资料下载

D_CAN USER MANUAL

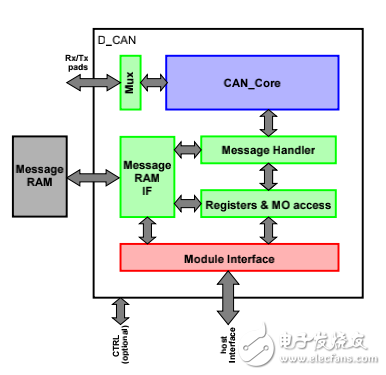

The D_CAN is a CAN IP module that can be integrated as stand-alone device or as part of

an SoC or ASIC. It is described in VHDL on RTL level, prepared for synthesis. It consists of

the components (see figure 1) Mux, CAN_Core, Message RAM interface, Message

Handler, Registers and Message Object (MO) access, Module Interface.

The D_CAN performs CAN protocol communication according to ISO 11898-1 (identical to

Bosch CAN protocol specification 2.0 A, B)。 The bit rate can be programmed to values up

to 1 MBit/s depending on the used technology. Additional transceiver hardware is required

for the connection to the physical layer (the CAN bus line)。

For communication on a CAN network, individual Message Objects are configured. The

Message Objects and Identifier Masks are stored in the Message RAM.

All functions concerning the handling of messages are implemented in the Message

Handler. Those functions are acceptance filtering, transfer of messages between the

CAN_Core and the Message RAM and the handling of transmission requests as well as the

generation of the module interrupt.

The register set of the D_CAN can be accessed directly by an external CPU via the module

host interface. These registers are used to control/configure the CAN_Core and the

Message Handler and to access the message RAM via the IF1 and IF2 register sets.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章