资料下载

×

达芬奇技术的数字视频系统设计与实现

消耗积分:0 |

格式:rar |

大小:0.21 MB |

2017-10-26

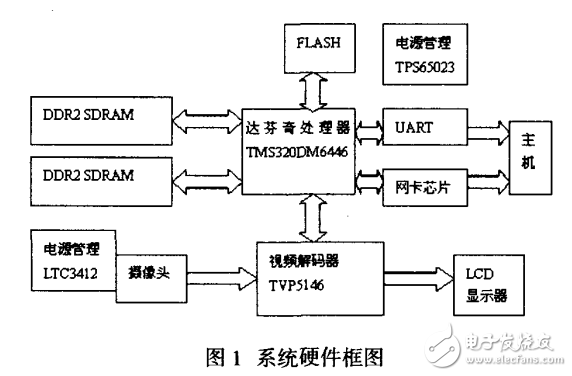

提供 了看 门狗 、中断控制器 、电源管理控制器 、复位控制器及 2个片上振荡器 。视频处理子系统(、,pss)有用 于视频输入的视频前端输入 rvPFF)接 口由 CCD控制器(CCDC),预处理器 、柱状模块 、自动曝光伯 平衡/聚焦模块(H3A)和寄存器组成;和用于视频输出的视频后端输出rvPBE)接 口由屏幕菜单式调节器(OSD)、视频编码器(VENC)和 四路 10bitDACs组成。1.2系统的硬件组成及工作原理整个数字视频系统采用 的是由达芬奇处理器(TMS320DM6446)、DDR2SDRAM、NAND FLASH、视 频解 码器 TVP5146、电源管理芯片 TPS65023,LTC3412加上外围接 口芯片 的方案。视频解码器把 CCD摄像头传过来的模拟视频信号进行模,数转换,变成符合 rru—BT.656标准的数字视频信号,然后将数字视频信号传到达芬奇处理器的视频处理子系统的前端进行预处理经过 CodecEngine编解码后送到视频处理子系统的后端,直接输出数字 视频信号 到显示终端上 或是通过 四路 54MHz的 DACs来提供 NTSC/PAL制式 的模拟视频输出。DM6446上 的 ARM端主要做为控制器来控制视频解码芯 片和外围接 口芯 片,DSP端主要负责视频编解码工作 。系统硬件框 图如图 1

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章