资料下载

×

NAND FLASH存储模块设计(XC3S1600E和NAND512W3A构成)

消耗积分:0 |

格式:rar |

大小:1.09 MB |

2017-10-31

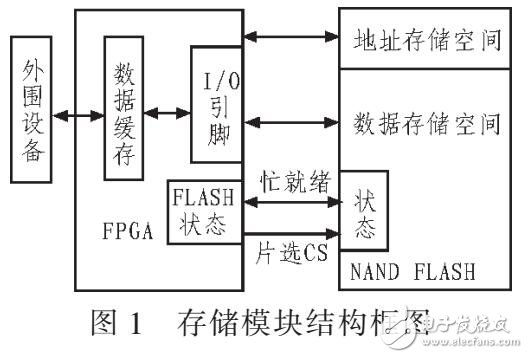

目前最新型的弹载黑匣子在实时性、大容量、高可靠性、高速率等方面又有了新的要求,炮弹弹道实验中姿态、轨迹、旋转速率等参数在被采集后需要及时存人存储模块中。传统的数据存储模块多用ARM作为其控制核心,但是由于ARM 的时钟频率较低且需用软件实现数据存储,这使得存储的速度和效率较低,在整个存储周期中大多为软件的运行时间。而FPGA 有ARM 无法比拟的优势,FPGA 时钟频率高、内部延时小,全部控制逻辑由硬件完成,速度快、效率高。在此技术基础上,为了满足数据存储对速度的要求,本文将介绍一种基于FPGA,采用VerilogHDL硬件描述语言设计实现的高速数据存储模块。存储芯片采用意法半导体公司的NAND512W3A,利用FPGA 构建读写FIFO 缓存、硬件擦除和读写以及坏块屏蔽NANDFLASH,从而加快了黑匣子数据存储的速度和可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章