d触发器的特性方程

电子常识

描述

D触发器(data flip-flop或delay flip-flop)由6个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器

SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

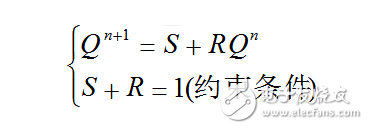

1、基本RS触发器(锁存器)

(1)特性方程

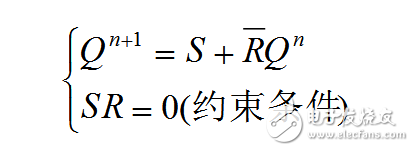

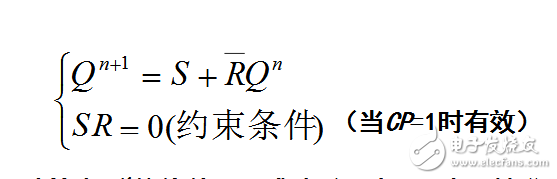

2、RS触发器

(1)特性方程

例2 同步RS触发器,设初始状态为0,已知输入R、S的波形图如图,画出输出Q的波形图。

解:将每个时段对应的R、S的波形高电平设为1低电平设为0,代入特性方程

计算出Qn+1的值并还原成波形。对于同步RS触发器要注意在CP信号时有效时输入端的波形会影响输出端得输出状态,在CP信号时无效时输入端的波形就不会影响输出端得输出状态此时触发器的状态不变。如:

在t1~t2时刻CP=1,此时触发器处于工作状态此时R=0,S=1,Qn=0,通过特性方程计算可知Qn+1=1高电平。

同理t2~t3时刻,触发器仍处于工作状态将输入信息和电路的原来状态带入公式计算得到Qn+1=0低电平。

在t3~t4时刻CP=0,电路处于非工作状态,因此触发器的状态不会随输入信号变化而变化,所以输出信号保持不变。

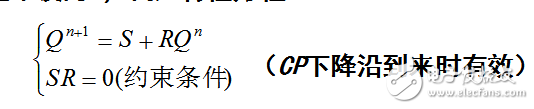

将每个有效时刻对应的R、S的波形高电平设为1低电平设为0,代入特性方程

计算出Qn+1的值并还原成波形。但在主从结构的触发器中电路发生变化的时间是某一个特定的时刻。

如:

在t1时刻主从RS触发器处于工作状态,R=1,S=0,Qn=0,代入特性方程得Qn+1=1高电平。在此时刻之后触发器不工作,触发器得状态保持不变,因此波形不变化。

同理触发器下一次工作是在t2时刻,将信号量和原状态代如公式得Qn+1=1。

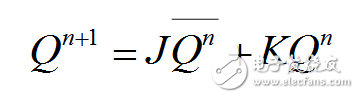

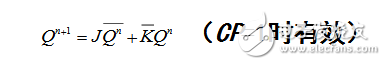

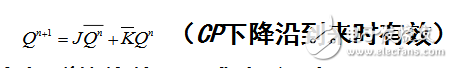

3、JK触发器

(1)特性方程

将每个时段对应的J、 K的波形高电平设为1低电平设为0,代入特性方程

计算出Qn+1

的值并还原成波形。如:

在t1~t2时刻CP=1,此时触发器处于工作状态此

时J=1,K=0,Qn=0,通过特性方程计算可知Qn+1=1高电平。

同理t2~t3时刻,触发器仍处于工作状态将输入信息和电路的原来状态J=0,K=0,Qn=1带入公式计算得到Qn+1=1高电平。

在t3~t4时刻CP=0,电路处于非工作状态,因此触发器的状态不会随输入信号变化而变化,所以输出信号保持不变。

将每个有效时刻对应的J、 K的波形高电平设为1低电平设为0,代入特性方程

计算出Qn+1的值并还原成波形。如:

在t1时此时触发器处于工作状态此时J=1,K=0,Qn=0,通过特性方程计算可知Qn+1=1高电平。在此时刻之后触发器不工作,触发器得状态保持不变,因此波形不变化。

同理触发器下一次工作是在t2时刻,将信号量和原状态代如公式得Qn+1=0。

-

时序逻辑电路的概述和触发器2018-08-23 0

-

关于D触发器的问题2019-01-16 0

-

施密特触发器有什么特性?2019-09-17 0

-

jk触发器设计d触发器2021-07-22 0

-

哪些触发器时钟有效哪些无效2021-09-06 0

-

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?2022-01-25 0

-

不同功能触发器的相互转换方法2010-09-30 1413

-

第十一讲 同步触发器2009-03-30 4001

-

主从rs触发器特性表及特性方程2018-02-08 50026

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 85475

-

基本rs触发器有哪三种功能 RS触发器的特征方程是什么2023-08-23 10776

-

jk触发器的特征方程怎么得到2024-01-17 656

-

四种触发器的状态方程 简述四种基本触发器及功能2024-02-06 1766

-

d触发器的功能 d触发器的状态方程2024-02-18 672

全部0条评论

快来发表一下你的评论吧 !