资料下载

×

基于Builder的正弦信号源优化设计

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-03

实现信号源常用的方法是频率合成法,其中直接数字频率合成法是继直接频率合成法和间接频率合成法之后,随着电子技术迅速发展的第三代频率合成技术。DDS是一种全数字技术,它从相位概念出发直接合成所需频率,它具有频率转换时间短,频率分辨率高,相位变化连续,低相位噪声和低漂移,易于集成、调整、实现正交输出等优点。近年来,DDS技术在频率合成、通信、雷达、电子对抗、仪器测试等领域均有广泛的应用。目前专用的DDS芯片产生的信号波形、功能和控制方式固定,常不能满足具体需要。现场可编程门阵列(FPGA)器件具有规模大、工作速度快及可编程的硬件特点,并且开发周期短,易于升级,因此非常适用于实现DDS。

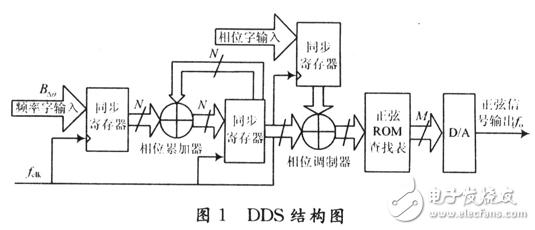

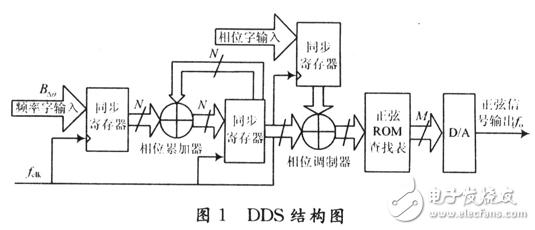

1 DDS的基本原理

DDS的结构由相位累加器,相位调制器,波形存储ROM和D/A转换器组成,是Tierney,Rader和Gold于1971年提出。一个正弦信号发成器结构图如图1所示。相位累加器是整个DDS的核心,完成相位累加运算,它输入的是相位增量B△θ。相位累加器每溢出一次,就代表输出ROM内的一个完整波形。相位调制器接收相位累加器的相位输出。加上一个相位偏移量,用于信号的相位调制。正弦ROM查找表完成相位到幅度的转换,它的输入是相位调制器的输出,也就是ROM的地址。

fo为输出频率,fo的值由fclk和B△θ共同决定:fo=fclk×B△θ/2N。根据Nyquist采样定律,最高的输出频率是时钟频率的一半,即fo=fclk/2。实际应用中,一般取fo≤40%fclk。DDS的频率分辨率△f用频率输入值步进一个最小间隔对应的频率输出变化量来衡量,即△f=fclk/2N(默认情况下,ROM存储整个周期信号波形)。可见,△f越小,DDS输出精度越高。

2 DDS精度改进方案

ROM查找表实际上是一个存储了正弦信号抽样点幅度编码的只读存储器,将输入的序列转换为正弦信号的幅度编码。ROM查找表地址位数M越靠近相位累加器的位数N,相位寻址时舍去的位数就越小,相位舍位误差也就越小,但ROM表的大小会随地址位数M的增加成指数递增关系。因此,为了使用较小的ROM而满足信号性能,必须采用优化方法压缩ROM。

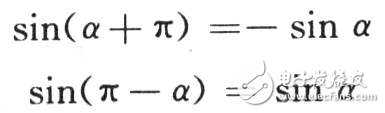

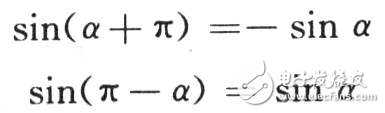

2.1 正弦波特点

已知正弦波存在下面的关系:

可见,[π,2π]区间的波形可以通过[0,π]区间波形转化得到。进一步,由于[O,π/2]和[π/2,π]区间波形关于α=π/2对称,则[π/2,π],[π,3π/2],[3π/2,2π]三个区间波形都可以通过[0,π/2]区间的波形转化得到。

2.2 基于DSP Builder的ROM优化方案

从上面对正弦波特点的分析可得出,查找表ROM中只存储[O,π]或[0,π/2]区间的波形就可得完整周期的正弦信号。这样就有效地利用了ROM存储完间,提高了存储效率。对于ROM中存储[O,π]区间波形的情况,可以利用相位调制器输出的最高位作为符号位,将正弦波合成到[0,2π]区间。而对于ROM中存储[0,π/2]区间波形的情形,利用相位调制器输出的次高位判断象限,将正弦波合成到[O,π]区间;最高位作为符号位,将正弦波合成到[0,2π]区间。图2给出了ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型。

1 DDS的基本原理

DDS的结构由相位累加器,相位调制器,波形存储ROM和D/A转换器组成,是Tierney,Rader和Gold于1971年提出。一个正弦信号发成器结构图如图1所示。相位累加器是整个DDS的核心,完成相位累加运算,它输入的是相位增量B△θ。相位累加器每溢出一次,就代表输出ROM内的一个完整波形。相位调制器接收相位累加器的相位输出。加上一个相位偏移量,用于信号的相位调制。正弦ROM查找表完成相位到幅度的转换,它的输入是相位调制器的输出,也就是ROM的地址。

fo为输出频率,fo的值由fclk和B△θ共同决定:fo=fclk×B△θ/2N。根据Nyquist采样定律,最高的输出频率是时钟频率的一半,即fo=fclk/2。实际应用中,一般取fo≤40%fclk。DDS的频率分辨率△f用频率输入值步进一个最小间隔对应的频率输出变化量来衡量,即△f=fclk/2N(默认情况下,ROM存储整个周期信号波形)。可见,△f越小,DDS输出精度越高。

2 DDS精度改进方案

ROM查找表实际上是一个存储了正弦信号抽样点幅度编码的只读存储器,将输入的序列转换为正弦信号的幅度编码。ROM查找表地址位数M越靠近相位累加器的位数N,相位寻址时舍去的位数就越小,相位舍位误差也就越小,但ROM表的大小会随地址位数M的增加成指数递增关系。因此,为了使用较小的ROM而满足信号性能,必须采用优化方法压缩ROM。

2.1 正弦波特点

已知正弦波存在下面的关系:

可见,[π,2π]区间的波形可以通过[0,π]区间波形转化得到。进一步,由于[O,π/2]和[π/2,π]区间波形关于α=π/2对称,则[π/2,π],[π,3π/2],[3π/2,2π]三个区间波形都可以通过[0,π/2]区间的波形转化得到。

2.2 基于DSP Builder的ROM优化方案

从上面对正弦波特点的分析可得出,查找表ROM中只存储[O,π]或[0,π/2]区间的波形就可得完整周期的正弦信号。这样就有效地利用了ROM存储完间,提高了存储效率。对于ROM中存储[O,π]区间波形的情况,可以利用相位调制器输出的最高位作为符号位,将正弦波合成到[0,2π]区间。而对于ROM中存储[0,π/2]区间波形的情形,利用相位调制器输出的次高位判断象限,将正弦波合成到[O,π]区间;最高位作为符号位,将正弦波合成到[0,2π]区间。图2给出了ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章