资料下载

×

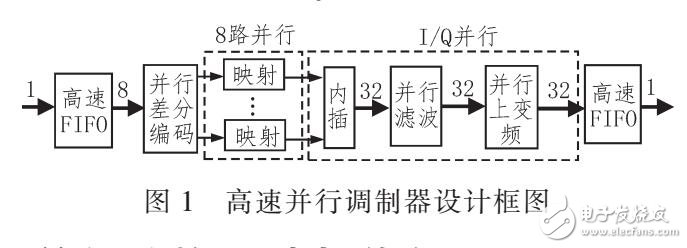

一种高速并行调制器的设计方案

消耗积分:0 |

格式:rar |

大小:0.72 MB |

2017-11-03

随着信息技术和通信技术的发展,人们对信息传输速率的要求越来越高,如对高清电视、视频会议等服务的需求日益高涨,从而对调制解调这一制约传输速率的环节提出了更高的速率要求。传统的高速调制解调器多为高速模拟调制解调器。随着数字芯片处理速度的不断提高,可靠性更高、灵活性更大的高速数字调制解调器得到了越来越广泛的应用。

而高速数字调制解调器的速率仍会受限于其所采用的数字信号处理芯片的最高处理速度。在诸多数字芯片中,FPCA的处理速度最快,常用于高速信号处理领域。而FPCA的处理速率主要受限于其主时钟频率。若采用传统的串行调制技术就难以突破主时钟频率对调制速率的限制。若想进一步提高调制速率,就必须先将高速数据分流到各个支路以降低速率,其后采用并行结构进行处理。

文中对差分编码、成形滤波等各个调制步骤的并行处理算法进行了研究,将这些模块转化为并行结构,从而在时钟频率受限的情况下提高了处理速率,并对这些结构进行了深度优化,以减少资源消耗,便于FPGA实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章