nmos高端驱动自举电路

场效应管

描述

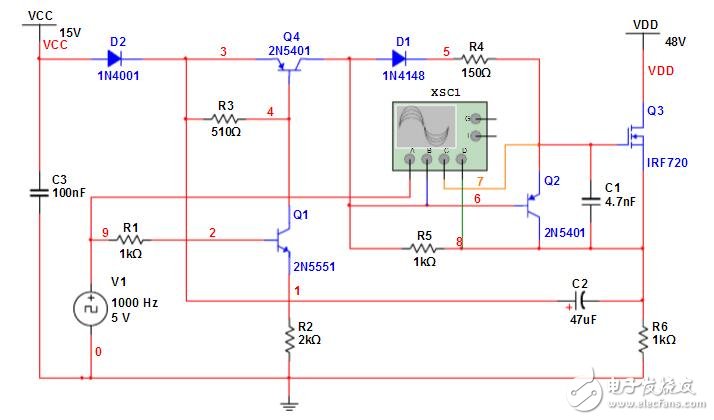

一、电容自举驱动NMOS电路

VCC经过二极管D2、电容C2、电阻R1到地,所以加载在电容C2两端的电压约为14V。

图1电容自举驱动NMOS电路

(1) 当V1输入高电平时,Q1、Q4导通,B通道输出高电平,Q2截止,C通道输出高电平,Q3导通,D通道输出高电平48V,由于C2两端电压14V,所以Q3的导通使电容抬升了VDD的电压,即电容C2的正极电压位62V左右,经过三极管Q4、二极管D1到达Q3的栅极,电容C2起到了自举抬升电压的作用,使Q3持续导通。

(2) 当V1输入低电平时,Q1、Q4截止,B通道输出低电平,Q2导通,Q2的导通为Q3的栅极提供放电电路(栅极电压通过Q2、电阻R1放电),使得电容C2的负极电压接近0V,即D通道输出低电平。

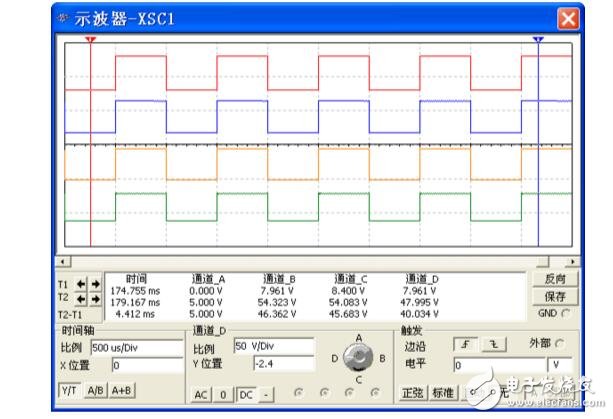

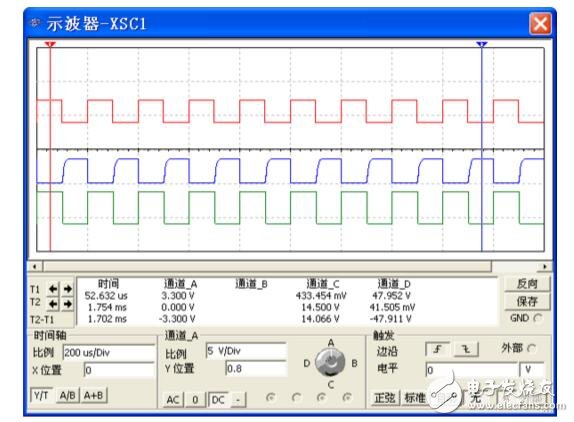

图2 电容自举驱动NMOS电路仿真

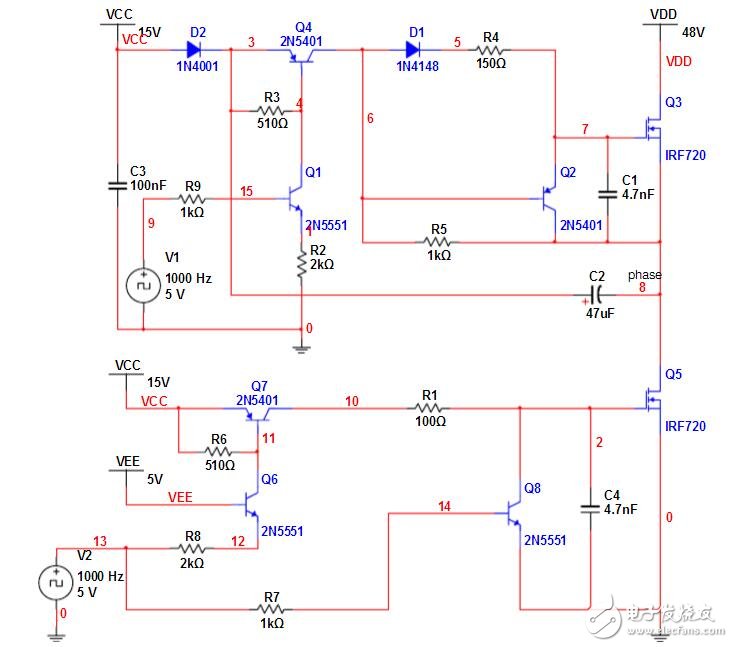

二、MOSFET驱动电路

图3 MOSFET驱动电路

(1) 当V1=V2=5V时,Q1、Q4导通,Q2截止,VCC经过D2、Q4、D1、R4到达Q3的栅极,Q3导通;Q6、Q7截止,Q8导通,Q8的导通为Q5的栅极提供放电回路,Q5截止;

(2) 当V1=V2=0V时,Q1、Q4截止,Q2导通,Q2的导通为Q3的栅极提供放电回路放电电流经过Q2、Q5到地;Q6、Q7导通,Q8截止,VCC经过Q7、电阻R1到达Q5的栅极,Q5导通。

实际应用中,保持V1、V2同相可以避免上下管同时导通。

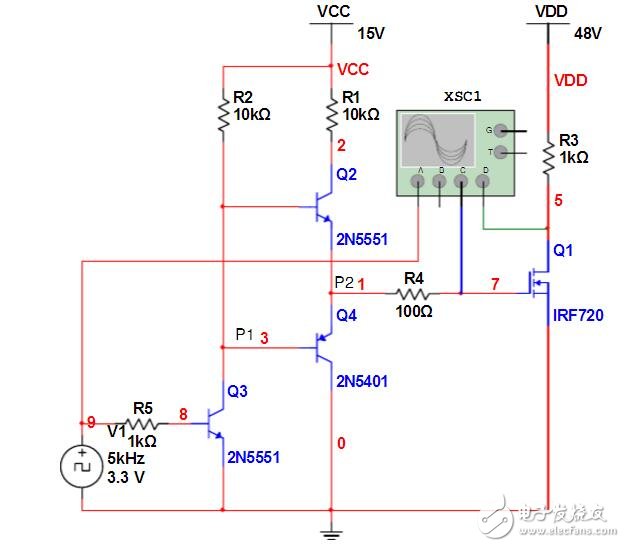

三、推挽驱动NMOS电路

图4推挽驱动NMOS电路

(1) 当V1=3.3V时,Q3导通,P1为低电平,使得Q2截止、Q4导通,Q4的导通为Q1的栅极提供放电回路,P2为低电平,Q1截止。

(2) 当V1=0V时,Q3截止,电阻R2将P1钳位在高电平,使得Q2导通、Q4截止,Q2的导通为Q1的栅极提供充电电路,P2为高电平,Q1导通。

图5 推挽驱动NMOS电路仿真

-

关于IR2104搭建的驱动电路的几个问题2018-04-20 0

-

请问如何用NMOS管设计高端输出电路?2019-02-19 0

-

关于NMOS高端输出的设计问题2019-02-28 0

-

NMOS与PMOS的驱动电路有什么区别?2021-07-30 0

-

NMOS驱动电路的特性有哪些呢2021-11-03 0

-

NMOS、PMOS驱动负载优缺点2023-02-03 0

-

MPS | DCDC 高端 NMOS 的自举秘诀2023-05-22 0

-

驱动半桥自举电路2010-01-04 9990

-

NMOS驱动电路2012-04-01 9110

-

自举供电驱动电路设计-魏巍2016-05-11 677

-

利用MOSFET管自举升压驱动电路2016-12-16 1400

-

高压栅极驱动器自举电路设计2021-06-19 1221

-

开关电源中同步开关对管中高端E-NMOS的自举驱动分析2021-10-21 528

-

自举电路工作原理是什么2024-02-16 1402

全部0条评论

快来发表一下你的评论吧 !