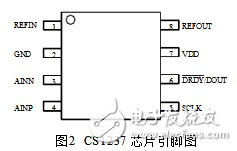

CS1237引脚图及功能

AC-DC/DC-DC转换

描述

CS1237是一款高精度、低功耗模数转换芯片,一路差分输入通道,内置温度传感器和高精度振荡器。

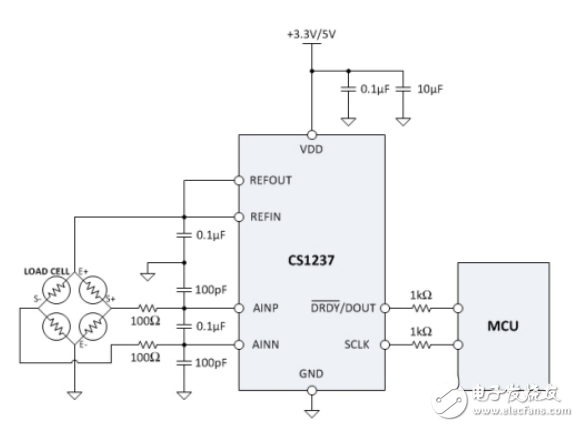

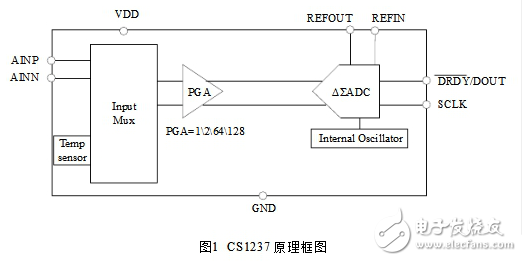

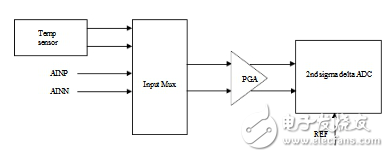

以下为CS1237芯片的功能框图。

1、芯片功能说明

1) CS1237 是一款高精度、低功耗模数转换芯片,一路差分输入通道,内置温度传感器和高精度振荡器。

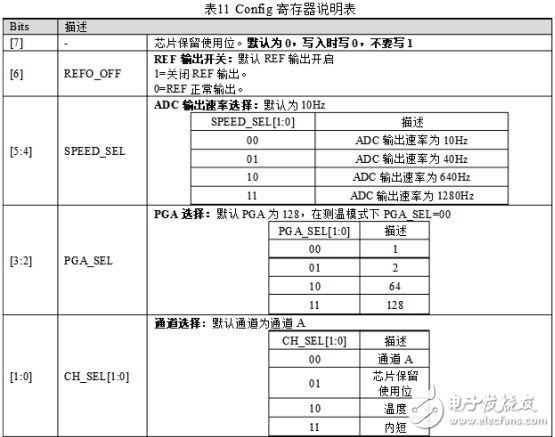

2) CS1237的PGA可选: 1、2、64、128,默认为128。

3) CS1237 正常模式下的ADC 数据输出速率可选: 10HZ、40Hz\ 640Hz\ 1.28kHz,默认为10Hz;

4) MCU 可以通过2 线的SPI接口SCLK、DRDY DOUT与CS1237 进行通信,对其进行配置,例如通道选择、PGA选择、输出速率选择等。

1.1芯片主要功能特性

1)内置晶振

2)集成温度传感器

3)带Power down功能

4)2线SPI接口,最快速率为1.1MHZ

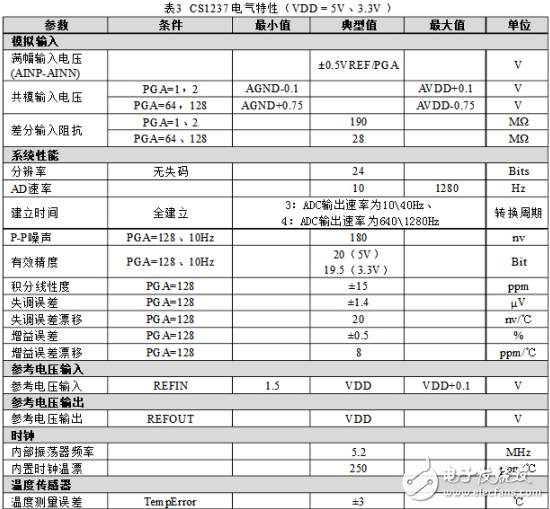

1.2ADC 功能特性

24 位无失码

PGA放大倍数可选: 1、2、64、128

1路24位无失码的差分输入,在PGA=128时ENOB为20位(5V)\19.5位(3.3V)

PP噪声:PGA=128、10HZ:180nV;

INL小于0.0015%

输出速率可选: 10HZ、40HZ、640Hz、1.28kHz

带内短功能

1.3芯片基本结构功能描述

CS1237是一款高精度、低功耗Sigma-Delta 模数转换芯片,内置一路Sigma-De1taADC,一路差分输入通道和一路温度传感器,ADC 采用两阶sigm a delta 调制器,通过低噪声仪用放大器结构实现PGA放大,放大倍数可选: 1、2、64、128。在PGA=128时,有效分辨率可达20 位(工作在5V)。

CS1237 内置RC 振荡器,无需外置晶振。

CS1237 可以通过DRDY,DOUT和SCIK 进行多种功能模式的配置,例如用作温度检测、PGA选择、ADC 数据输出速率选择等等。

CS1237 具有Powerdown模式。

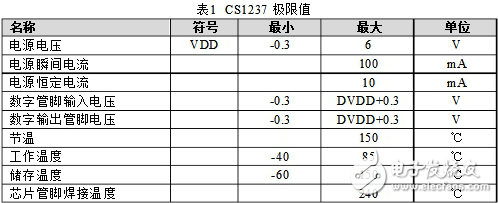

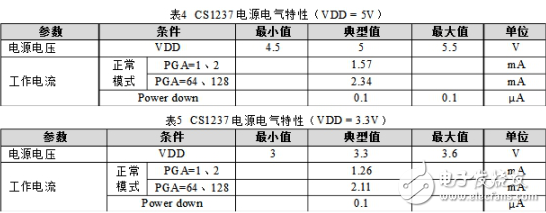

1.6 CS1237电气特性

所有的参数测试在环境温度-40~85℃、内置基准的条件下测试,除非有其它注明。

1.7芯片引脚

2.1模拟输入前端

CS1237 中有1路ADC,集成了1路差分输入,信号输入可以是差分输入信号AINP、AINN,也可以是温度传感器的输出信号,输入信号的切换由寄存器(ch_se[1:0])控制,其基本结构如下图所示:

图3 模拟输入结构图

CS1237 的PGA可配: 1、2、64、128,由寄存器(ga_sl[1:0])控制;

基准电压可以由外部输入也可是内部输出,如果要使用外部基准电压,要先关闭内部

基准,内部基准控制由寄存器(refo_off控制。

2.2温度传感器

芯片内部提供温度测里功能。当ah_se1[1:0]=2‘b10时,ADC模拟信号输入接到内部温度传感器,其它的模拟输入信号无效。ADC 通过测里内部温度传感器输出的电压差来推导出实际的温度值。当ch_se[10]=2b10时,ADC 只支持PGA=1。温度传感器需要进行单点校正。校正方法: 在某个温度点A下,使用温度传感器进行测里得到码值Yao

那么其他温度点B 对应的温度= Yb+(273.15+A)Ya-273.15

A温度单位是摄氏度。Ya 是A点对应温度码值。Yb是B点对应温度码值。

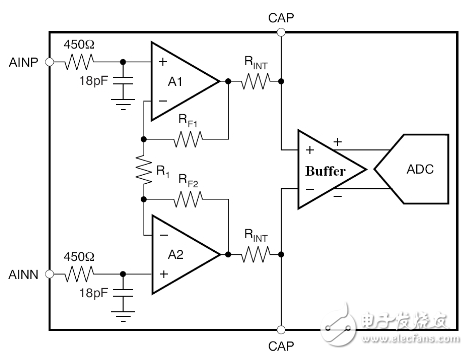

2.3低噪声PGA 放大器

CS1237 提供了一个低噪声,低漂移的PGA 放大器与桥式传感器差分输出连接,其基

本结构图如下图所示,前置抗EMI 滤波器电路R=4502,C=18pF 实现20M高频滤波。低

噪声PGA放大器通过RF1; R1; RF2 实现64倍放大,并和后级开关电容PGA组成64 和

128 的PGA 放大。通过pga_sel[1:0]来配置1\ 2、64\ 128 等不同的PGA。当使用PGA=1,2时,64 倍低噪声PGA放大器会被关断以节省功耗。当使用低噪声PGA放大器时,输入范围在GND+0.75V 到VDD_0.75V 之间,超出这个范围,会导致实际性能下降。在CAP端口处接一个内置45PF电容,与内置2k电阻RINT组成一个低通滤波,用作低噪声PGA放大器的输出信号的高频滤波,同时该低通滤波器也可以作为ADC 的抗混叠滤波器。

图4 PGA结构图

CS1237 内置Buffer,当PGA=1,2时,CS1237 使用Buffer来减少由于ADC差分输入阻抗低带来的问题,例如建立时间不足,增益误差偏大等等,当PGA=64 ,128 时,CS1237 也使用Buffer 来减少由于低噪声PGA经过RINT=2K,CNT=0.1uF的低通滤波后带来的建立误差,增益误差以及内码漂移的现象。

2.4时钟信号源

CS1237 使用内置晶振来提供系统所需要的时钟频率,典型值为5.2MHZO

2.5复位和断电( POR& power down )

当芯片上电时,内置上电复位电路会产生复位信号,使芯片自动复位。

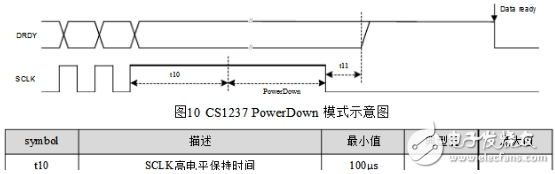

当SCLK 从低电平变高电平并保持在高电平超过100us,CS1237 即进入PowerDwon

模式,此时功耗低于0.1UAO 当SCLK 重新回到低电平时,芯片会重新进入正常工作状态。

当系统由Power down 重新进入正常工作模式时,此时所有功能配置为PowerDown 之前的状态,不需要进行功能配置。

基于CS1237的电子秤应用设计http://bbs.elecfans.com/forum.php?mod=viewthread&tid=927715&page=1

2.6SPI 串口通信

CS1237 中采用2 线SPI 串行通信,通过SCLK 和DRDY.DOUT可以实现数据的接收以及功能配置。

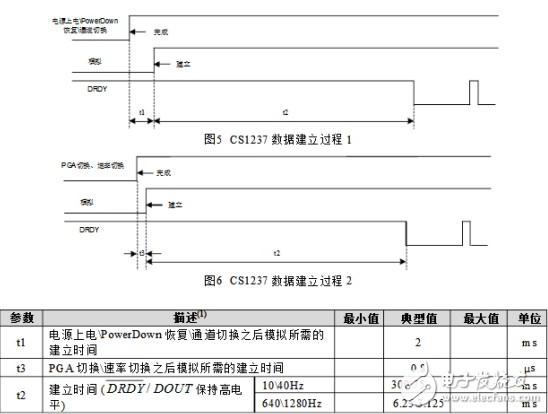

2.6.1建立时间

在ADC 数据输出速率为10HZ 或40HZ 时,数字部分需要有3个数据转换周期满足模拟输入信号的建立和滤波器的建立时间要求; ADC 数据输出速率为640HZ 或1280HZ 时,数字部分需要有4个数据转换周期满足模拟输入信号的建立和滤波器的建立时间要求。CS1237 整个建立过程如下图所示:

2.6.2ADC数据输出速率

CS1237数据输出速率可以通过寄存器speed_sel[1:0]配置。

2.6.3数据格式

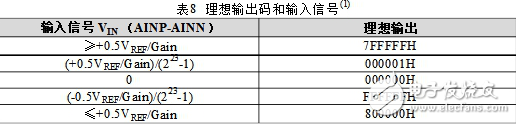

CS1237 输出的数据为24 位的2 进制补码,最高位(MSB) 最先输出。最小有效位(LSB) 为(0 5VR=/Gain)(2Z-1)o 正值满幅输出码为TFFFFH,负值满幅输出码为800000H。下表为不同模拟输入信号对应的理想输出码。

(1) 不考虑噪声,INL,失调误差和增益误差的影响

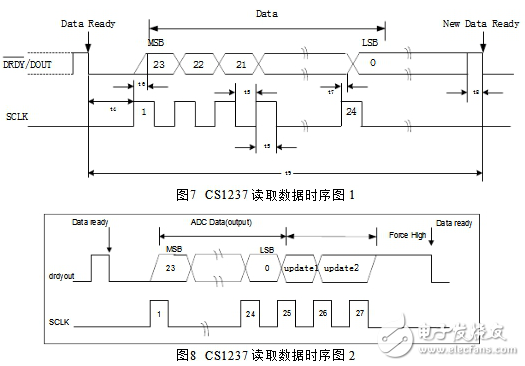

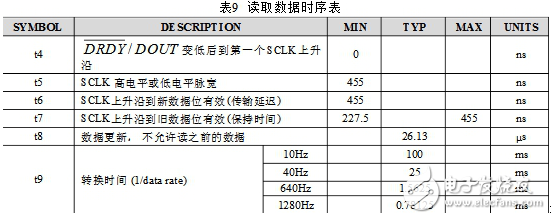

2.6.4数据准备数据输入输出(DRDY.DOUT)

DRDY/DOUT引脚有4个用途。第一,当输出为低时,表示新的数据已经转换完成; 第二,作为数据输出引脚,当数据准备好后,在第1个SCIK的上升沿后,

输出转换数据的最高位(MSB)。在每一个SCLK的上升沿,数据会自动移1位。在24个SCLK 后将所有的24位数据读出,如果这时暂停SCLK的发送,着最后一位的数据,直到下一个数据准备好之前拉高,此后当DRDY.DOUT被再: 欠拉

低,表示新的数据已经转换完成,可进行下一个数据读取; 第三,在第25、26 个SCIK时,输出寄存器状态更新标志; 第四,作为寄存器数据写入或读出引脚,当需要配置寄存器或读取寄存器值时,SPI需要发送46个SCLK,根据DRDY DOUT输入的命令字,判断是写寄存器操作还是读寄存器操作。

2.6.5串行时钟输入(SCLK)

串行时钟输入SCLK是一个数字引脚。这个信号应保证是一个干净的信号,毛刺或慢速的上升沿都会可能导致读取错误数据或误入错误状态。因此,应保证SCLK的上升和下降时间都小于50ns。

2.6.6数据发送

CS1237 可以持续的转换模拟输入信号,当将DRDY /DOUT拉低后,表明数据已经准备好接受,输入的第一个SCLK 来就可以将输出的最高位读出,在24个SCLK 后将所有的24 位数据读出,如果这时暂停SCLK 的发送,DRDY/DOUT 会保持着最后一位的数据,直到其被拉高,第25 和26个SCLK 输出配置寄存器是否有写操作标志,第25个SCLK 对应的DRDY/DOUT为1时表明配置寄存器Config 被写入了新的值,第26个SCIK 对应的DRDY/DOUT为芯片扩展保留位,目前输出一直为0,通过第27个SCLK可以将DRDY DOUT拉高,此后当DRDY.DOUT被再次拉低,表示新的数据已经淮备好接受,进行下一个数据的转换。其基本时序如图所示:

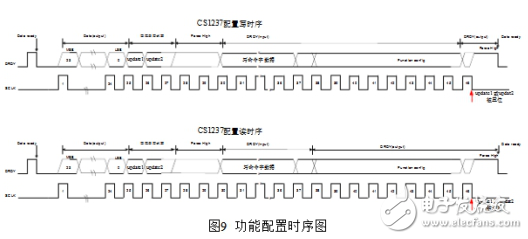

2.6.7功能配置

Cs1237可以通过SCLK和DOUT/DRDY可以进行不同功能的配置,功能配置时序图如下图所示:

功能配置过程简述,在DRDY,DOUT由高变低之后:

1.第1个到第24个SCLK,读取ADC 数据。如果不需要配置寄存器或者读取寄存器,可以省略下面的步骤。

2.第25 个到第26个scLK,读取寄存器写操作状态。

3.第27 个SCLK,把DRDY,’DOUT输出拉高。

4.第28 个到第29个scLK,切换DRDY ‘DOUT为输入。

5.第30 个到第36个sCLK,输入寄存器写或读命令字数据(高位先输入)。

切换DRDY/DOUT的方向(如果是写寄存器,

6.第37 个SCLK,

DRDY/DOUT为输入; 如果是读寄存器,

DRDY/DOUT 为输出)。

7.第38 个到第45 个SCLK,输入寄存器配置数据或输出寄存器配置数据(高位先输入/输出)。

8.第46 个SCLK,切换DRDY/DOUT为输出,并把DRDY/DOUT拉高.update1/ update2 被置位或清零。

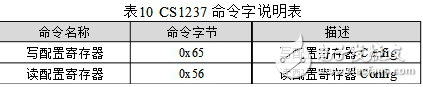

2.6.7.1SPI 命令字

CS1237 有2个命令字,命令字的长度为7bits,命令字描述如下:

2.6.7.2SPI寄存器

Cs1237有一组寄存器Config

Config寄存器

2.6.8 PowerDwon模式

当SCLK从低电平变高电平并保持在高电平超过100µs,CS1237即进入PowerDwon模式,这时会关掉芯片所有电路,功耗接近0。当SCLK重新回到低电平时,芯片会重新进入正常工作状态。

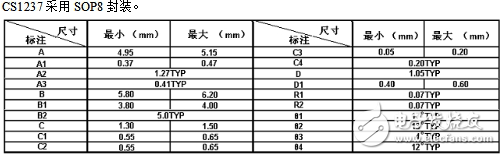

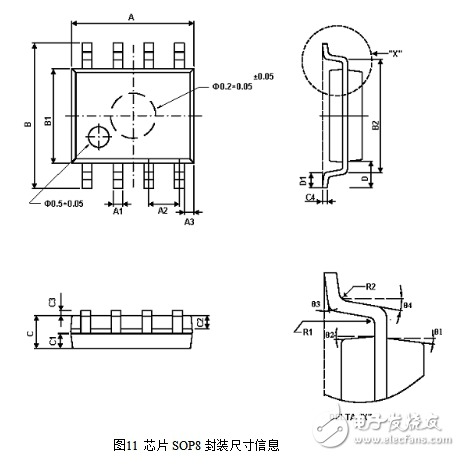

3 芯片的封装

-

CS1237/CS1238 系列问题集2024-03-27 0

-

CS1237/CS1239 问题集2024-03-27 0

-

基于CS1237的电子秤应用设计2016-08-15 0

-

提供CS1237芯片 深圳鼎盛合科技代理芯海CS1237芯片2020-06-11 0

-

CS1237要多次写入配置才能有效2020-11-09 0

-

CS1237无法正常写配置问题,附时序图2020-11-27 0

-

CS1237驱动程序2021-08-10 0

-

cs12372021-08-16 0

-

cs1237时序问题2021-08-23 0

-

CS1237 内短功能 是什么意思?2021-12-06 0

-

CS1180和CS1237低温表现不同2022-09-08 0

-

cs1237的ardunio的驱动程序2023-08-24 0

-

CS1237驱动程序参考代码2017-11-06 11393

-

cs1237配置不成功2023-12-29 453

-

CS1237 用户手册2024-04-21 84

全部0条评论

快来发表一下你的评论吧 !