资料下载

×

等价型PG逻辑在加法器设计中的应用分析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-06

引言

在全加器设计中运用PG逻辑是非常普遍的,本文在设计和研究全加器时,根据现有的PG逻辑公式推导出了一种新的逻辑公式,并论证了两者之间的等价关系。这一新的公式能够指导全加器设计中的连线方式,灵活更改连线策略。本文将从基本原理开始逐步引出该公式,对其进行论证,并应用于全加器设计中。

全加器设计的

基本原理

N位全加器将{AN,……,A1}、{BN,……,B1}和进位输入Cin作为输入,计算得到和{SN,……,S1}以及最高位的进位输出Cout(见图1)。每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。最终,整个全加器的和与输出都受进位输入Cin的影响。

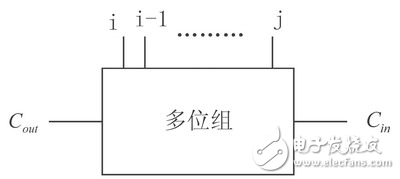

图1 N位全加器

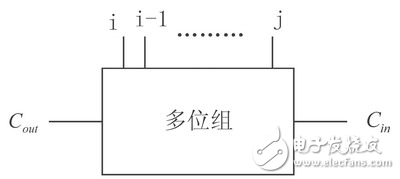

图2 多位组传播Cin 或者直接产生进位输出

全加器最简单的构成方法就是把每一位的进位输出与下一位的进位输入简单地连接起来,得到的就是行波进位全加器。但在快速全加器中,是将加数和被加数中具有相同下标的位分成若干组,即多个多位组,并将各个多位组看作一个整体。通过计算多位组的PG逻辑,在求和之前可预测多位组的进位输出是传播进位输入还是直接产生进位输出。多位组所包括的位在i到j的范围内(见图2),如果该多位组的进位输出是与进位输入无关的“真”值,那么它就产生了一个进位;如果该多位组的进位输出只有当进位输入为“真”时才进位输出“真”值,那么它就传播了一个进位。对于i≥k≥j,这些信号能够递归地定义为:

Gi:j=Gi:k+Pi:kGk-1:j;Pi:j=Pi:kPk-1:j

其中 Gi:i≡Gi=AiBi;Pi:i≡Pi=Aii;定义 G0:0=Cin;P0:0=0

在全加器设计中运用PG逻辑是非常普遍的,本文在设计和研究全加器时,根据现有的PG逻辑公式推导出了一种新的逻辑公式,并论证了两者之间的等价关系。这一新的公式能够指导全加器设计中的连线方式,灵活更改连线策略。本文将从基本原理开始逐步引出该公式,对其进行论证,并应用于全加器设计中。

全加器设计的

基本原理

N位全加器将{AN,……,A1}、{BN,……,B1}和进位输入Cin作为输入,计算得到和{SN,……,S1}以及最高位的进位输出Cout(见图1)。每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。最终,整个全加器的和与输出都受进位输入Cin的影响。

图1 N位全加器

图2 多位组传播Cin 或者直接产生进位输出

全加器最简单的构成方法就是把每一位的进位输出与下一位的进位输入简单地连接起来,得到的就是行波进位全加器。但在快速全加器中,是将加数和被加数中具有相同下标的位分成若干组,即多个多位组,并将各个多位组看作一个整体。通过计算多位组的PG逻辑,在求和之前可预测多位组的进位输出是传播进位输入还是直接产生进位输出。多位组所包括的位在i到j的范围内(见图2),如果该多位组的进位输出是与进位输入无关的“真”值,那么它就产生了一个进位;如果该多位组的进位输出只有当进位输入为“真”时才进位输出“真”值,那么它就传播了一个进位。对于i≥k≥j,这些信号能够递归地定义为:

Gi:j=Gi:k+Pi:kGk-1:j;Pi:j=Pi:kPk-1:j

其中 Gi:i≡Gi=AiBi;Pi:i≡Pi=Aii;定义 G0:0=Cin;P0:0=0

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章