资料下载

×

基于FPGA的异构可重配置DSP平台

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-06

视频、影像和电信市场的标准推动了异构可重配置DSP硬件平台的使用。在本文中这些平台包括DSP处理器和FPGA,它们提供的现成硬件解决方案可以解决视频、影像和电信设计中的重大难题,同时又不失差异化设计所需的足够的可定制性。

市场研究公司Forward Concepts 2005年发表的一则调查报告称,选择处理器和FPGA的主要标准不是器件本身,而是开发它们的工具。这一概念对于包含FPGA和DSP处理器的平台亦应成立。

在DSP处理器和FPGA之间,传统的DSP开发者通常选择前者,因为设计流程是已知的,而异构系统的优势则难于评价。可重新配置的硬件平台限制了硬件自由度,设计流程因此而具有较高的自动化程度。这种自动化消除了设计的复杂性,从而在DSP设计界进一步推广了硬件解决方案的优势。

DSP硬件平台的优点

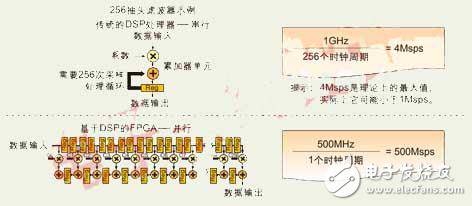

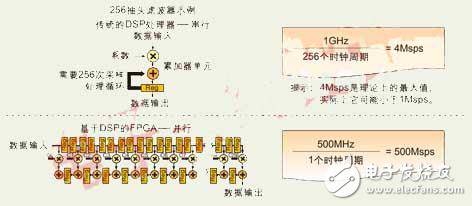

FPGA和DSP处理器具有截然不同的架构。在一种器件上非常有效的算法,放在另一种器件上却可能效率非常低。如果目标应用要求大量的并行处理或最大的多通道流量,那么单纯基于DSP处理器的硬件系统就可能需要更大的面积、成本或功耗。一个FPGA协处理器仅在一个器件上就能提供多达550个并行乘法和累加运算,从而以较少的器件和较低的功耗为许多应用提供同样的性能(如图1所示)。

图1:基于FPGA的DSP。

尽管FPGA在处理大量并行数据方面出类拔萃,但对于定期系数更新、决策控制任务或高速串行数学运算这类任务来说,它们的优化程度比不上处理器。此时FPGA和DSP处理器的结合为许多应用提供了制胜的解决方案。

例如,对于采用模式识别技术的智能摄像机来说,异构可重配置DSP平台就是理想的选择。FPGA的并行处理能力非常适用于图像分割和特征提取,而视频和影像DSP处理器则更适合统计模式分类等数学密集型任务。异构系统可以更好地利用流水线和并行处理,这对于获得高帧速率和低延迟来说至关重要。

基于异构平台的设计流程的优点

基于异构平台的设计流程把单独处理器和FPGA设计流程采用的设计自动化概念扩展到整个平台。基于平台设计的基本原则是剔除基于硬件系统和基于软件系统的“中间件”。这样就可以让缺乏或完全没有FPGA设计经验的DSP设计者能够评估和利用FPGA协处理器的性能、成本和功耗优势。

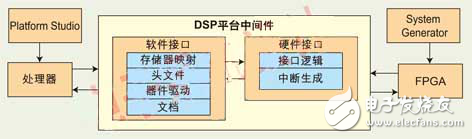

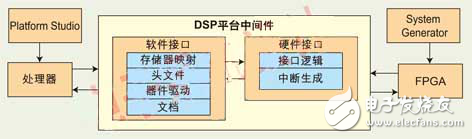

基于平台的设计流程应能自动生成内存映射、软件接口的头文件和驱动程序文件以及硬件的接口和中断逻辑。整体系统的改动对单个软件和硬件组件的影响有限(见图2)。通过这种自动化,开发者个人不必再掌握设计FPGA硬件、DSP处理器应用代码以及接口逻辑和软件所需的庞杂技术。

图2:软硬件接口生成

设计FPGA协处理器

任何给定的技术中都有多种方法可以实现信号处理算法。算法步骤常常受到目标硬件的影响。当目标是异构DSP硬件平台时,需要分两步选择实现方法。你必须首先选择最合适的硬件器件,然后再确定哪种实现方法适合该器件。

在可重新配置的DSP硬件平台上,处理器将作为主处理单元并且控制FPGA。而FPGA则用作协处理器(数据传入DSP处理器进行同步,然后传出),或者用作预处理器或后处理器(数据从高速接口传入)。FPGA的最佳用法取决于系统数据速率、格式和运行参数。

像德州仪器公司的DSP工具包Code Composer Studio就含代码分析器,用来识别可以下载到FPGA的软件“热点”。20%应用代码占用80%可用处理器MIPS的情况并不罕见。

在将FPGA与硬件平台上独立的DSP处理器连接时需要一个接口。可重新配置的DSP平台通常能支持较多通用接口(如德州仪器公司的16/32/64位Tic6x DSP扩展存储器接口,适用于系统控制和协处理任务)和较多高速串行接口(如SRIO或视频接口,用于预处理和后处理操作)。

系统中加入FPGA协处理器后,软件实现就将由算法描述转变为数据传递与函数控制。对于应用软件开发者来说,FPGA协处理器将显示为一个硬件加速器,可以通过函数调用对其进行访问。

市场研究公司Forward Concepts 2005年发表的一则调查报告称,选择处理器和FPGA的主要标准不是器件本身,而是开发它们的工具。这一概念对于包含FPGA和DSP处理器的平台亦应成立。

在DSP处理器和FPGA之间,传统的DSP开发者通常选择前者,因为设计流程是已知的,而异构系统的优势则难于评价。可重新配置的硬件平台限制了硬件自由度,设计流程因此而具有较高的自动化程度。这种自动化消除了设计的复杂性,从而在DSP设计界进一步推广了硬件解决方案的优势。

DSP硬件平台的优点

FPGA和DSP处理器具有截然不同的架构。在一种器件上非常有效的算法,放在另一种器件上却可能效率非常低。如果目标应用要求大量的并行处理或最大的多通道流量,那么单纯基于DSP处理器的硬件系统就可能需要更大的面积、成本或功耗。一个FPGA协处理器仅在一个器件上就能提供多达550个并行乘法和累加运算,从而以较少的器件和较低的功耗为许多应用提供同样的性能(如图1所示)。

图1:基于FPGA的DSP。

尽管FPGA在处理大量并行数据方面出类拔萃,但对于定期系数更新、决策控制任务或高速串行数学运算这类任务来说,它们的优化程度比不上处理器。此时FPGA和DSP处理器的结合为许多应用提供了制胜的解决方案。

例如,对于采用模式识别技术的智能摄像机来说,异构可重配置DSP平台就是理想的选择。FPGA的并行处理能力非常适用于图像分割和特征提取,而视频和影像DSP处理器则更适合统计模式分类等数学密集型任务。异构系统可以更好地利用流水线和并行处理,这对于获得高帧速率和低延迟来说至关重要。

基于异构平台的设计流程的优点

基于异构平台的设计流程把单独处理器和FPGA设计流程采用的设计自动化概念扩展到整个平台。基于平台设计的基本原则是剔除基于硬件系统和基于软件系统的“中间件”。这样就可以让缺乏或完全没有FPGA设计经验的DSP设计者能够评估和利用FPGA协处理器的性能、成本和功耗优势。

基于平台的设计流程应能自动生成内存映射、软件接口的头文件和驱动程序文件以及硬件的接口和中断逻辑。整体系统的改动对单个软件和硬件组件的影响有限(见图2)。通过这种自动化,开发者个人不必再掌握设计FPGA硬件、DSP处理器应用代码以及接口逻辑和软件所需的庞杂技术。

图2:软硬件接口生成

设计FPGA协处理器

任何给定的技术中都有多种方法可以实现信号处理算法。算法步骤常常受到目标硬件的影响。当目标是异构DSP硬件平台时,需要分两步选择实现方法。你必须首先选择最合适的硬件器件,然后再确定哪种实现方法适合该器件。

在可重新配置的DSP硬件平台上,处理器将作为主处理单元并且控制FPGA。而FPGA则用作协处理器(数据传入DSP处理器进行同步,然后传出),或者用作预处理器或后处理器(数据从高速接口传入)。FPGA的最佳用法取决于系统数据速率、格式和运行参数。

像德州仪器公司的DSP工具包Code Composer Studio就含代码分析器,用来识别可以下载到FPGA的软件“热点”。20%应用代码占用80%可用处理器MIPS的情况并不罕见。

在将FPGA与硬件平台上独立的DSP处理器连接时需要一个接口。可重新配置的DSP平台通常能支持较多通用接口(如德州仪器公司的16/32/64位Tic6x DSP扩展存储器接口,适用于系统控制和协处理任务)和较多高速串行接口(如SRIO或视频接口,用于预处理和后处理操作)。

系统中加入FPGA协处理器后,软件实现就将由算法描述转变为数据传递与函数控制。对于应用软件开发者来说,FPGA协处理器将显示为一个硬件加速器,可以通过函数调用对其进行访问。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章