资料下载

×

基于PCB信号完整性的反射设计

消耗积分:0 |

格式:rar |

大小:1.45 MB |

2017-11-09

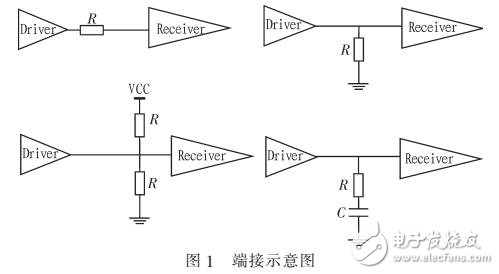

随着半导体工艺的进步,晶体管特征尺寸将持续减小,因而信号的上升边必然持续减小且时钟频率也必然持续提高。相应的时钟频率的不断提高则又促进了上升边的不断下降,因此也就引发了愈发严重的信号完整性问题,在高速数字系统中,对于频率达到百兆甚至CHz以上的信号,会由于系统的信号完整性的问题而导致信号质量不佳。甚至对于不到50 MHz的信号,由于其电平跳变时间在Ins甚至ps级,最终PCB产品中依然有可能会m现信号完整性问题。

为了缩短开发周期提高效率,在高速PCB设计过程中可以借助有效的仿真工具对关键信号网络进行仿真以辅助设计。在本设计中将使用Cadenc:e Allegro软件平台下的Allegro PCB Sl GXL、Allegro PCB PI op工ion XL及SigXplorer相关仿真组件来对系统单一网络的信号质量,信号间串扰及电源完整性等问题进行仿真来支持叠层设置、布局布线等规则的选择,以此对高速DA/AD电路系统提供硬件设计技术支持。根据仿真的结果确定电路的最终方案,优化了PCB设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章