并行总线是什么?(并行总线协议介绍)

接口/总线/驱动

描述

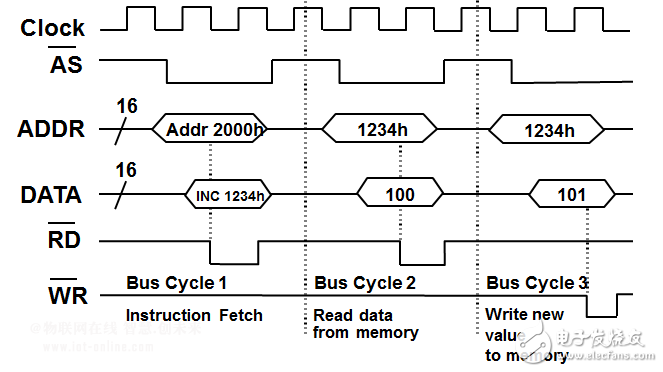

并行总线,就是并行接口与计算机设备之间传递数据的通道。采用并行传送方式在 微型计算机与外部设备之间进行数据传送的接口叫并行接口,它有2个主要特点;一是同时并行传送的二进位数就是数据宽度;二是在计算机与外设之间采用应答式的联络信号来协调双方的数据传送操作,这种联络信号又称为握手信号。

1、简单的并行接口 简单的并行接口分0线握手并行接口、1线握手并行接口和2线握手并行接口等多种。

1)0线握手并行接口所谓0线握手(连络),即接口电路中不含协调数据传送的连络信号,这是并行接口的最简形式,它又分输入并行接口和输出并行接口以及输入/输出双向并行接口 3种形式。 0线握手 输入接口 在输入量比较稳定的情况下(输入的状态信息在一个的时间内不改变,如开关量输入),可采用三态门直接读取。 0线握手输出接口 当输出数字量无需锁存时,可采用三态门直接输出。 0线双向输入/输出接口当外设与CPU之间需要利用 数据总线进行双向传送信息时,I/O设备即能发送信息,又能接收信息。

2)1线握手并行接口 1线握手并行接口是在0线握手并行接口的基础上,增加了一条握手信号线。 1线握手方式总是假设发送方式所发送的数据已经就绪,接收方可以接收。

2、可编程并行接口 可编程并行接口芯片种类较多,Intel公司的8255A(PPI),Motorola公司的MC6820(PIA)和Zilog公司的Z80-PIO 都属于这一类器件。

3、并行总线的最大好处是总线的逻辑时序比较简单,电路实现起来比较容易,但是缺点也是非常明显的。比如并行总线的信号线数量非常多,会占用大量的管脚和布线空间,因此芯片和PCB板的尺寸很难实现小型化,特别是如果要用电缆进行远距离传输时,由于信号线的数量非常多,使得电缆变得非常昂贵和笨重。

采用并行总线的另外一个问题在于总线的吞吐量很难持续提升。对于并行总线来说,其总线吞吐量=数据线位数×数据速率。我们可以通过提升数据线的位数来提高总线吞吐量,也可以通过提升数据速率来提高总线吞吐量。以个人计算机里曾经非常流行的PCI总线为例,其最早推出时总线是32位的数据线,工作时钟频率是33MHz,其总线吞吐量=32bit×33MHz;后来为了提升其总线吞吐量推出的PCI-X总线,把总线宽度扩展到64位,工作时钟频率最高提升到133MHz,其总线吞吐量=64bit×133MHz。下图是PCI插槽和PCI-X插槽的一个对比,可以看到PCI-X由于使用了更多的数据线,其插槽更长。

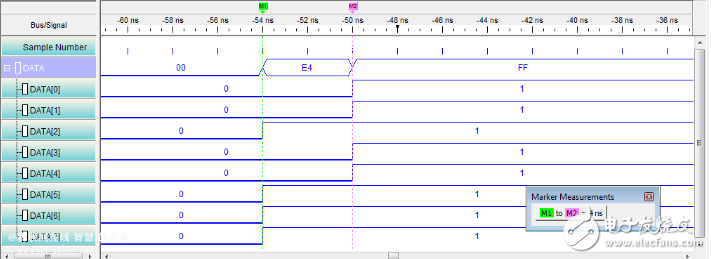

但是随着人们对于总线吞吐量的要求的不断提高,这种提升总线带宽的方式遇到了瓶颈。首先由于芯片尺寸和布线空间的限制,64位数据宽度已经几乎是极限了。另外一方面,这64根数据线是共用一个采样时钟,为了保证所有的信号都满足其建立保持时间的要求,在PCB上布线、换层、拐弯时需要保证精确等长。而总线工作速率越高,对于各条线的等长要求就越高,对于这么多根信号要实现等长的布线是很难做到的。

下图是用逻辑分析仪采集到的一个实际的8位总线的工作时序,我们可以看到在数据从0x00跳变到0xFF状态过程中,这8根线实际并不是精确一起跳变的。

-

高速并行总线的工作原理是什么 高速并行总线有哪些2024-10-06 2212

-

并行总线和串行总线的区别2023-12-07 5650

-

基于FPGA的ARM并行总线设计原理2023-10-10 370

-

高速PCB并行总线和串行总线2022-12-29 2592

-

高速串行总线与并行总线的差别是什么?2021-05-12 1448

-

并行总线和高速串行总线的布线要求2020-10-21 5845

-

什么是基于FPGA的ARM并行总线?2019-09-17 2084

-

关于并行总线波形捕获与分析的视频介绍2018-06-25 4184

-

并行总线有哪些?串行总线有哪些?2017-11-13 86067

-

基于FPGA和多DSP的多总线并行处理器设计2017-10-19 913

-

基于FPGA的ARM并行总线研究与仿真2017-01-24 987

-

基于FPGA的ARM并行总线设计与仿真分析2013-08-15 9103

-

PCA9564 并行总线转I2C总线接口芯片简介2010-03-10 1548

全部0条评论

快来发表一下你的评论吧 !