资料下载

×

在星载设备上通信的收发器IP核方案

消耗积分:0 |

格式:rar |

大小:1.15 MB |

2017-11-14

传统卫星星载设备使用并行传输结构提高数据传输速率,随着星载设备数据处理能力的提高,继续采用并行传输的方式提高速率将引入一些问题。一是在接收端对多路并行数据的同步将变的困难。二是卫星内部数据传输线的过多会增加卫星重量,增加卫星发射成本。日前市面上的主流工业级FPGA芯片都集成各自开发的高速串行收发器,能达到很高的数据传输速率,但是卫星上使用的宇航级FPGA芯片中,却少有集成高速串行收发器,在国防军事卫星上使用国外厂商的黑盒IP核对于整个卫星系统的可靠性控制会产生不可预测的风险。

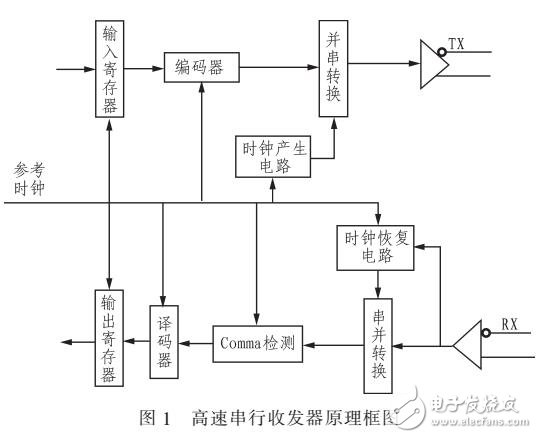

文中通过对现有的各主流厂商的FPGA集成的高速串行收发器不同方案的分析,提出一种能够在FPGA设计中方便调用的高速串行收发器IP核,该IP核具有8BIOB编解码,时钟数据恢复等功能,具有实现资源消耗少,速度快,移植性好,可靠性高等特点。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章