UltraScale– UltraScale FPGA中IODelay相比7Series FPGA的改变

FPGA/ASIC技术

描述

IODelay是Xilinx FPGA IO结构内,一个很有用处的单元,至少从Spartan6/Virtex5时代开始,就已经集成了这一技术,在很多高速接口互联时,我们都可能找到IODelay的用武之地。在最新的Ultrascale系列FPGA中,IODelay这一单元的具体用法,跟7Series中相比产生了一些变化。本文总结下,供读者参考。

1. 7Series FPGA中IODelay的用法

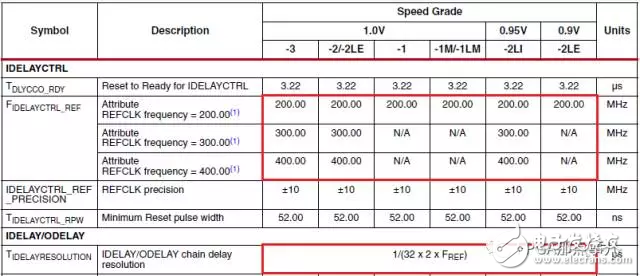

在7Series中,IODelay都需要配合IOdelayCtrl来使用。其延迟步进阶数总共为64个Taps,每个Tap精度是tREFCLK/64。REFCLK提供3种设置,分别是200Mhz,300Mhz,和400Mhz,所以相对应的延迟精度分别为:5ns/64=78ps,3.333ns/64=52ps,2.5ns/64=39ps。

2.在Ultrascale FPGA中

相比7Series,最大的区别是,IODelayCtrl补偿时,针对的是整个delayline,而不是单个的delay tap element。

IODelay提供了2种使用模式供用户选择,分别是TIME Mode和COUNT Mode

在TIME Mode中,延迟是加入了温度补偿的,因此延迟值比较精确。在COUNT Mode中,不配合使用IDelayCtrl,每个TAP的延迟值在2.5ps-15ps之间随机不固定。一般我们都会使用TIME Mode,因此重点说下这个Mode的使用方法。

在TIME Mode下,我们可以在IP配置初始时指定延迟的具体数值,单位是ps,范围是0-1250ps。这种模式对应的DELAY_TYPE属性是FIXED。

如果在TIME Mode下,我们想动态的调整IODELAY的延迟值该怎么办呢?方法如下,首先需要把DELAY_TYPE属性配置成VARIABLE或者VAR_LOAD,然后遵循以下步骤:

①. Deassert (Low) the EN_VTC pin.

②. Wait a minimum of 10 clock cycles.

③. Use the CE and INC ports to increment or decrement the delay line.

④. Wait a minimum of 5 clock cycles.

⑤. (Option for multiple updates) Increment or decrement of the delayline needs to be performed. Go to step 3, or else proceed to step 6.

⑥. Wait a minimum of 10 clock cycles.

⑦. Assert the EN_VTC pin.

- 相关推荐

- FPGA

-

Xilinx UltraScale 系列发布常见问题汇总2013-12-17 0

-

XilinxVirtex®UltrascaleFPGA多路千兆位收发器MGT电源解决方案2015-05-11 0

-

用于Xilinx Ultrascale Kintex FPGA多路千兆位收发器(MGT)的电源解决方案2018-08-10 0

-

12V输入的Xilinx Virtex Ultrascale FPGA电源参考设计2018-08-29 0

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案包括BOM及原理图2018-08-29 0

-

Xilinx Ultrascale 16nm FPGA/SoC电源解决方案2018-11-19 0

-

是否有推荐的PROM与Ultrascale FPGA一起使用?2019-03-14 0

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案2022-09-21 0

-

基于20nm工艺制程的FPGA—UltraScale介绍2023-03-09 4468

-

使用UltraScale和UltraScale+FPGA开发防篡改设计2023-09-13 84

-

UltraScale和UltraScale+ FPGA封装和管脚用户指南2023-09-13 191

-

AMD推出全新Spartan UltraScale+ FPGA系列2024-03-18 73

全部0条评论

快来发表一下你的评论吧 !