总线之RS-485的工业应用

接口/总线/驱动

描述

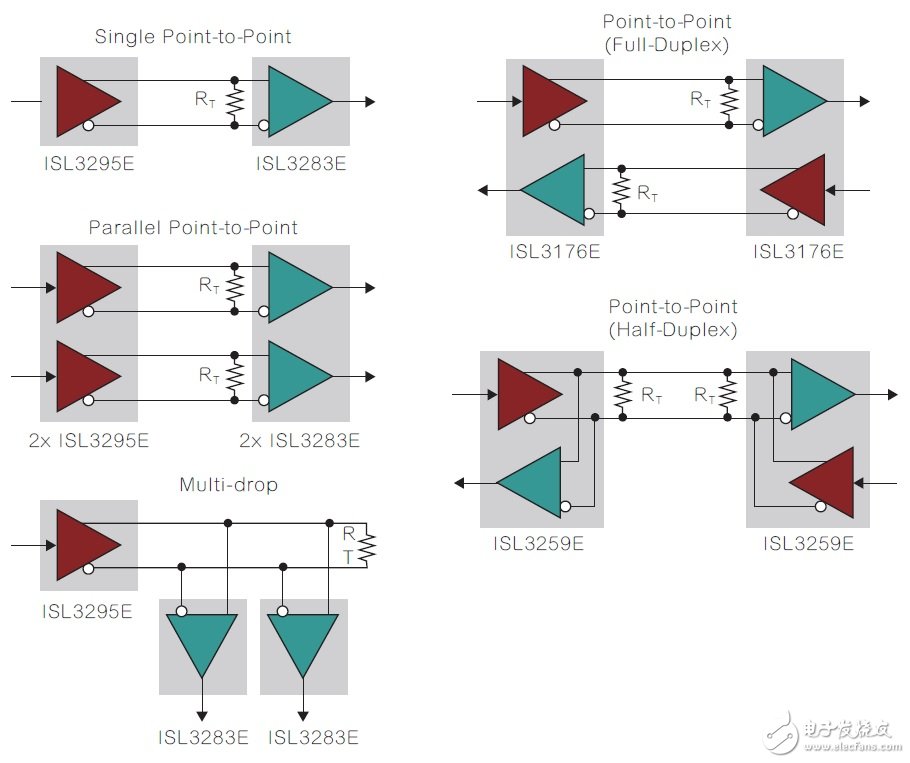

RS-485是用于许多工业通讯系统(如PROFIBUS系统),或者用于PLC等连接组件、SCADA系统、RTU或MODBUS系统的物理层(PHY)标准。如图1所示,高速和超高速RS-485数据链路通常采用相对简单的配置,如单个或并行点对点(全双工或半双工)、或多点(multi-drop)结构。

图1 高速RS-485链路的典型配置。

这些简单的图表隐含了许多设计考虑事项,如收发器选择、每个节点的电路板布局、缆线选择和互连几何形状(interconnect geometry)等。为满足最终用户对更高数据速率和更长缆线的要求,并确保将可识别数据误差降到最低,必须对所有这些方面予以考虑和优化。本文讨论了在高速数据传输中工程师应当考虑的关键设计事项,并透过一个总线节点设计示例提供一般设计指导原则和布线建议。

讯号劣化显示为讯号抖动(jitter),是限制实际缆线长度的主要因素。这种讯号抖动是驱动器和接收器脉冲偏移和模式相关缆线偏移(pattern-dependent cable skew)的结果。驱动器和接收器脉冲偏差是驱动器和接收器的上升和下降边缘(edge)的传播延迟之差。

位模式相关的缆线偏移是总线讯号上升和下降时间的变量,这是由不同位序列(bit sequence)造成。数据脉冲对位模式相关偏移的反应是振幅损失、圆化边缘、时间位移和在相邻位间隔产生脉冲「拖尾(smearing)」。

使用数据编码方法(例如Manchester、8b/10b或33hex)有助于减轻抖动。对数据流进行编码会在数据流中引入转变,从而使缆线电容充电和放电更均衡,并产生更一致的讯号振幅。但是,数据编码可以缩短缆线电容的充电和放电时间,从而缩小总线讯号振幅。

收发器选择

为向接收器提供可靠的输入讯号,建议使用具有较大差分输出电压(VOD)和较低偏移的高速收发器。大VOD可克服缆线衰减、数据编码和共模负载造成的讯号振幅减小,并确保远程接收器输入端有足够的噪声容限。

对于低电压设计,应当注意所谓的「经济实惠型」3V收发器的输出等级,只能在电源电压高于4V时提供符合RS-485标准的输出电压。在较低电源轨情况下,晶体管效率会大幅下降,使VOD比RS-485标准要求的1.5V最小值还要低40%,如此低的输出电压不能产生足够的噪声容限来触发远程接收器。

具有非常高输出驱动能力的Intersil高速收发器系列的最低VOD范围为1.5V最小值的160%(4.5V电源电压)至100%(3.0V电源电压),从而提供真正的3V RS-485驱动能力。在最高工作温度下测得的典型VOD电压在3V收发器情况下超出RS-485标准27%,5V收发器情况下超出70%~93%。

此外,小脉冲偏移可以将收发器在数据链路总抖动预算中所占的比例降到最低。所有Intersil高速收发器的最大脉冲偏移均为1.5ns。而且,不同零件的偏移(在同步应用中也需要重点考虑)小于4ns。

总线节点设计

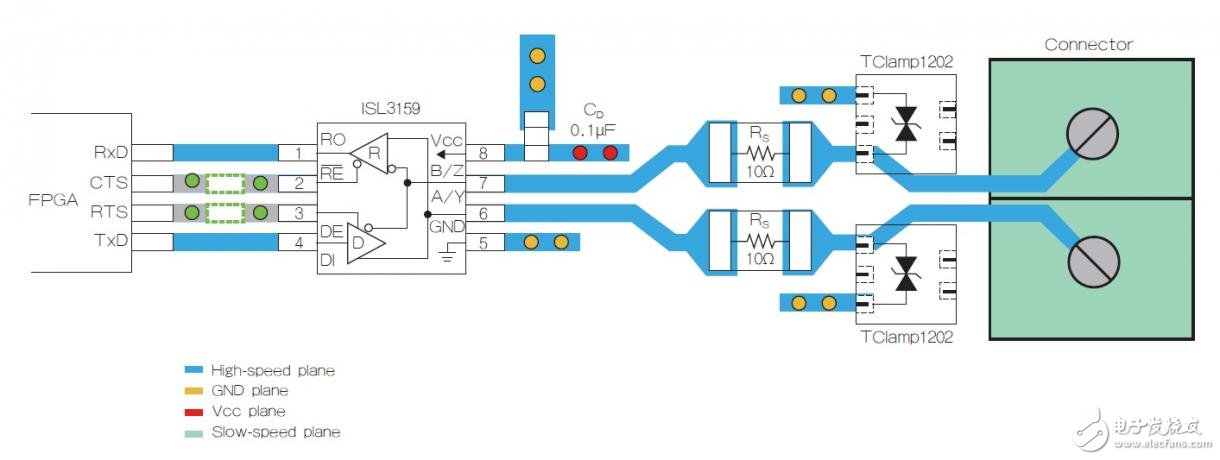

图2显示的总线节点包含收发器、基于FPGA的控制器、防浪涌电阻和用于避雷的瞬态抑制器。收发器引出线将总线端子(A/Y、B/Z)放在IC的一侧,将单端数据线(DI、RO)和控制线(DE、/RE)放在另一侧,从而简化设计。

图2 主要组件和互连。

为了将电磁干扰(EMI)降到最低,必须部署可控阻抗传输线。在总线侧,总线迹线(trace)的差分阻抗必须与传输媒介的特性阻抗(100Ω或120Ω)匹配。在控制侧,单端迹线的线路阻抗通常设置为50Ω。

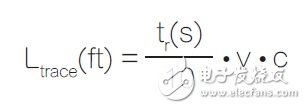

在由收发器和控制器组成的简单总线节点中,通过谨慎选择迹线长度、宽度、高度和间距,以及透过与低电感参考面(接地层或电源层)的紧密电耦合,可相对容易地实现可控阻抗传输线。必须计算控制器和收发器连接迹线,以及收发器和电缆连接器间的差分讯号迹线的长度。在每个连接的情况下,电气(electrical)长度应比驱动器输出上升时间的1/10要短,该关系可表示如下:

其中: Ltrace是迹线长度(英尺) tr是驱动器上升时间(秒) v=讯号速度(光速的百分比) c=光速(9.8×108英尺/秒)

对于接地层上方的紧邻单端线路,例如推荐用于连接控制器与收发器的线路,相对讯号速度为56%。使用2ns ISL3159E上升时间可以计算出迹线长度最大为33mm。

收发器至电缆连接器的迹线长度可按照标准FR4衬底上迹线的相对讯号速度(亦即40%)来计算。在此情况下,计算得出的最大迹线长度为24mm。

图2所示的避雷组件会使设计变得复杂。可以使用Field Solver软件工具准确计算需要的迹线几何尺寸。该软件可计算特性阻抗、讯号速度、串扰和差分阻抗,并允许用户评估几乎任意几何形状。除了考虑第一级的项目,例如线宽、介电层厚度和介电常数,还可以考虑第二级的项目,如迹线厚度、阻焊层和迹线回蚀。

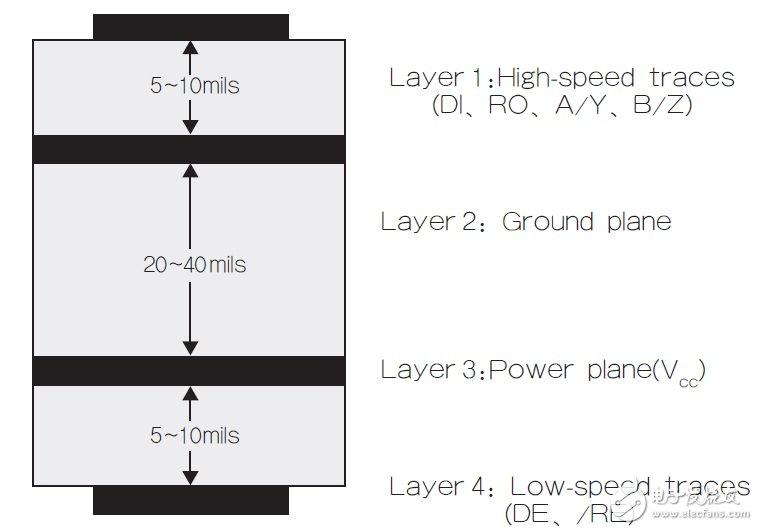

在PCB设计方面,为了将电磁干扰降到最低,至少需要采用四层。这些层应以图3所示顺序层迭,顶层为高速讯号层,然后是接地层和电源层,底层是控制讯号层。

图3 建议的4层PCB结构。

将高速迹线布置于顶层的方案,有助于避免与添加通孔(vias)有关的额外复杂性和电感,同时使得从总线连接器到收发器总线端子,以及从收发器的高速单端数据线到节点控制器的互连更加整洁。

将固体(solid)接地层放在高速讯号层下面可建立传输线互连所需的可控阻抗,并为返回电流提供低电感路径。将电源层放在接地层下可产生额外的高频旁路电容。

将速度较低的控制(启用)讯号放在底层可提供更大的灵活性。这些讯号链路通常具有针对间断点(如通孔)的容限,而且这种分隔几乎消除了来自高速数据迹线的串扰。

应遵循的六项一般指导原则: ˙使用尽可能小的讯号迹线通孔和连接器焊盘,将其对差分阻抗的影响降到最低; ˙使用固体电源层和接地层,以控制阻抗,并将收发器电源线路上的噪声降到最低; ˙使RS-485连接器和收发器之间的迹线电长度尽可能短,将衰减和反射降到最小; ˙将大电容(如10μF)放在接近电源(如稳压器)的位置,或者放在为PCB供电的位置; ˙将0.1μF和0.01μF去耦合电容放在收发器VCC接脚位置,以便为需要大电流来进行内部开关的IC提供局部电荷源; ˙如果需要通孔,可在连接Vcc、GND、去耦电容和TVS二极管至高速IC时使用多个通孔。

此外,以下关于缆线选择、总线端接和管理短线的建议有助于从系统角度完成设计。

传输缆线

RS-485标准建议使用标称特性阻抗Z0=120Ω非屏蔽双绞线(UTP)。通常使用的缆线为Z0=120Ω的专用单对RS-485缆线,或具有四个讯号对和Z0=100Ω的五类线。

当在单对应用中使用CAT-5缆线时,应当在线缆两端使用RT=100Ω的电阻对三个未使用的讯号对正确接地,这可防止来自未使用导线的噪声进入数据对。

请注意,在选择CAT-5缆线以外的多对缆线时,不能使用所谓的「无偏移缆线」,这种线是专为具有较低或零谐波含量的模拟讯号而设计。对数据讯号使用这种缆线会导致较大的串扰和数据误差。

总线端接

因为RS-485标准允许使用两个终端电阻(termination resistor),所以高速数据线始终应在数据链路的两端使用终端电阻RT。RT的值当与缆线的特性阻抗Z0或电路板上的可控阻抗传输线的阻抗匹配RT=Z0=100Ω。

存根(stub)长度

收发器与主数据缆线之间的连接(称为存根)无需使其终止,以避免总线超载。另一方面,存根长度应尽可能短,以防止形成讯号反射。菊链(Daisy-chaining)缆线连接方法可以有效地减少从收发器到连接器的存根长度至PCB迹线长度,这可以使用上面的简单公式,或使用用于节点设计的Field-Solver软件来计算。

总结

在电路板和系统层面运用合理的设计原则,并使用在3.3V和5V电源下均提供高输出驱动能力和最小偏移的收发器,可帮助设计工程师克服RS-485高速通讯链路的讯号劣化问题。

-

RS-485总线在工业设计中的应用介绍2009-09-04 0

-

RS-485总线介绍2021-07-16 0

-

RS-485的相关资料分享2022-02-09 0

-

防止RS-485总线出现致命瞬态波形的参考设计2022-09-15 0

-

3个理由了解为什么CAN总线与RS-485更好2023-04-03 0

-

RS-485总线电路中的过热保护2010-12-16 775

-

RS-485总线的理论与实践2006-03-13 1083

-

CAN总线与RS-485总线的通信接口设计2010-01-27 4243

-

RS-485总线标准及几种常见的RS-485接口电路介绍2015-12-21 1661

-

RS-485总线芯片的选型_应用及注意事项2018-04-18 21117

-

RS-485总线技术的基础知识2020-07-23 1770

-

rs422总线RS-485总线和RS-232-C的区别介绍2020-10-16 3391

-

深度解读RS-485总线2021-06-16 11234

-

RS-485 总线是要距离还是要速度?2022-11-07 321

全部0条评论

快来发表一下你的评论吧 !