对DDR3读写状态机进行设计与优化并对DDR3利用率进行了测试与分析

设计测试

描述

摘要:为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该设计满足大容量数据缓存要求,并具有较强的可移植性。

随着宽带雷达技术的发展,超高速和宽带采样已成为基本要求[1],超高速采集系统需要相匹配的数据缓存设计,DDR3 SDRAM是当前最常用的高效方案[2-4]。

DDR SDRAM是同步动态随机存储器,其采用双倍速率存取,数据在工作时钟的上升沿和下降沿采样,有效提升了存储速率。DDR SDRAM系列存储设备经历了DDR、DDR2和DDR3几个阶段。DDR3 SDRAM在降低系统功耗的同时提高了系统性能,其利用“FlyBy”和动态片上匹配技术对于信号完整性的改善效果明显[5]。本文基于Xilinx的MIG_v1.91 IP核进行了DDR3 SDRAM控制器的编写,并在Kintex-7 FPGA芯片上完成了功能测试及实现。

1 DDR3连续读写操作的FPGA 实现

设计选用8片Mircon公司型号为 MT42J128M16的芯片作为缓存区。每片芯片的数据位宽为8bit,行地址复用14条地址线,列地址复用10条地址线,共有8个Bank。每片容量为128MB,8片DDR3共同组成位宽为64bit,容量为1GB的缓存区域[6]。

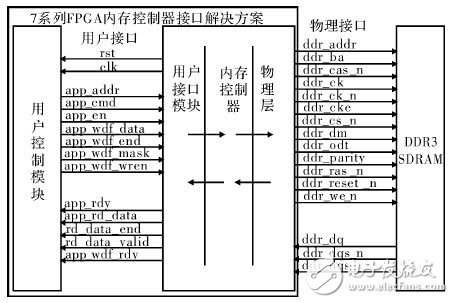

本文中DDR3控制器是基于Xilinx MIG IP核设计的。用户首先需要在MIG IP核配置页面对DDR3芯片型号、总线位宽、速度等级、引脚分配等参数进行设置。设置完成后即可得到DDR3控制器接口解决方案,Xilinx Kintex-7系列FPGA内存接口解决方案如图1所示[7]。

该方案由用户控制模块、用户接口模块、内存控制模块和物理层接口模块4部分组成。用户接口模块位于设计的最前端,通过呈现一个扁平化的地址空间和缓冲器,提供了一个简单的用户接口,用以代替本地接口进行数据的读写操作。内存控制模块位于用户接口模块和物理层模块之间,其前端为用户接口模块提供本地接口。本地接口支持用户设计提交存储器读写请求,并提供用户设计模块与外部存储设备之间的数据传输机制。内存控制模块还提供了一个具有重排序的功能选项,可以对接收到的请求进行重新排序,进而优化数据传输的吞吐量及时延。内存控制器后端连接至物理层接口,并处理所有该模块的接口请求。物理层接口前端连接至内存控制器模块,后端连接外部存储设备,其主要功能是捕获DDR3发出的数据,产生DDR3所需要的控制指令信号,并通过输入输出缓存发送所有DDR3的控制信号、地址信号以及数据信号,同时保证指令与地址、数据的同步和信号的维持[5]。

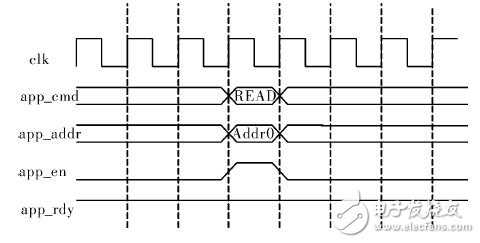

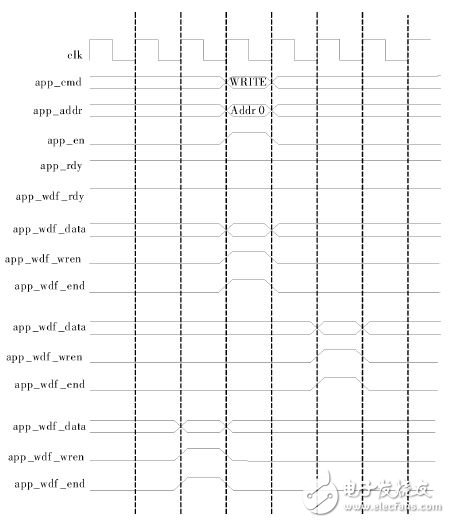

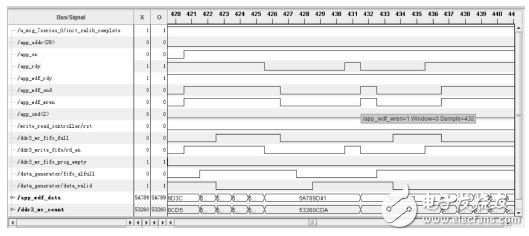

用户使用时,只需设计DDR3读写控制模块即可通过IP核对DDR3进行读写操作。app_rdy信号是用户接口模块准备就绪的标识,在进行读操作时,只需在app_rdy信号为1时更新读地址即可,读操作时序如图2所示[7]。而写操作相对复杂,若要成功进行写操作,则必须保证写地址和写数据都有效,而写地址和写数据不必同时有效,可以相差几个周期,当用户接口反馈的app_rdy信号和用户控制的app_en信号同时为1时,写操作指令app_cmd以及写地址app_addr有效。而对于需要写入的数据app_wdf_data来说,只有当用户接口反馈的app_wdf_rdy信号和用户控制的app_wdf_wren信号同时拉高时才是有效的。写操作对应的时序如图3所示[7]。

图1 Xilinx Kintex-7 FPGA内存接口解决方案

图2 读操作时序图

图3 写操作时序图

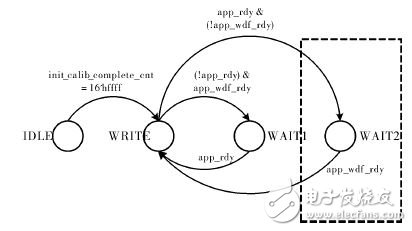

本文基于Verilog HDL 硬件描述语言[8],设计如图4所示的状态机实现DDR3的连续写操作。在IDLE状态下,当DDR3 IP核完成校准后,经过几十μs的延时,写地址和写数据被同时送入IP核,状态机进入WRITE状态。如果写地址与写数据均得到响应(app_rdy & app_wdf_rdy为1),写地址和写数据将得到更新,状态机继续处于WRITE状态。如果只有写数据得到响应(! app_rdy & app_wdf_rdy为1),则停止写数据更新,状态机进入WAIT1状态,待写地址得到响应后,再更新写地址和写数据,并返回到WRITE状态。如果只有写地址得到响应(app_rdy & ! app_wdf_rdy为1),则停止写地址更新,进入WAIT2状态,待写数据得到响应后,更新写地址和写数据,并返回WRITE状态。经实际测试状态WAIT2并不会出现,所以可以将WAIT2状态去掉,对状态机进行优化。

图4 DDR3连续写控制模块状态机"

本文设计的状态机,通过对IP核的控制,成功实现了DDR3连续写操作。用 Chipscope软件进行信号观测,波形如图5所示。由于连续读操作比较简单,文中不再赘述。

图5 DDR3连续写操作Chipscope相关信号波形

2 DDR3读写效率测试与分析

为满足高速数据传输的要求,DDR3需要保证较高的带宽利用率。DDR3的极限速率为两倍工作时钟频率与数据总线位宽的乘积。但是,DDR3的读写共用同一组数据总线,同时DDR3内部是以BANK/行/列的形式组织起来的。在对新的BBANK/行进行读写前,需要执行预充命令和激活命令等[9-10]。同时不同指令之间也有各种时间间隙要求。因此,DDR3的实际传输速率与极限速率有一定差距。根据使用方式的不同,DDR3的接口带宽利用率会存在差异[11-13]。

本文通过测试不同使用情形下DDR3的带宽利用率来寻求具有较高效率的读写控制方式。本测试计算带宽效率的方式是,向IP核中输入指定的激励,观察DDR3芯片接口上的有效数据所占的比例,由此计算出有效带宽。

本文对以下3种DDR3读写方式进行了带宽利用率的测试:

(1)固定Bank多行切换测试。单Bank内,每完成一次写操作,则进入下一个行的相同列。由于两列的打开操作有时间间隙要求,打开列到写操作也有时间间隙要求,导致单Bank内行切换时,测得的带宽利用率较低,仅为11%;

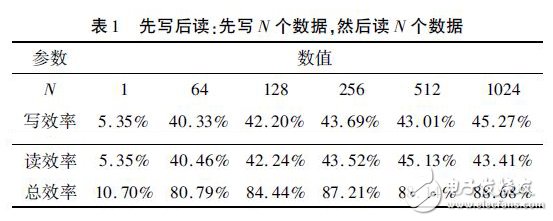

(2)读写切换测试。对DDR3同一地址空间,每进行完1次写操作之后,进行1次读操作。由于相邻读写操作间有时间间隙要求,导致该方式下,带宽利用率较低,仅为10.7%。接着按照先进行N次写操作,再进行N次读操作的读写方式进行测试,其结果记录如表1所示;

(3)两Bank不换行平滑过渡测试。先在Bank0的同一个行内连续写8次然后过渡到Bank1的同一个行内连续写8次。结果显示,在Bank0的写操作过程中打开Bank1的一个Row,而不影响Bank0的写操作。由于提前了足够的时间打开Bank1,那么等Bank0的写操作结束后,可以直接平滑的过渡到Bank1的写操作阶段,中间没有等待。该方式下,带宽利用率为91%。

经测试项验证可发现:Xilinx MIG IP 核对DDR3芯片进行按地址连续存储,效率较高。但Xilinx MIG IP 核对DDR3的随机地址存取效率比较低。使读写效率降低的主要原因有:同Bank行切换、读写切换、IP核Bank管理方式。故可采取以下方式提高DDR3带宽利用率:(1)降低读写切换的频率;(2)采用连续地址存取的方式,减少Bank和行的切换;(3)在对MIG IP 核进行配置时,用户接口地址映射方式采用“ROW——BANK——COLUMN”方式,降低行切换的频率。

3 DDR3读写控制模块的类FIFO封装

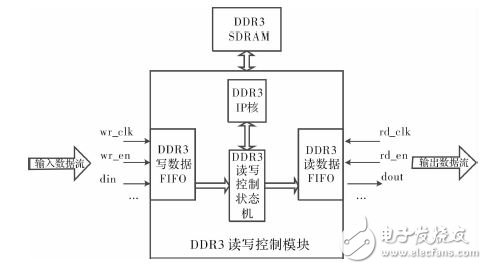

为便于DDR3模块与其他模块对接,方便用户的使用,对其进行类FIFO接口封装[14-15],整个模块结构框图如图6所示。可见封装后的DDR3模块外部接口与FIFO非常相似,因此有效提升了使用的便捷性。DDR3模块是由写FIFO模块、读FIFO模块、DDR3读写控制模块、DDR3 IP 核4部分组成。写FIFO模块用来接收数据。读FIFO模块用来输出从DDR3内读取的数据。DDR3读写控制模块用来控制DDR3的读写操作,合理切换读写状态,保证读写效率。DDR3 IP核模块为FPGA与DDR3的物理接口。

图6 类FIFO接口封装结构图

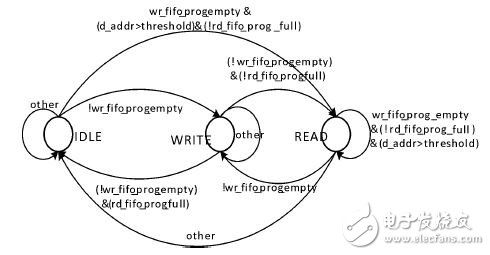

可以看出,DDR3模块设计的关键是读写控制状态机的编写。此状态机共有3种状态,IDLE状态下不进行读写操作,WRITE状态下进行连续写操作,READ状态下进行连续读操作。根据上述分析,为保证较高的读写效率就要避免频繁的读写切换。因此,写FIFO的编程空信号

wr_fifo_prog_empty和读FIFO的编程满信号rd_fifo_prog_full均采用双门限的设置。若写FIFO满,则数据会丢失,而读FIFO满只会使数据在DDR3内缓存,因此,写操作的优先级高于读操作,状态机如图7所示。

图7 DDR3读写状态机

为确保设计的可行性及可靠性,对编写的DDR3读写控制器进行板级验证,硬件测试中选用Xilinx公司的Kintex-7 FPGA以及Micron公司的DDR3 SDRAM芯片。DDR3工作频率为500MHz,经测试其可对3GB/s的数据流进行稳定缓存。

4 结束语

本文对DDR3读写状态机进行了设计与优化,并对DDR3在不同读写方式下的带宽利用率进行了测试与分析,提出了保证带宽率的相应措施。在此基础上,将FPGA的DDR3的读写控制模块封装成简单的类FIFO接口。并将其在Xilinx公司的Kintex-7 系列FPGA芯片上实现,工作稳定可靠、有较高的工作效率、接口简单、可移植性高,为DDR3在高速数据流缓存中的应用提供了便利。

-

DDR3布线参考电子学习 2022-12-07

-

ddr3一般上电多久后可对其进行读写操作?2014-06-14 0

-

如何提高DDR3的效率2015-08-27 0

-

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢2016-01-14 0

-

基于FPGA的DDR3六通道读写防冲突设计2018-08-02 0

-

基于FPGA的DDR3 SDRAM控制器的设计与优化2018-08-02 0

-

基于FPGA的DDR3多端口读写存储管理的设计与实现2018-08-02 0

-

基于FPGA的DDR3用户接口设计2018-08-30 0

-

怎样对DDR3芯片进行读写控制呢2021-08-12 0

-

ddr3的读写分离方法有哪些?2017-11-06 8495

-

Virtex7上DDR3的测试例程2022-08-16 1322

-

基于AXI总线的DDR3读写测试2023-09-01 2314

-

基于FPGA的DDR3读写测试2023-09-01 872

-

阐述DDR3读写分离的方法2023-10-18 587

全部0条评论

快来发表一下你的评论吧 !