高效、低成本的 FPGA 器件:Spartan-7 FPGA!

FPGA/ASIC技术

描述

赛灵思 Spartan®-7 系列提供了一系列高效、低成本的 FPGA 器件。这些器件经过专门设计,能满足低成本市场的特殊需求。

摘要

Spartan®-7 FPGA 将高性能 28nm 可编程架构与低成本小尺寸封装完美结合在一起,同时满足高性能与小型 PCB 尺寸需求。

Spartan-7 系列器件的主要优势包括 :

• 采用 28HPL (High performance/low power 高性能低功耗)工艺,具有最高单位功耗性能比

• 28nm 架构扩展,可实现设计复用

• Vivado® Design Suite 可实现简单的低成本设计输入与验证

上述优势使得 Spartar-7 FPGA 系列可以低功耗、低总成本为设计人员提供了必要资源,可满足低成本应用的要求。

简介

赛灵思 Spartan®FPGA 系列自 1998 年问世以来就一直是业界领先的成本优化型 FPGA 产品系列。该系列包含数代成本优化型小尺寸器件,旨在实现桥接、交换、控制、处理、接口等功能。但为了满足当今低成本应用(诸如工业物联网 (I-IoT)、高级驾驶员辅助系统 (ADAS)/ 驾驶员感知系统以及新一代通信系统等)的性能和功能要求,单单逻辑远不能满足其需求。为应对日益提高的功能和小尺寸要求,Spartan-7 系列致力于在小面积封装中提供成本优化的高性能可编程逻辑。

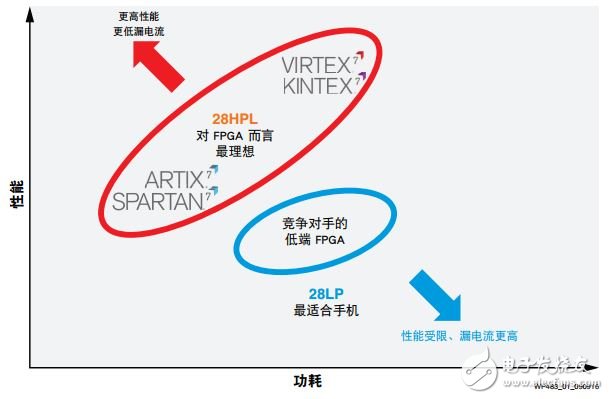

选择最佳工艺

赛灵思在开发 7 系列(Artix®-7、Kintex®-7 以及 Virtex®-7)器件过程中与台积公司 (TSMC) 通力合作,共同开发出了 28nm HPL 工艺。高介电层金属闸 (HKMG) 工艺提供了高性能与低功耗的最佳组合,能帮助打造出满足不同市场需求的不同产品系列。Spartan-7 FPGA 采用与成熟的 7 系列相同的 28HPL 工艺,以及众多底层架构元件,从而使其成为结构紧凑的成本优化型 FPGA 系列器件。该产品系列具备很高的逻辑和 I/O 性能,功耗也得到严格控制,可采用很小的封装,而且价格低廉。得益于工艺的灵活性,该器件可在两种不同内核电压下工作,使用户能够在最高性能与最低功耗之间权衡。与竞争对手的FPGA 使用的 28LP (Low Power 低功耗)工艺相比,28HPL 工艺具有足够宽的工作窗口,使器件能实现更好的性能 / 功耗指标,即以更低功耗实现更高性能。见图 1。

图 1 :Spartan-7 FPGA 28HPL 工艺的优势

为成功而构建

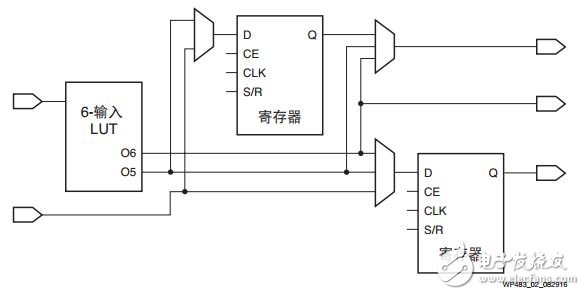

逻辑结构是所有 FPGA 架构的核心。逻辑单元是器件容量与功能的统一测量标准,设计人员要想理解用器件能做什么事情,还需要深入了解一下其中的构建模块。Spartan-7 FPGA 采用一个包含 Slice 的可配置逻辑块 (CLB) ;Slice 由查找表 (LUT)、进位链和寄存器构成。这些 Slice 经过配置可以执行逻辑功能、算数功能、存储器功能以及移位寄存器功能。

随着 Spartan-7 FPGA 产品的更新换代,CLB 中的资源数量也在发展演变,以便不断以合适的成本提供最佳功能。例如,第一代 Spartan 器件(于上世纪 90 年代末推出)中的 CLB 包含一个 3 输入 LUT、两个 4输入 LUT 和两个寄存器。与 Spartan-7 FPGA 的 CLB 中的八个 6 输入 LUT 和十六个寄存器相比,不难看出器件功能的进步。见图 2。

图 2 :Spartan-7 FPGA LUT 与寄存器连接

Spartan-7 FPGA 中的 LUT 可以配置成一个具有单个输出的 6 输入 LUT,或者配置成具有独立输出的两个 5 输入 LUT。每个 LUT 都可在触发器中可选择性地寄存。四个 LUT 和八个触发器构成一个 Slice,两个 Slice 构成一个 CLB。部分 Slice 还可以将它们的 LUT 作为分布式 64 位 RAM 或作为 32 位移位寄存器(SRL32)。

这些灵活、强大的功能都可由 Vivado® Design Suite 的综合阶段直接实现,使用户能方便地利用这些高级功能,且无需花时间学习各个模块的端口和信号名称。Spartan-7 FPGA 提供的高设计效率不仅限于LUT 和寄存器 ;还为设计人员提供了专门用于处理和存储数字信号的模块。

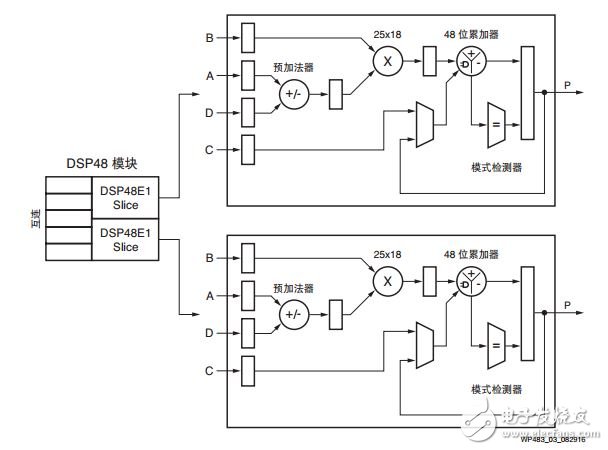

DSP

音频与视频内容在新型系统中越来越普及。需要高速数学性能对数字化音频和视频数据进行操作。为了便于在这样的环境中开展设计工作,所有 Spartan-7 FPGA 都包含一系列 DSP 模块,每个模块包含两个DSP Slice。每个 Slice 都包含一个 25x18 乘法器和一个 48 位累加器——可在 550MHz 或更高频率下工作。见图 3。

图 3 :Spartan-7 FPGA DSP48 模块

25 位预加法器支持对称滤波器(如 FIR 滤波器)的高能效创建。中等密度的 Spartan-7 器件(如XC7S50)有 120 个 DSP Slice,如果都用来实现对称 FIR 滤波器,能为设计人员提供 132 GMAC/s 的处理能力。即便拥有这样的处理能力,仍需要空间来存储预处理和后处理数据。

存储器

除了之前提到的分布式 RAM 以外,所有 Spartan-7 FPGA 都包含名为 Block RAM 的可配置 36Kb 存储模块。每个 Block RAM 均支持不同工作模式,包括单端口、简单双端口、真双端口和 FIFO。BlockRAM 可用作单个 36Kb 模块,分成两个独立的 18Kb 模块,或者连在一起构成 64Kb 或更大的 RAM。为了确保存储器的内容正确,每个 Block RAM 都有可选的检错和纠错 (ECC) 电路,能够校正单位错误和检测双位错误。Spartan-7 FPGA 包含多达 120 个 Block RAM,相当于 4.2Mb 的片上存储器。加上分布式RAM,存储容量可达 5.3Mb。

I/O 与存储器接口

Spartan-7 FPGA 通过宽范围 (HR) I/O 在 PCB 板上通信,该 I/O 支持多种通信标准,包括 HSTL、SSTL、LVDS、LVCMOS 和 RSDS,工作电压为 1.2V-3.3V。可编程驱动功能使 HR I/O 能以尽量低的功耗实现速度高达 1250Mb/s 的任意连接。为进一步降低功耗,I/O 模块中的各个组件在不使用时可以禁用。例如,输出缓冲器在读事务处理时被禁用,输入缓冲器在写操作时被禁用。见图 4。

图 4 :禁用 I/O 缓冲器

与其他 Spartan-7 FPGA 功能的启用方式类似,Vivado Design Suite 为设计人员省去了决定何时禁用 I/O 缓冲器的麻烦。

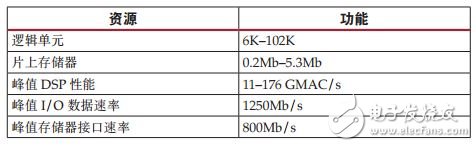

Spartan-7 FPGA 中的 HR I/O 按 50 个 I/O 引脚一组排列。由于实现了内置的存储器 PHY,因此每个完全绑定的组都能实现存储器接口。Vivado Design Suite 中的存储器接口生成器 (MIG) 工具可简化软存储器控制器的创建,以适应设计人员的要求。经配置可支持高达 800Mb/s 的低成本主流 DDR3,或者DDR2 和 LPDDR2 这样的旧标准。表 1 列出了 Spartan-7 FPGA 的功能。

表 1 :Spartan-7 系列的功能

PCB 板上

工业控制系统等应用领域经常需要在很大区域内分散安装多个电子设备,但每个位置的面积却非常有限。通常,需要对传感器信号进行整理和处理,并送到中央控制单元进行组合。用来执行初始整理和处理任务的物理面积一般非常有限。

小尺寸、低成本封装

为了将强大的可编程功能塞入空间有限的区域,Spartan-7 系列采用了尺寸仅为 8x8mm 和球栅间距仅为0.5mm 的低成本封装。采用相同封装的器件引脚兼容,如果需要增加功能,用户只需在单个封装内向上升级移植即可。

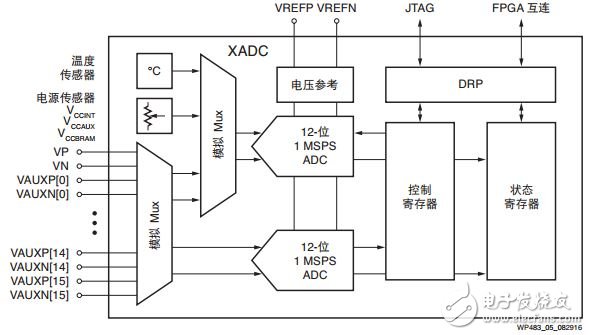

XADC

大多数 Spartan-7 FPGA 包含一个名为 XADC 的灵活的模拟接口。当与可编程逻辑结合使用时,XADC可以满足多种数据采集和监控功能需求。这就使得设计人员能够监控远程且难以接入的位置上的系统行为。见图 5。

图 5 :XADC 方框图

XADC 包含两个 12 位、1MSPS ADC,具有独立的跟踪与保持放大器 ;一个片上多路复用器,多达 17个外部模拟输入 ;以及片上热传感器和电源传感器,可确保整个系统的可靠性、可用性、安全性和保密性,以符合 FIPS 140-2 安全等级 4。

设计安全性

除了 XADC 提供的运行安全性之外,大多数 Spartan-7 FPGA 还通过一系列不同措施提供设计和 IP 安全性。使用 256 位 AES 加密法对编程文件或比特流进行加密,以确保系统断电和加电配置过程中的机密性。可将解密密钥存储在电池供电的 RAM 或 eFuse 中 ;前者能在检测到篡改活动时清空密钥内容。

提供工作所需的工具

Vivado IDE 在提供简单、按钮式设计方法方面一直领跑整个行业,可提供众多高级特性,以帮助设计人员快速构建面向 FPGA 和 SoC 的设计。可利用很多设计重用功能将针对某款器件或某个系列而构建的部分设计或 IP 打包,便于以后重复用于采用类似架构的另一款器件或系列。例如,设计人员可创建用在Spartan-7 FPGA 中的 IP 核。随着系统要求的不断提高,设计人员可在 Artix-7 FPGA 中重用这一 IP 核。

Vivado Design Suite 支持 VHDL 2008、Verilog 和 System Verilog,允许用户选择自己最喜欢的语言来输入 RTL 设计。创建设计后,可利用多种调试和验证工具确保功能正确,包括一种免费的混合语言仿真工具(无代码行限制)。

免费的 Vivado HL WebPACK ™ Edition 支持所有量产级 Spartan-7 器件,为这些器件提供最快速、成本最低的工具。

结论

Spartan-7 FPGA 将高性能 28nm 可编程架构与低成本的小尺寸封装完美结合,在实现高性能的同时确保小型化 PCB 尺寸。逻辑、存储器、DSP、I/O 和存储器接口电路以及高性能、低功耗 28nm 工艺的结合,使得 Spartan-7 器件能执行多种严苛功能,例如传感器接口、电机控制以及协议桥接等。成熟的Vivado Design Suite 提供众多省时功能,使设计人员在 Spartan-7 FPGA 上花较少的工作就能够构建出复杂的低成本设计。

- 相关推荐

- F

-

基于FPGA的Spartan-7和Zynq-7000可扩展集成电源设计2019-01-03 0

-

7系列FPGA数据手册:概述------中文翻译版 精选资料分享2021-07-26 0

-

赛灵思推出Spartan-7 FPGA系列密集型器件,能够快速集成和实现2018-08-20 1482

-

Xilinx Spartan-7 7S50器件性能和功耗优势介绍2018-11-28 4680

-

Spartan-7提供最佳成本和I/O优化的解决方案2018-11-22 3258

-

ARTIX-7和SPARTAN-7 FPGA的DDR2和DDR3低成本印刷电路板设计指南2019-02-19 1492

-

Spartan-7 FPGA的详细白皮书资料说明2019-02-25 1112

-

Spartan-7 FPGA产品资料简介2019-02-26 828

-

赛灵思的Spartan-7 FPGA系列器件的关键功能介绍2019-07-30 4127

-

赛灵思Spartan-7器件介绍2019-07-30 4225

-

digilent Cmod S7: Spartan-7 FPGA 介绍2019-11-14 2779

-

从Spartan-6到Spartan-7 FPGA的迁移过程2023-09-14 163

-

Spartan-7 FPGA满足对成本敏感的市场要求2023-09-13 80

-

AMD进军低成本FPGA市场,满足边缘应用需求2024-03-10 562

全部0条评论

快来发表一下你的评论吧 !