JESD204B SystemC module 设计简介(一)

FPGA/ASIC技术

描述

本设计致力于用SystemC语言建立JESD024B的协议标准模型,描述JESD204B的所有行为,并且能够保证用户可以通过该JESD204B的SystemC库,进行JESD204B行为的仿真和RTL代码的编写。

设计以最新的版本JESD204B.01(July 2011)为参考,设计根据数据流的传输分为传输层、数据链路层、物理成进行代码的编写,其中JESD204B的模拟特性在本设计中因为无法实现,所以并没有做过多的描述,具体的模拟的细节可以参考有JEDEC发布的标准协议。

JESD204和JESD204B修订版数据转换器串行接口标准由JEDEC委员会制定,旨在标准化并减少高速数据转换器与FPGA(现场可编程门阵列)等其它器件之间的数据输入/输出数目。更少的互连可简化布局布线,并支持实现更小尺寸的解决方案,同时不影响整体系统性能。这些特性对于克服许多高速ADC应用的系统尺寸和成本限制非常重要,包括无线基础设施(GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA)、收发器架构、软件定义无线电、便携式仪器仪表、医疗超声设备、雷达和安全通信等军用/航空应用。

文档将分别介绍系统的时钟、数据传输层、数据链路层、Deterministic Latency,系统的时钟包括系统中时钟的管理和生成,数据传输层主要完成系统中AD采样数据的映射和组帧,数据链路层主要完成数据流的传输、加扰、编码、同步、纠错,Deterministic Latency作为JESD204B的一个新加入的功能,主要设定系统中中发送器与接收器之间的数据传输的延迟,并保证传输的延迟是固定的。

文档在介绍各个大模块的基础上,将进一步介绍协议中定义的每一个模块的设计标准,需要注意的问题细节,并在每章的最后介绍该模块在SystemC中的设计和仿真情况。

注意:为了保证文档意思的正确无误的表达,所有的专用名词,将用原有的英文表示。

2、CLK

JESD204B内部包含丰富的时钟资源,在一个JESD的系统中,所有的器件将共用一个(source)时钟源,这个时钟可以称为源时钟。经过源时钟,将产生具体的器件需要的时钟,根据系统的结构不同,所需要的时钟也不同。ADC/DAC的输入时钟称为转换器时钟(converter device clock),FPGA的输入时钟称为数字逻辑器件时钟(logic device clock)。

Logic device clk是FPGA的输入参考时钟,FPGA将通过Logic device clk生成所需要frame clock、multiframe clock、character clock、sample clcok、bit clock,以上的时钟将在后面进行具体的介绍。

Converter device clock是ADC/DAC的输入参数时钟,同理,ADC/DAC上的所有时钟都由converter device clock时钟衍生而来,衍生的意思指其他的时钟可以由converter clock 通过PLL生成,也可以是converterclock只作为生成其他的时钟的参考或者边沿对齐标志,在本次的设计中,ADC/DAC上的所有时钟由converter device clock倍频或者分频得到,并且他们的相位对齐。

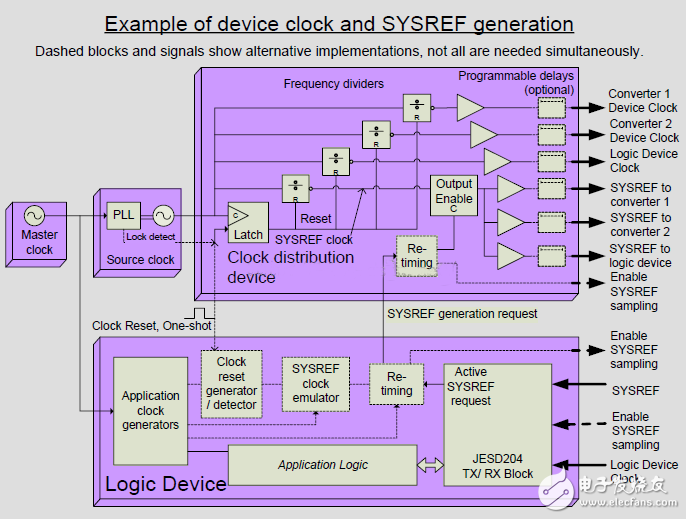

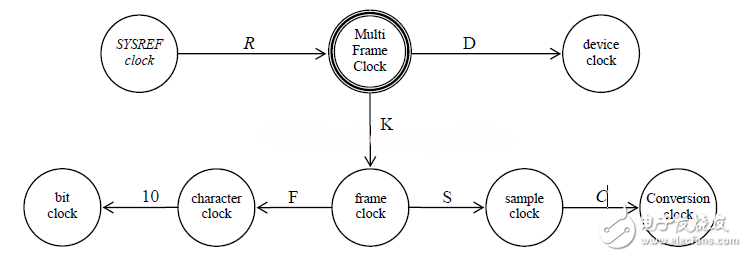

图1:时钟拓扑接口图

如图1所示,系统的时钟管理包括两个部分:clock distribution device 模块,apllication clcok generators模块。

clock distribution device 模块为时钟源控制模块,该模块生成系统中所有的器件需要的时钟,并且包括SYSREF信号,SYSREF是系统中发送器件与接收器件的同步信号。该模块生成接收器和发送器所需要的device clock,在JESD204A中,接收器和发送器的devcie clock必须保持一致,而在JESD204B中,各自的device clock可以是不一致,但是建议各个器件的devcie clock的频率保持整数倍的关系。

2.1 Device clock

Device clock 是所有接收器和发送器的所有时钟来源,每一个发送与接收器都需要一个Device clock,不同器件间的Device clock必须由唯一的Source clock生成。Device clock 可能与frame clock、multiframe clock 的频率不同。但是frame clock、multiframe clock须由Device clock 衍生而成,也可以理解为device clock 是各个器件的PLL的参考时钟。

根据Device clock与frame clock、multiframe clock的关系,JESD204B的时钟模式可以分为以下3类:

Subclass0: 该时钟类是为向JESD204A保持兼容。

Subclass1: Multiframe clock的时钟周期必须是device clock的整数倍,主要的特点是用SYSREF完成不同器件的时钟同步。

Subclass2: Device clock 生成frame clock、multiframe clock,同时Tx Device clock 必须是RX device clock的整数倍,或者RX device clock 是Tx Device clock的整数倍,在该时钟类下,接收器与发送器的同步通过SYNC信号,并且通过发送控制信号完成发送或者接收器中的时钟调整。

2.2 Frame clock 、Local Multiframe clock

Frame clock 是应用层和JESD204的链路层桥梁。

在链路层中,数据会先被组合成帧,多个单帧又会组成复帧(multiframe),multiframe 必须与LMFC(Local Multiframe clock)对齐。

每个发送与接收器有独立的device clock,并且frame Frame clock 、Local Multiframe clock由device clock派生。frame Frame clock 、Local Multiframe clock 可以直接由device clock生成,也可以由device clock 来同步,派生出frame Frame clock 、Local Multiframe clock。

如果Multiframe clock由device提供,在Subcalss 1中LMFC的起始相位由SYSREF决定。在Subcalss2中,由SYNC的上升沿决定。

Frameclock 、LocalMultiframe clock的要求如下:

l 所有的发送与接收器Frame clock的周期必须一致。

l 所有的发送与接收器的Multiframe clock的周期必须保持一致。

l 在JESD204系统中所有的Frame clock 、Local Multiframe clock必须来自同一个时钟源。

l 在每个device中,frame clock与LMFC必须保持对齐

l 在Subclass 1中,当SYSREF为高电平时,Frame clock 、Local Multiframe clock的上升沿与device clock第一个上升沿对齐。

l 在Subclass 2中,Frame clock 、Local Multiframe clock与SYNC的上升沿对齐。

l Device可以允许LFMC的相位可以小范围的调整,这样可以保证系统中所有的devices更好的对齐,这个功能主要针对于subclass2,通过LFMC的相位,可以保证发送器与接收器的LFMC对齐。

如果一个device支持多个JESD204,上述要求是独立的。

2.3 SYNC

SYNC的接口是接收器给发送器的一个反馈,SYNC必须与RXdevice内部的frame clock同步。同时,强烈建议TX frame与SYNC也保持同步(在Subclass 0和Subclass 2有要求)。强烈建议SYNC的接口与deviceclock的接口的物理特性保持一致,以获得一致的延时。

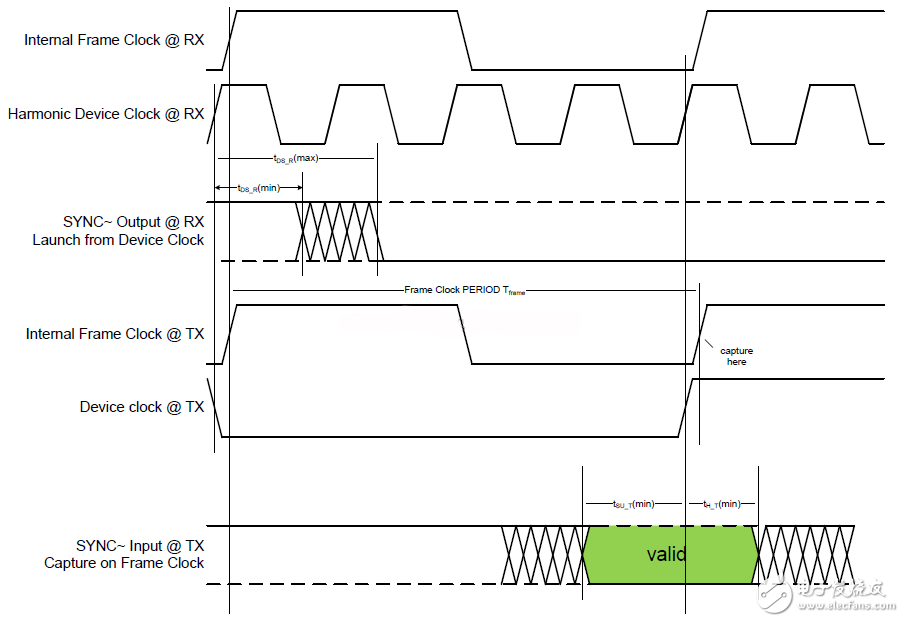

图2 subclass 0和subclass 2 中SYNC的时序

:是指Device clock到SYNC的延迟。

:建立时间

:保持时间。

图2中展示了SYNC的时序图,对于Subclass 0和Subclass2 是必须的,Subclass 0是为了保持与JESD204A的兼容性,而在Subclass 2 中用于解决发送与接收的延迟的问题。

当device的devices clock快于或者等于frame clock是,device clock 将用于对齐SNYC,而当deivice clock 慢于frame clock时,SYNC将由frame clock抓取。

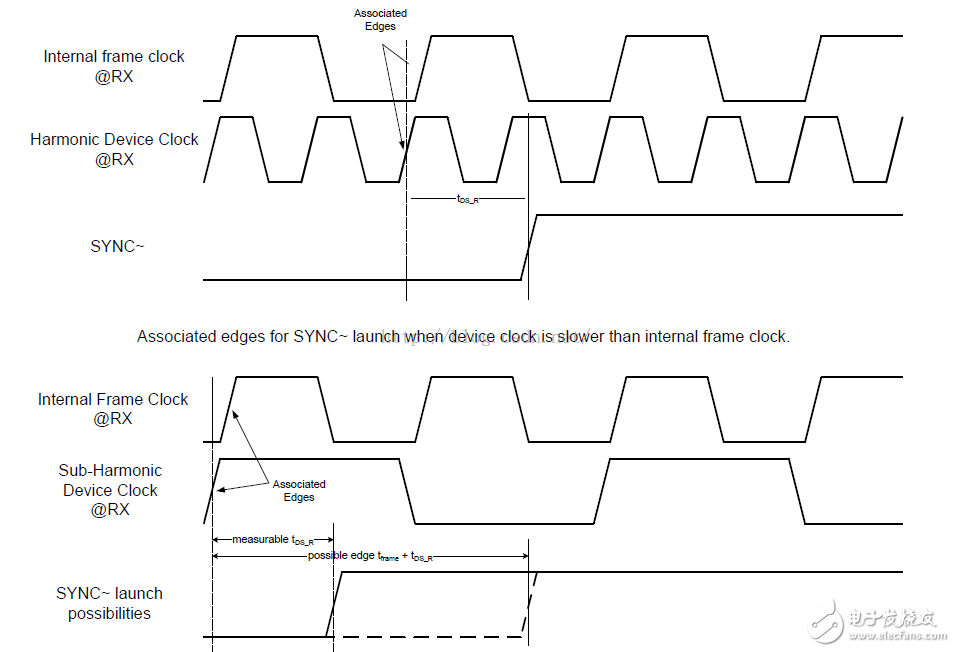

图3 Subclass 0和Subclass 2 中device clock中时钟边沿的关系

图3中展示的两种不同情况下,各个时钟边沿的关系,在第一种情况下,frameclock的时钟慢于deviceclock,第二种情况刚好相反。

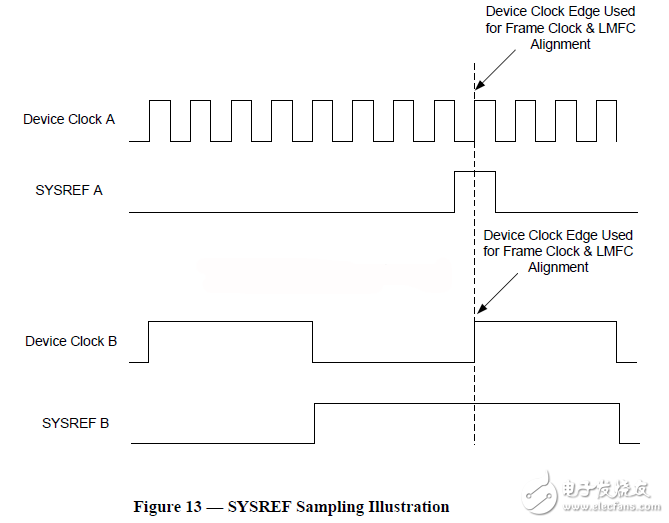

2.4 SYSREF signal(Device Subclass 1)

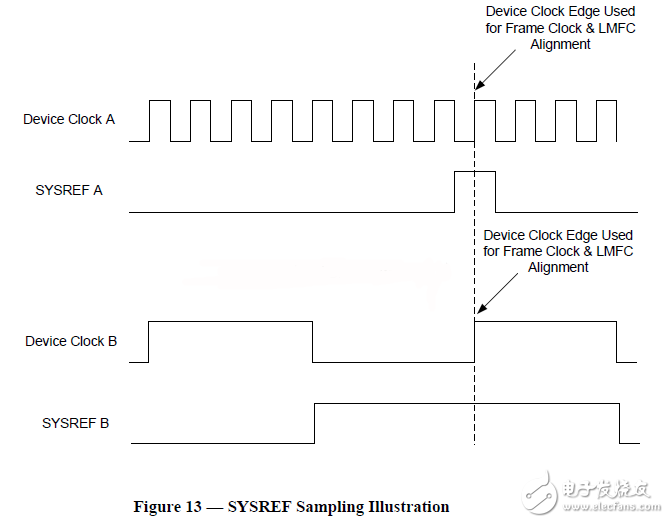

在Subclass1中,SYSREF信号将实现发送器与接收器之间有固定的数据延迟,SYSREF的目的是用来确定用哪个一个device的的上升沿来对齐LMFC和frame clock的相位。因为LMFC和frame clock通常会与character clock对齐,所以在调整LMFC和frame clock时,character clock的相位也需要同时的调节。

SYSREF可以是一个周期信号,或者脉冲的周期信号,也可以是单脉冲信号,只有在器件请求同步是,才产生SYSREF信号,高电平有效,一般是通过deviceclock的上升沿抓取,但也可以通过下降沿抓取。

对于周期的SYSREF来说,他的频率必须是LMFC的整数倍,LMFC和frame clock将与抓到SYSREF信号的device clock的上升沿对齐,周期的SYSREF信号除了对齐器件的时钟外,也可以通过检测各个时钟是否与SYSREF时钟对齐来时钟是否发生偏移。

图4:SYSREF对齐示意图

对于整个系统来说,

对于系统的同步最需要考虑的是系统的延迟,由于分布延迟的不确定性,会导致很多的问题,而本次设计搭建的是纯数字的不同的device不一定必须共用一个SYSREF,但是必须保证不同的SYSREF信号之间有固定的关系。逻辑系统,所以不考虑上述的问题。

对于系统的延迟主要包括:Interconnect skew、Intra-device skew、Inter-device skew、

Clock distribution skew、SYSREF distribution skew、SYNC~ distribution skewInter-device 、SYNC~ generation skew详见JESD204B的spec。

2.5 SystemC 中的时钟模型设计

在模型的设计中,系统的主要包含两个时钟模块,Clock_distribution_device 模块, jesd204clk_generator模块,以及SYNC_signal_encoder和SYNC_signal_decoder模块。

2.5.1 SYNC signal encoder and decoder

该模块工作与frameclock时钟域下。

在SystemC模型中,SYNC_signal_encoder在接收器中,该模块接收系统中的SYNC请求,并生成SYNC信号。具体的流程如下:

Ø 系统复位后,SYNC信号的初始值为0,即SYNC复位后将直接生效。

Ø RX_link控制器运行后,状态机运行生成gen_SYSREF_req信号,gen_SYSREF_req也可以是由系统传输发送错误引起,也可以由其他情况触发。

Ø 在Subclass 0中,SYNC将延迟gen_SYSREF_req一拍输出。

Ø 在Subclass1、2中,SYNC信号在gen_SYSREF_req下降沿是后有效,在gen_SYSREF_req的上升沿后的第一个multiframeclock的上升沿后SYNC将被置1,无效。

在SystemC模型中,SYNC_signal_decoder在发送器中,该模块在接收系统中的SYNC请求,并将不同器件的SYNC信号组合到一起,实现SYNC的解码。具体的流程如下:

Ø 将多个器件的SYNC相与输出

Ø SYNC~有效4个frame clock时钟后,认为系统重新同步请求有效

SYNC~有效的持续时间小于4个frame clock,认为接收器接收发生非致命错误。

2.5.2 jesd204clk_generator

该模块生成系统所需要的6个时钟,multiframe_clock、frame_clock、sample_clcok、character_clcok、bit_clock、sample_clcok、conversion_clcok。上诉的所有时钟由device clock生成,并与其对齐。

在subclass 1中,multiframe_clock、frame_clock、character_clcok会与采样到SYSREF高电平的deviceclock的上升沿对齐。

在subclass 2中会multiframe_clock、frame_clock、character_clcok会做相应的调整。]

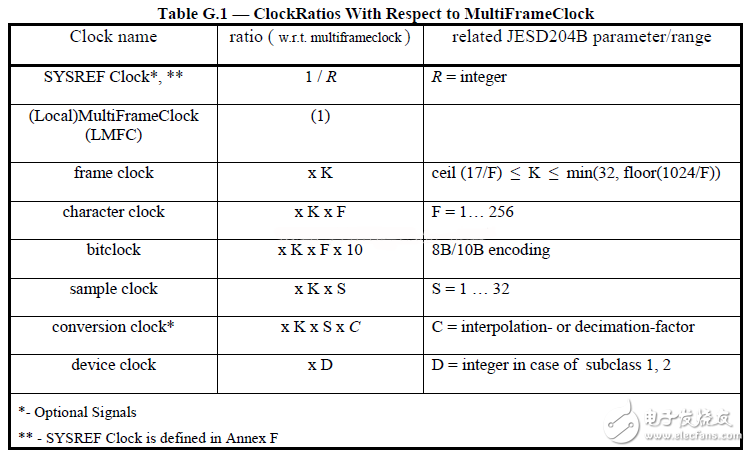

图6:系统时钟的关系图

如上图所示为各个时钟的对应关系,上面的系数的解释如下表:

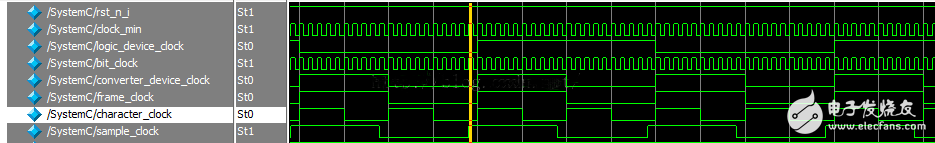

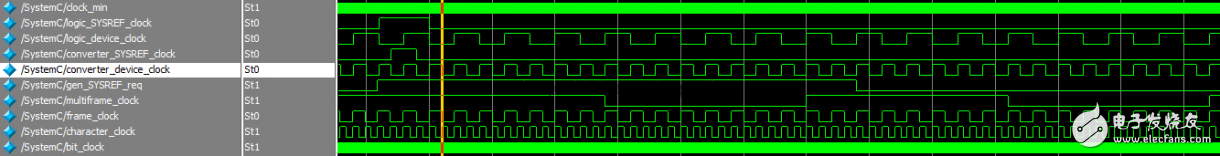

最终的模型仿真如下:

图7:系统时钟时序仿真图

系统中,frame_clcok、multiframeclock、character clcok、sample clcok将根据输入的对应参数生成不同频率关系的时钟,并且frame_clcok、multiframeclock、character clcok的时钟相位可以调整。

SYSREF_req由低拉高后,系统分别生成了FPGA的SYSREF_clock以及converter 的SYSREF_clcok,并且在两个信号的高电平期间,他们的device clock的上升沿对齐。而同时,frameclock、multiframe clock、character clock将从新对齐于device clock的上升沿,具体的如下图所示:

图8:SYSREF信号同步示意图

在模型的设计中,SYNC的模型包括两个部分:SYNC_signal_encoder、SYNC_signal_decoder。

2.5.3Clock_distribution_device

该模块负责生产device clock和SYSREF信号,device clock 由source clock通过PLL生成,并且频率和相位在系统运行的过程中不需要做调整,而SYSREF的信号形式可以多样化,可以是周期的方波、周期的脉冲波、单脉冲信号,本次的模型中采用的单脉冲的信号。具体的实现过程遵循以下几点:

Ø 不同的device有自己独立的SYSREF信号,可以分为converter SYSREF和logic SYSREF。

Ø gen_SYSREF_req信号是生成SYSREF的请求信号,该信号在系统复位或者系统要求从新同步时会有效,信号在SYNC低电平持续4个frame clock周期后拉高,并在SYNC信号由低电平变为高电平后拉低。

Ø gen_SYSREF_req为上升沿有效,在module抓取到gen_SYSREF_req信号上升沿后,SYSREF信号将在logic device clock和converter device clock的第一个对齐的上升沿后输出高电平,以实现不同器件间的同步。

Ø 在SYSREF信号的高电平有效,并持续一个device clock的时钟周期,根据器件的device clock的周期不同,SYSREF信号的高电平持续时间也会不同。

Ø 在SYSREF信号为高电平时,各个器件将复位各个时钟的frame clock、multiframe clock、character clock,以保证各个器件的时钟边沿对齐,具体的仿真如9所示。

图9:SYSREF信号同步仿真图

-

jesd204b2017-12-13 0

-

JESD204B的系统级优势2018-09-18 0

-

JESD204B生存指南2019-05-28 0

-

串行LVDS和JESD204B的对比2019-05-29 0

-

JESD204B串行接口时钟的优势2019-06-19 0

-

jesd204b ip核支持的线速率2020-08-12 0

-

JESD204B是什么工作原理?控制字符是什么?2021-04-06 0

-

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?2021-04-06 0

-

JESD204B协议有什么特点?2021-04-06 0

-

如何去实现JESD204B时钟?2021-05-18 0

-

一文读懂JESD204B标准系统2021-05-24 0

-

如何采用系统参考模式设计JESD204B时钟2022-11-18 0

-

JESD204B协议介绍2022-11-21 0

-

JESD204B的优势2022-11-23 0

-

如何构建您的JESD204B 链路2022-11-04 333

全部0条评论

快来发表一下你的评论吧 !