基于FPGA的超声数据采集装置的设计与实现

FPGA/ASIC技术

描述

摘要:为了实现对某航天器在地面及飞行过程中的超声数据进行高精度、高速采集的功能,根据测量系统的技术要求,设计数据采集装置的硬件电路和时序控制逻辑。为了满足恶劣的环境测试要求,设计采用高速、高精度、宽温度范围的THS1408模数转换器。选取高速运放AD8028 进行信号调理,以FPGA 作为逻辑控制器,控制THS1408 进行模数转换。经测试,采集精度优于0. 5%,满足实际工程需要,具有很高的可靠性,已成功应用于该测量系统。

随着数字化技术不断深入的今天,数据采集技术已经成为信号处理过程中的重要环节。数据采集技术已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤、航空、航天等诸多领域[1-2] 。随着数据采集技术应用的不断加深,不仅对数据采集装置的采集精度、采集速度和数据量有了更高的要求,还要求数据采集装置能够在恶劣环境条件下可靠的工作[3] 。而模数转换芯片性能的优劣对数据采集会产生最直接的影响,因此,本设计在实际应用的背景下,根据测量系统的技术要求,通过合理的选取高速、高精度、宽温度范围的THS1408 模数转换器,优化数据采集装置的电路设计和时序设计,以实现超声数据采集装置的功能。

1 整体设计方案

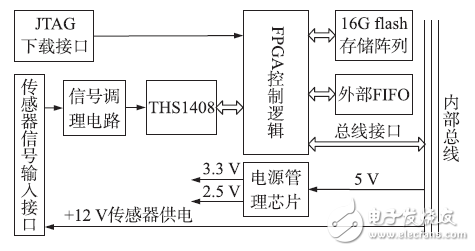

超声数据采集装置的整体设计框图如图1 所示。输入的超声信号是经过传感器转换过的电压模拟信号(0 ~5 V),电压信号经过传感器信号输入接口进入信号调理电路, 调理后的输入信号经过THS1408 前的单端转差分电路后转换为差分信号,THS1408 在FPGA 芯片的逻辑控制下,将差分信号进行模数转换,模数转换后的数字量经过内部程序进行数据处理后缓存入外部FIFO 中,再将FIFO 中的有效数据编帧、存储在16 Gflash 存储阵列中。超声数据采集装置通过总线接口进行板间通信:接收上位机指令,上传数据和装置状态。

图1超声数据采集装置的整体设计框图

2 THS1408 功能简介

测量系统要求超声数据采集装置的单通道采样率为5 Msample/ s,分辨率为12 位,采样精度小于0.5%,保留8 位有效数据位,采集装置的工作温度

范围为-50℃~125 ℃,模数转换芯片功耗小于500mW。为了满足超声数据采集装置的技术指标,设计选用了德州仪器的THS1408 模数转换器,THS1408 具有以下功能特点:

(1)采样速率高:3 Msample/ s ~8 Msample/ s 采样率;

(2)工作温度范围宽:-55 ℃~125 ℃;

(3)功耗低:典型功耗为270 mW,最大功耗为360 mW;

(4)14 位分辨率;

(5)差分输入接口;

(6)可编程输入增益;

(7)单电源供电;

(8)片内集成高性能的采样保持放大器和参考电压源。

THS1408 在宽温带、强振动的环境下,能够满足测量系统的技术要求,且具有很好的性价比和功耗/速度比[4] 。

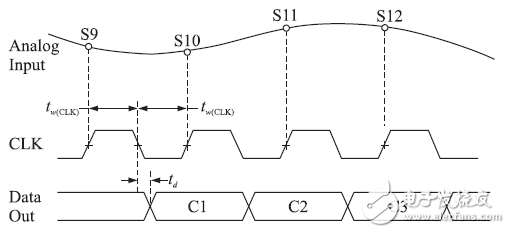

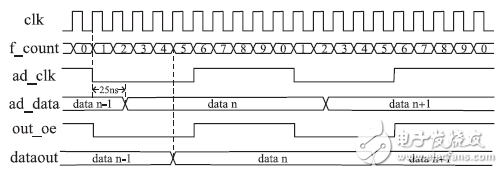

THS1408 的采样内核采用的是一个延时9. 5 个采样周期的循环采样结构,信号开始采样后的9. 5个时钟周期后,转换结果开始输出,THS1408 采用具有三态缓冲的并行数据接口,可以直接连接到数据总线接口,通过驱动OE 为低可以将数据输出使能,使得电路设计更加简单。采样时序如图2 所示。时钟频率为5 MHz,时钟上升沿采样,下降沿输出数字量,数据输出延时td =25 ns。

图2THS1408 采样时序图

3 超声采集电路设计与分析

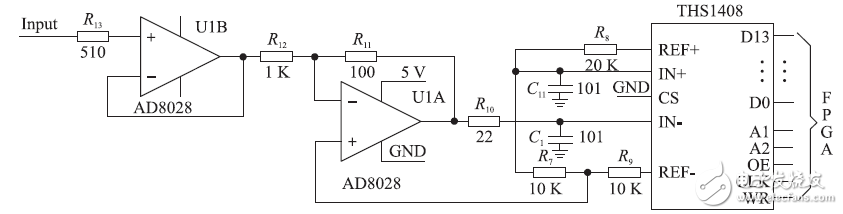

超声采集电路主要由两部分组成:信号调理电路、单端转差分电路和模数转换电路。电路原理图如图3 所示,信号调理电路的功能是对输入信号进

行运放跟随调理以及接口保护,R13 为接口保护电阻,单端转差分电路将输入信号转为差分信号,满足THS1408 转换的输入信号要求,模数转换电路为:FPGA 芯片控制THS1408 完成模数转换部分[5] 。

图3 超声采集电路原理图

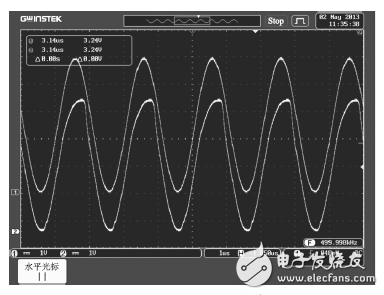

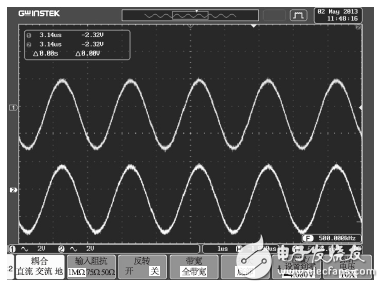

输入的超声信号是经过传感器转换成电压量的模拟信号(0 ~5 V),输入信号频率不大于1. 5 MHz,设计拟采用-3 dB 带宽为16 MHz 的AD823 进行运放跟随,在电路调试的过程中,当信号频率达到500 kHz时,经过AD823 运放跟随后信号出现明显失真现象,运放跟随前后波形如图4 所示(通道1 为跟随前波形)。为了解决高频信号经过运放跟随后波形失真的现象,设计采用低失真率、-3 dB 带宽为190 MHz 的AD8028 替换AD823,经过AD8028 进行运放前后的测试波形如图5 所示(通道1 为跟随前波形)。电路采用AD8028 以后, 当信号频率达到最大要求(1. 5MHz)时,运放跟随后的波形效果仍然很好,失真几乎可以忽略不计,大大提高了信号采样的精度[6-7] 。

由于THS1408 的模拟信号输入接口采用差分形式,而输入信号为单端模拟信号,所以需要对输入信号进行单端转差分处理。THS1408 芯片资料推荐了两种单端转差分的电路:变压器耦合和单端配置方式单端转差分电路。变压器耦合单端转差分电路虽然精度较高,抗干扰能力较好,但是电路比较复杂,而且功耗较高;单端配置方式单端转差分电路简单,容易实现,功耗较低,能够满足采样精度要求,综合考虑,设计采用单端配置方式的单端转差分电路,电路设计如图3 中运放跟随和THS1408 之间的电路。

图4AD823 运放跟随前后波形

图5 AD8028 运放跟随前后波形

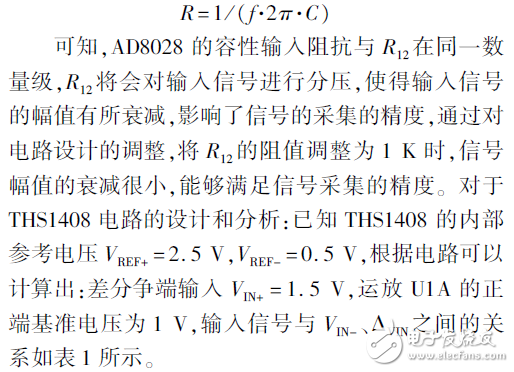

芯片资料推荐电路中R12 为10 K,在实际电路调试过程中,AD 运放的容性负载随着输入信号频率的增大不断减小,当输入信号频率达到1 MHz 以上时,根据AD8028 的输入电容值C =和容性负载计算公式:

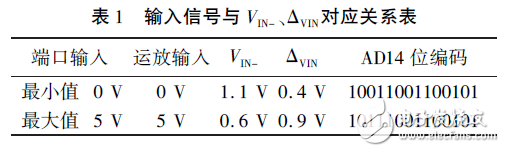

系统要求采集的有效数据位为8 位, 根据THS1408 芯片资料可知:驻VIN 的范围为-2 V ~ 2 V,对应的AD14 位编码为0 ~16 383,编码方式设置为

线性二进制。为了实现有效编码的全范围覆盖,即输入电压范围为0 ~5 V 时,采集的有效对应编码为0 ~255,设计驻VIN 最值差为0. 5 V,对应的AD14 位编码差值为2 048,通过FPGA 内部程序将模数转换的高11 位编码进行转换处理:如果高11 位编码大于“10111001100冶,则有效对应编码值为255;如果高11 位编码小于“10011001100冶,则有效对应编码值为0; 其他情况下, 高11 位编码减去零位值(10011001100)后,取低8 位数据为采集的有效对应编码。经过内部程序处理后,输入电压范围为0 ~5 V 时,采集的有效对应编码为0 ~ 255,最后对采集的有效数据进行编帧、打包和储存。

4 时序逻辑设计

设计采用Xilinx 公司的FPGA 芯片作为时序逻辑控制器[8-9] ,根据THS1408 的采样时序和采样率确定AD 采集时序如图6 所示。系统时钟CLK 频率为60 MHz,AD 采样时钟ad_clk 为6 MHz,系统上电后,FPGA 按照THS1408 的写时序对THS1408 的增益寄存器、偏移寄存器、控制寄存器进行初始化配置,增益设置为1,偏移校正值设置为0,THS1408 工作模式设置为:普通工作模式、内部参考电压、线性二进制编码方式。当上位机下发超声数据采集命令时,采集装置进入数据采集状态,通过对系统时钟进行计数分频产生AD 采样时钟ad_clk,对输入信号进行采样和数据转换,再通过控制数据输出使能out_oe 输出转换的14 位数字量,数字量经过内部数据处理缓存入外部FIFO 中,再将FIFO 中的有效数据编帧存储在16 GFlash 存储阵列中[10] 。当上位机下发读取超声数据命令时,超声数据采集装置将Flash 中的有效数据通过总线接口上传到上位机进行数据处理。

图6 AD 采集时序

5 功能验证

将超声数据采集装置接入测试系统,对超声数据采集装置进行功能测试。在模拟的工作环境下,通过地面测试台为采集装置提供3 V 直流量,上位机软件将超声数据采集装置采回的数据进行数据处理和分析,数据的帧校验准确无误,对分解后的数据进行绘图。

经过功能验证,超声数据采集装置满足实际工程的要求,能够可靠的对超声数据进行采集。本设计只介绍了单通道的超声数据采集,在单通道的基础上,增加多路采集电路设计和调整AD 的采集时序可以实现多通道数据采集,这里就不做介绍了。

-

求电压数据采集装置设计2015-05-31 0

-

无线数据采集2017-05-04 0

-

基于FPGA与SRAM数据采集系统设计2018-05-09 0

-

基于FPGA+AD7609的数据采集系统实现2018-08-09 0

-

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究2019-07-09 0

-

FPGA实现数据采集的方式对比(传统串口、数据采集卡及外设计接口)2020-01-07 0

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 0

-

具有多种通信功能的数据采集装置的实现2009-12-17 433

-

一种深海长期观测低功耗数据采集装置2009-12-23 643

-

多通道超声探伤数据采集处理技术2010-08-05 552

-

利用ColdFire uClinux实现数据采集和传2010-01-13 638

-

基于FPGA的数据采集板设计与实现2016-05-10 512

-

基于磁阻传感器的地磁数据采集装置_李文胜2017-03-19 722

-

关于CC2420的煤矿井下采掘设备无线数据采集装置2018-04-24 925

-

基于FPGA的在临空环境下实现数据采集系统的设计2020-01-27 791

全部0条评论

快来发表一下你的评论吧 !