简析Zynq芯片中PS和PL之间的9个双向读写的通信端口

FPGA/ASIC技术

190人已加入

描述

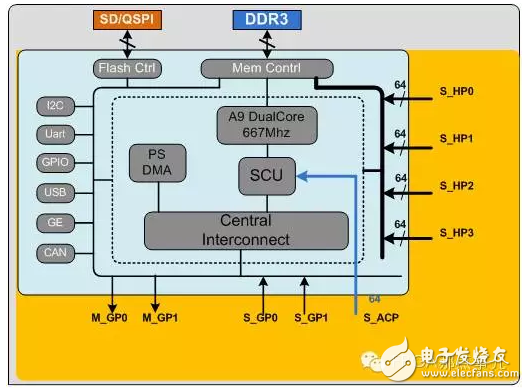

Zynq芯片中,PS(ProcessorSystem)和PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是:

M_GP0 &M_GP1

S_GP0 &S_GP1

S_AXI_HP0-3

S_AXI_ACP

这些端口的特性和适合的使用场景都不太一样,其中M_GP适合CPU和FPGA之间少量的数据通信,S_HP用来进行大批量的数据交互,S_GP很少用到,S_ACP同S_HP类似,但是它可以保证CPU和DDR3之间的Cache一致性。

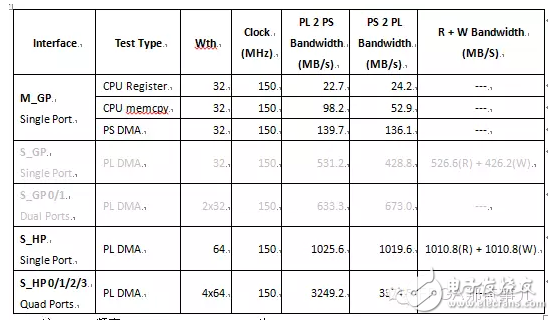

那么这些接口实际使用时,它们能提供的最大吞吐量如何呢,下标给出了一个实测的数据:

注: CPU频率667Mhz,CPU ClockRatio为6:2:1,DDR Date Rate1066Mhz,PL-PS AXI Clock 150Mhz

S_ACP和S_HP的数据比较接近

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ZYNQ(FPGA)与DSP之间SRIO通信实现2023-02-02 0

-

ZYNQ(FPGA)与DSP之间GPIO通信实现2023-06-16 0

-

简谈Xilinx Zynq-7000嵌入式系统设计与实现2024-04-10 0

-

【Z-turn Board试用体验】由PS向PL提供时钟信号(转载)2015-06-01 0

-

玩转Zynq连载30——[ex52]基于Zynq PS的GPIO控制2019-10-10 0

-

玩转Zynq连载31——[ex53] 基于Zynq PS的EMIO控制2019-10-12 0

-

zynq 7020 PS和zynq PL是如何通话的?2020-05-08 0

-

请问是否可以在同一个Zynq FPGA中从PS控制PL JTAG?2020-07-30 0

-

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?2023-12-15 0

-

实例详解:如何利用Zynq-7000的PL和PS进行交互?2012-12-12 53400

-

Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 242017-02-10 978

-

PYNQ案例(一):ZYNQ的PL与PS开发2020-12-25 6989

-

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL读写PS端DDR数据2021-01-30 13227

-

ZYNQ:使用PL将任务从PS加载到PL端2022-05-10 2089

-

将Zynq PS和PL与内存映射寄存器集成2022-12-06 546

全部0条评论

快来发表一下你的评论吧 !