FPGA中RocketIO GTP收发器的高速串行传输实现方案

FPGA/ASIC技术

描述

提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收发器设计的一个高速串行传输实现方案,详细阐述了硬件设计要点和软件实现概要,系统实测表明,该方案能在某信号处理系统两个板卡之间稳定地进行1.6 Gb/s的数据传输,误码率优于10e-12,传输距离大于1米。

引言

传统的并行总线互联技术因为需要占用大量的芯片管脚与印制板空间,随着更高的速度要求,多条信号线之间几乎无法实现完全同步,为抵消串扰和干扰需要在多条信号线中间插入隔离地线从而使总线数目突增,造成板级布线难度和系统设计以及复杂度急剧增加,也无法满足电子系统便携和小型化要求。而采用包含源时钟的差分同步串行传输方式,如LVDS,因为采用低压差、小摆幅,避免晶体管进入‘饱和’与‘截止’区从而具有快速恢复时间,因此可以做到很高的传输速率,但由于时钟与数据要分别发送,传输过程中各信号瞬时偏差和相位抖动会破坏数据与时钟之间苛刻的定时关系,所以传输速率很难超过1Gb/s每信道。最终,高速、低功耗、极低IO引脚数量、低布线难度、采用自同步(即CDR,时钟数据恢复)方式的串行互联技术,通过编码与时钟恢复功能,将时钟‘内嵌’于数据中,在接收端从数据中提取出所需要的时钟信息,高速传输情况下不存在时钟与数据的同步问题,因而极大提高了传输速率并降低了开发难度和成本,成为新一代信息交换与传输方式的主流。

Xilinx公司的Virtex-5系列FPGA中集成了基于RocketIO的多个GTP或GTX硬核,能够分别提供高达3.75Gb/s和6.5Gb/s的单路传输速率,在FPGA中可使用厂商提供的多种高速串行通信协议IP核,也可以自定义和开发简单高效、低延迟和开销的通信协议,从而可以帮助设计人员方便和灵活高效而可靠的实现高速串行通信。

本文利用Virtex-5 SX95T FPGA中集成的GTP收发器设计和实现了一个高速串行传输系统,实测表明,该系统能在某信号处理系统两个板卡之间稳定地以1.6 Gb/s的速度进行数据传输,误码率优于10e-12,传输距离大于1米。

1.Vritex-5 RocketIO简介

1.1 GTP_DUAL的组成

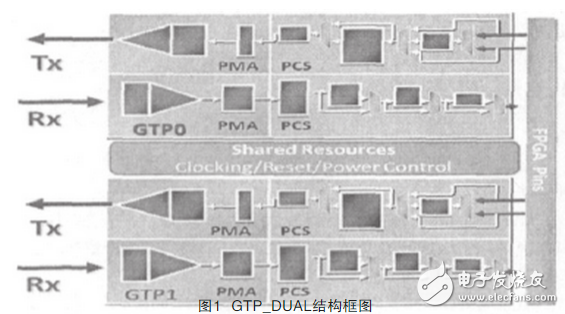

RocketIO是Xilinx公司FPGA集成的高速串行收发器,在Vritex-5平台下的LXT和SXT系列FPGA中,RocketIO称为GTP,传输速率为100Mb/s~3.75Gb/s,速率在100~500 Mb/s范围内时具有可选5倍过采用功能,单个GTP功耗小于100mW;在FXT和TXT系列FPGA中,RocketIO称为GTX,传输速率为750Mb/s~6.5Gb/s,速率在150Mb/s~750Mb/s范围内时具有可选5倍过采用功能,单个GTX功耗小于200mW;而在以往的Virtex-II平台下平均每8个RocketIO收发器功耗为2.2W,在Vritex-4平台下高达3.6W。Vritex-5平台下的每2个相邻的GTP或GTX组成一个基本的GTP_DUAL,图1给出了一个GTP_DUAL结构框图。

从图中可以看到,一个GTP_DUAL由2个GTP收发器和一个共享资源块(包括时钟/复位/电源控制/动态重配DRP)组成,每个GTP收发器分别由发送与接收物理编码子层PCS和物理媒体接口子层构成,结构紧凑并且参数可根据需要灵活配置, 使得GTP_DUAL具有低资源占用和低功耗的特点。

1.2 GTP_DUAL时钟驱动方式

GTP具有3种时钟输入方式:专用时钟引脚输入、共享临近GTP_DUAL时钟输入、使用FPGA内部时钟输入。对于使用专用引脚输入方式,当时钟源满足器件手册上的指标要求时设计具有最佳性能。使用共享临近的GTP_DUAL时钟输入时:在同一列上,时钟布线跨度从源端到目的端,中间相隔的数量不超过3,反之亦然,且禁止GTP_DUAL之间时钟交叉走线;从外部差分对时钟脚引入的单个时钟,所驱动的GTP_DUAL总数量不超过7,性能次之。使用FPGA内部时钟(GREFCLK)输入方式,虽然用法灵活多样,但性能最差,因为它引入了较大的时钟抖动,所以只适用于低传输速率、低误码率要求的场合。

1.3 GTP_DUAL电源设计要求

由GTP收发器构成的高速串行传输系统,其传输链路性能极大地决定于链路两端电源与时钟源及布线设计的好坏,除禁止使用开关电源直接为GTP_DUAL供电外,手册建议以POL方式做电源分配方案,即使用二次降压,先用开关电源进行一次电源变换,再用满足手册要求的低纹波线性稳压电源LDO为它供电,且要对每一个使用的电源引脚做滤波处理。

2.系统硬件平台设计

2.1 GTP_DUAL参考时钟设计

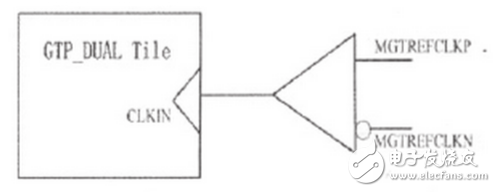

GTP收发器能否可靠的工作,高精度、高质量的参考时钟源至关重要,手册给出的参考时钟最大频率误差容限为±350 ppm,并建议选用差分时钟,本设计采用了低抖动、高性能的差分时钟晶振,采用专用时钟引脚驱动方式,硬件连接如图2所示。时钟晶振为SILICON LABS公司的530FB80M0000DG,工作电压2.5V,差分LVDS信号输出,工作频率为80M,最大频率误差±31.5ppm,相位抖动典型值0.26ps。为了获得最好性能,印制板设计时,晶振四周用地包围,下方禁止电源或其他信号过孔和穿越,其差分输出到GTP_DUAL专用时钟引脚的走线上串接了电容构成AC耦合方式,这样既隔断了直流漂移又有效消除了时钟抖动与偏移;布线时差分对时钟线严格按照差分等长和信号完整性处理,禁止信号线弯折和过孔穿越。

2.2 GTP_DUAL电源设计

在一个使用GTP收发器的FPGA设计中,传输链路的整体性能除与参考时钟源至关重要外,还高度依赖于供电电源的质量,手册要求采用专用电源,禁止与其他数字和模拟电路混用相同的电源,但单片或多片FPGA的GTP_DUAL之间可共享同一组电源。本设计采用二次降压变换POL方式为GTP_DUAL供电,低纹波线性稳压器选用TI公司的TPS74401,该芯片具有1%精度0.8V到3.6 V可调输出,满载电流为3 A时有115mV的超低压降以及优越的瞬态响应和过流、过热保护,供电纹波抑制比PSRR在1KHz时优于70 dB、超低输出噪声、软启动时间可编程等优点。通过调整反馈端分压电阻阻值,可为GTP方便的提供1.0 V和1.2 V电压,同时为了抑制各种高频噪声,在GTP_DUAL的每一个电源输入端连接了LC滤波网络进行滤波。

图2 外部专用管脚时钟驱动

3. 设计实现与测试

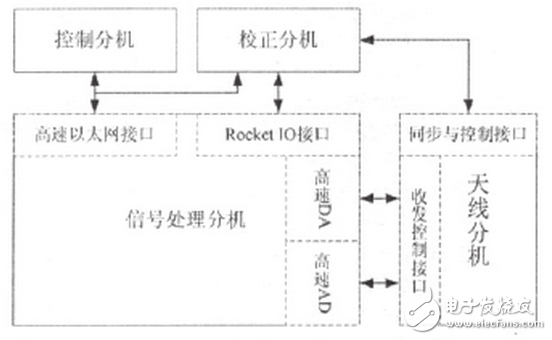

在某信号处理系统中,信号处理分机通过高速以太网接口收到控制分机命令后控制收发开关接口使系统处于接收与校正状态,通过高速AD将采集到的天线信号经RocketIO接口送给校正分机,根据接收数据的处理结果调整和控制天线参数,达到系统指标要求后使天线进入正常工作状态。系统组成框图如图3所示。

图3:系统组成框图

首先系统上电后,各分机做自身初始化与配置,建立所需各种通信连接,对RocketIO通信接口部分,本设计采用16比特数据位宽、使能8B/10B编码、并行端口数据速率80M、使能预/去加重和均衡、传输速率1.6Gb/s的设置。由于RocketIO接口只是提供了物理层的传输,对多通道、多链路、控制和反馈信息丰富的复杂通信模型,需要复杂和完善的通信协议来实现高可靠的数据传输,如PCI-E、千兆以太网、SATA、Aurora、RapidIO协议等;对简单的数据传输场合,用户可基于自定义协议、无反馈的实现数据的高效传输。本系统采用自定义协议方式,在每1KB数据中插入一个控制字符,做为同步和控制用途,传输信道具有低冗余和低开销的特点。测试过程中分别采用通过高速背板和射频电缆两种方式发送数据,在对多种预/去加重比尝试情况下,得到了很好的眼图和误码率。

由于并行数据位宽为16比特,测试中发现对于采用异步时钟(数据中嵌入时钟)方式时,数据的高/低字节易发生错位错误并且错位方式无明显规律,这是由于通信双方接收数据的起始边界不固定引起的,通过多次搜索同步控制字符找到正确边界,或发送训练字符串可解决此问题;另外,收发双方采用同源参考时钟,能更好、更快的解决此问题。通过Xilinx提供的专用误码率测试软件IBERT实测表明,采用长度为1.2米的等长、SMA接头的差分稳相射频电缆连接方式时,本设计系统在1.6Gb/s传输速率下误码率性能优于10e-12,采用高速背板连接时,达到了同样的误码率指标。

4.结束语

针对现代电子系统中数据传输速率不断增高的现状,设计了以Vritex-5 FPGA平台下的RocketIO GTP收发器为物理层的高速数据传输系统。它是基于嵌入式时钟同步方式,保证了吉比特数据传输速率可靠性,同时降低了系统互联的复杂度和功耗。基于标准协议的模型可保证数据的无丢失传输,而基于自定义协议方式的模型则有利于最小延时传输,其可靠性已经得到验证。

-

RocketIO高速串行接口2014-03-01 0

-

FPGA GTP收发器设计指导2016-08-25 0

-

RocketIO TM GTP在串行高速接口中的位宽设计2018-12-11 0

-

FPGA高速收发器设计要遵循哪些原则?2019-08-07 0

-

在Virtex-5/6 GTP / GTX收发器中如何实现JTAG2020-06-18 0

-

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?2021-05-25 0

-

RocketIO收发器怎么实现高速通信?2021-05-26 0

-

基于RocketIO的高速光纤红外图像串行传输的实现2010-09-22 458

-

基于FPGA的高速串行传输接口研究与实现2010-09-22 500

-

基于RocketIO的高速串行协议设计与实现2010-09-22 419

-

说说赛灵思(Xilinx )的FPGA 高速串行收发器2017-02-11 5980

-

如何在spartan-6 FPGA中使用GTP收发器的详细资料说明2019-02-15 1385

-

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器2020-11-20 17881

-

基于Virtex-5 RocketI0TM GTP收发器实现串行高速接口的开发应用2021-06-24 2548

全部0条评论

快来发表一下你的评论吧 !