对Vivado多周期路径约束的诠释

FPGA/ASIC技术

描述

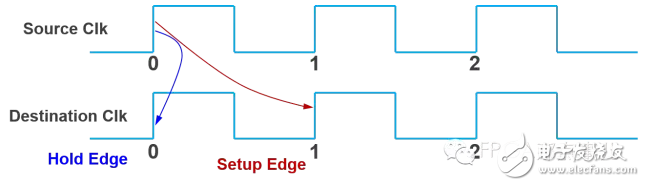

我们先看看单时钟周期的情形,如下图所示。红色标记为默认情况下的建立时间检查,蓝色标记为默认情况下的保持时间检查,且注意保持时间的检查是以建立时间的检查为前提,即总是在建立时间检查的前一个时钟周期确定保持时间检查。

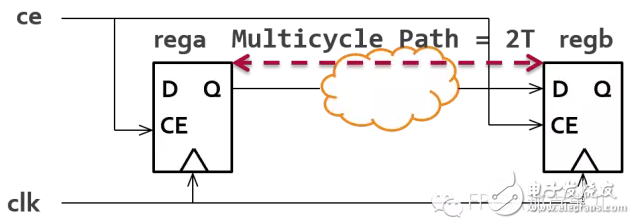

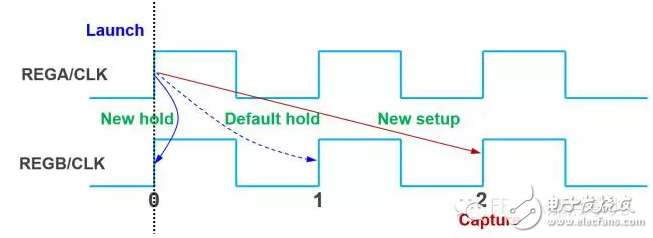

如果是多周期,如下图所示,此时两个寄存器之间尽管使用同一个时钟但因为使能信号的作用,使得两者数据率变为时钟频率的一半,意味着发起沿和捕获沿相隔2个时钟周期。

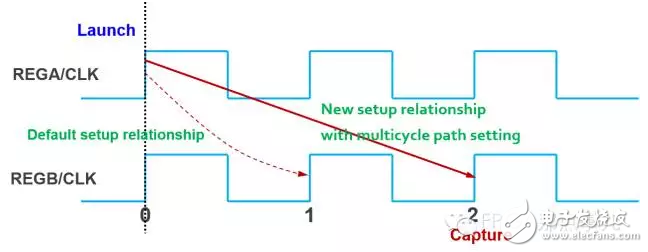

此时新的建立时间检查如下图中的红色实线所示,红色虚线为默认情况下的建立时间检查。

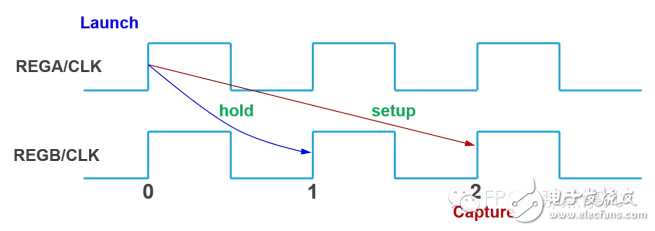

在此基础上,保持时间的检查变为下图中的蓝色实线(建立时间检查前移一个时钟周期)。

但显然,此时的保持时间检查是不对的,可想象一下,如果是一个时钟频率为原始时钟频率的一半的时钟,保持时间检查应该如下图中的蓝色实线所示。

多周期路径的约束我们会用到set_multicycle_path,这里我们结合上述分析重点介绍一下相应参数的含义:

*语句中数字的含义:

对于-setup:表示该多周期路径所需要的时钟周期个数;

对于-hold:表示相对于缺省捕获沿(图中的Default hold),实际捕获沿(图中的New hold)应回调的时钟周期个数;

*参考时钟周期的选取:

-end表示参考时钟为捕获端(收端)所用时钟,对于-setup缺省为-end;

-start表示参考时钟为发送端(发端)所用时钟,对于-hold缺省为-start;

setencells [get_cells -of_objects [get_pins -leaf –filter\

{IS_ENABLE==1} -of_objects [get_nets CE]]]

set_multicycle_path-from $encells -to $encells -setup 2

set_multicycle_path-from $encells -to $encells -hold 1

-

ISE多周期时序约束2015-04-30 0

-

设计中的关键路径如何约束2019-04-08 0

-

不同时钟域之间的多周期路径2015-03-17 0

-

vivado约束参考文档2018-09-26 0

-

Vivado生成的XDC约束的严重警告2018-11-02 0

-

VIVADO从此开始高亚军编著2020-10-21 0

-

Vivado时钟分组约束的三类应用2017-02-08 923

-

ISE约束导入vivado总共分几步2017-03-24 8568

-

Vivado中XDC文件的约束顺序2021-10-13 6358

-

vivado多时钟周期约束set_multicycle_path使用2021-12-20 962

-

VIVADO时序约束及STA基础2022-03-11 8823

-

Vivado设计约束功能概述2022-06-30 2968

-

关于多周期路径约束2022-12-10 824

-

FPGA时序约束之伪路径和多周期路径2023-06-12 978

-

如何在Vivado中添加时序约束呢?2023-06-26 2180

全部0条评论

快来发表一下你的评论吧 !