Vivado时钟的两大特性

FPGA/ASIC技术

描述

时钟延迟(Clock Latency)

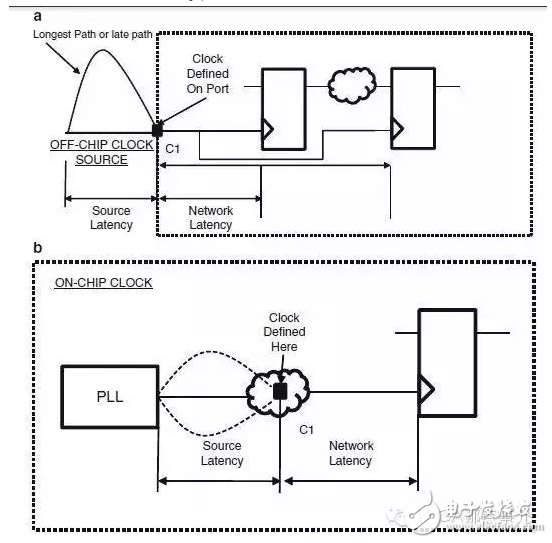

FPGA内部时钟通常由外部时钟源提供,经过PLL/MMCM生成内部所用时钟。从时钟源比如晶振或者上游芯片经过板级走线到FPGA的专用时钟管脚,这个过程必然有板级走线延迟;由create_clock定义的时钟端口到同步原件的时钟端口也必然有延迟。这两类延迟共同构成了时钟延迟,前者为时钟源延迟(Source Latency),后者为时钟网络延迟(Network Latency)。两者的关系如下图所示。

对于时钟网络延迟,Vivado为自行分析计算。对于时钟源延迟,可通过set_clock_latency来定义。如下Tcl脚本所示。

# Minimum source latencyvalue for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source-early 0.2 [get_clocks sysClk]

# Maximum source latencyvalue for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source -late 0.5 [get_clocks sysClk]

时钟的不确定性(Clock Uncertainty)

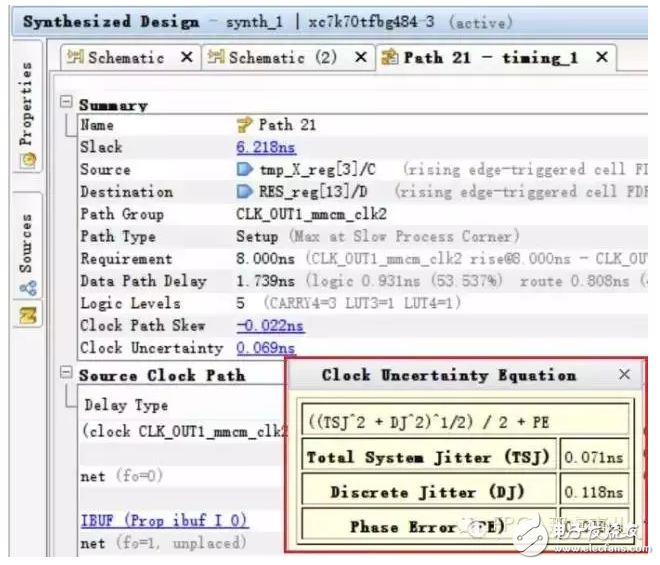

我们先看一下时钟不确定性的计算公式,如下图红色方框所示,在Vivado中打开时序路径,选中其中的Clock Uncertainty后面的数据,点击即可出现明确的计算公式。

这个公式表明,时钟的不确定性主要的构成因素为时钟抖动,包括输入抖动(Input Jitter)和系统抖动(System Jitter)。时钟抖动的具体概念可形象地用如下图表示,时钟周期为10ns的理想的时钟上升沿应该在0ns,紧邻之的下降沿应该在5ns,但因为抖动,上升沿可能会出现在0.1ns,下降沿出现在5.1ns。

在Vivado中可通过set_clock_uncertainty来设定时钟的不确定性。如下Tcl脚本所示。

set_clock_uncertainty-setup 0.213 [get_clocks wbClk]

set_clock_uncertainty-hold 0.167 [get_clocks wbClk]

设定时钟的不确定性的一个好处是可以在时序分析时时序过约束,而避免直接修改时钟周期。

-

Vivado:行业首款 SoC 增强型设计套件最新消息2019-08-01 1881

-

晶振良好的温度特性两大利势2013-12-17 0

-

怎么改变vivado性能2019-04-25 0

-

为什么Vivado没有在CCIO的同一时钟区域选择MMCM?2020-07-16 0

-

伺服电机有哪两大类别2021-06-28 0

-

嵌入式主板比较常见的两大类2021-12-16 0

-

与ARM相比较,Thumb代码的两大优势是什么2022-11-02 0

-

Vivado时钟分组约束的三类应用2017-02-08 923

-

如何使用Vivado IP Integrator组装具有多个时钟域的设计2018-11-27 3557

-

数字设计之时钟约束和时钟类型介绍2020-11-29 5442

-

详解Vivado时钟的基础知识2022-04-20 8054

-

Vivado 2022.1的新特性2022-07-03 1853

-

Vivado 202x-Versal时钟校准去歪斜的时序问题2023-07-07 375

-

Vivado Design Suite用户指南:I/O和时钟规划2023-09-13 119

-

如何禁止vivado自动生成 bufg2024-01-05 582

全部0条评论

快来发表一下你的评论吧 !