加速器一致性接口

FPGA/ASIC技术

描述

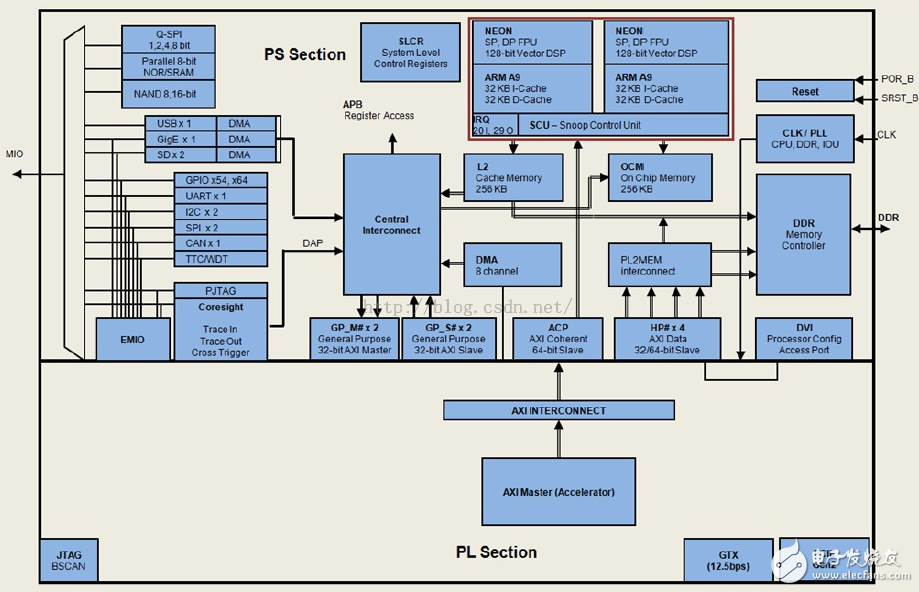

Zynq PS上的加速器一致性接口(Accelerator Coherency Port, ACP)是一个兼容AXI3的64位从机接口,连接到SCU(Snoop Control Unit),为PL提供异步缓存一致性直接访问PS的入口。

处理器可以标记ACP上的传输为一致性或非一致性。PL端的AXI主机通过ARUSERS[1:0]指示是否为一致性读传输,通过AWUSERS[1:0]指示写传输,这几个信号都是AXI总线相关信号。设备端或强烈要求顺序传输的情况常常按照非一致性传输对待(这些情况是指由AXI主机接口产生的传输,他们不被缓存,常常产生固定尺寸和数目的传输)。

【简介】

非一致性传输直接经过SCU,出现在AXI主机接口保持不变。

ACP从机的一致性传输到AXI主机会变为或多或少传输,一些属性会随之变化。

当ACP收到来自外部主机的一致性写请求时,SCU检查CPU内核L1数据缓存中相应地址,如果命中,一致性协议清空并invalidate 相应cache行,并合并清掉的数据和写请求。

从外部主机箱一致性内存区域发起读请求时,与SCU交互,测试是否需要数据已经存入处理器L1 Cache,如果命中,SCU直接向请求方返回数据;如果miss,SCU检查先L2 cache,再不然访问主存。

【ACP请求】

ACP一致性读请求:当ARUSER[0] == 1,ARCACHE[1] ==1,同时ARVALID有效时,产生ACP一致性读请求。这时,SCU强制一致性。

当ARUSER[0] == 0 或ARCACHE[1] ==0,同时ARVALID有效时,产生ACP非一致性读请求。这时SCU并不强制一致性,读请求直接传递到可用的SCU AXI master口通向L2 Cache控制器或OCM。

ACP一致性写请求:当AWUSER[0] == 1且AWCACHE[1] == 1,同时AWVALID有效时,产生ACP一致性写请求。这时SCU强制一致性,当数据存在于某个Cortex-A9处理器中时,PS区域逻辑首先清除并invalidate相应CPU的数据。当数据不在任一个CPU,或者当已经清掉、invalidate,则写请求通过某个Cortex-A9处理器的AXI主机接口发起到L2 Cache或主存。

当AWUSER[0] ==0 或AWCACHE[1] ==0,同时AWVALID有效时,产生ACP非一致性写请求。这时SCU不强制一致性,写请求直接传递到某个可用的SCU AXI master port。

【ACP的限制】

一致性访存不允许互斥访问;

一致性访存不允许锁定访问;

写传输,以length = 3, size = 3, 写选通11111111会引起CPU cache line破坏;

通过ACP连续访问OCM可能会饿死其他AXI主机;限制burst size小于8 x 64bit字。

【参考文献】

Zynq-7000 EPP TRM(UG585)

The Effect and Technique of System Coherence in ARM Multicore Technology by John Goodacre, Senior Program Manager, ARM Processor Division

ARM Cortex-A9 MPCore TRM, section 2.4, Accelerator Coherency Port

- 相关推荐

- 加速器

-

相位一致性边缘检测2014-06-11 0

-

一致性测试2017-07-14 0

-

c6678cache一致性2018-06-24 0

-

CAN一致性测试—容错性测试2018-11-22 0

-

LTE基站一致性测试的类别2019-06-06 0

-

混频器/变频器一致性测量特点介绍2019-07-18 0

-

一致性非锁定读分析2019-09-17 0

-

MIPI一致性测试2019-09-26 0

-

Infiniium一致性测试软件2019-10-28 0

-

什么是霍尔元件的一致性2020-10-12 0

-

为什么需要进行WiMAX协议一致性测试?2021-04-15 0

-

如何确保蓝牙设计通过EMI一致性测试 ?2021-05-07 0

-

如何实现信号电压幅值的一致性?2021-05-20 0

-

顺序一致性和TSO一致性分别是什么?SC和TSO到底哪个好?2022-07-19 0

-

ARM MPcore系统中ACP(加速器一致性接口的 )应用场景如何配置2022-09-08 0

全部0条评论

快来发表一下你的评论吧 !