利用捷变收发器来简化SDR平台设计复杂度并提高实际运算效能

FPGA/ASIC技术

描述

有鉴于软件定义无线电(SDR)平台是实现5G等先进通讯系统不可或缺的工具,半导体厂推出专为SDR应用量身打造的新一代捷变(Agile)收发器射频芯片,其整合模拟讯号处理与强大滤波功能于小巧且低功耗组件中,可大幅简化SDR平台设计复杂度并提高实际运算效能。

对于成功且实时的捷变(Agile)无线电收发器设计而言,高性能、宽带优化转换器及相关的高速现场可编程门阵列(FPGA)是必要的元素,但是许多设计者还需要额外的资源;由于组件有其复杂性,所以独立运作或是接近独立运作的方式不再可行,起因是内部连结的格式与通讯协议,以及电路板布局的细微之处所致。

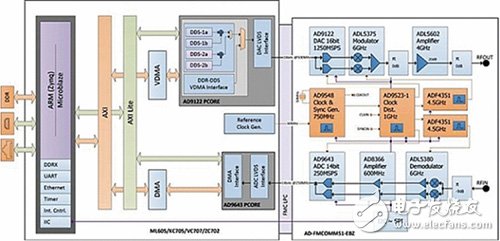

软件定义无线电(SDR)平台通常需要多项技术才能真正建立出一个完整的解决方案,其中包括射频(RF)与模拟数字转换器(ADC)设计、数字硬件、系统单芯片(SoC)汇编语言、数字信号处理器(DSP)硬件,以及软件开发技术等;要克服这些技术落差的其中一个方法就是使用参考设计及支持工具(图1),例如可以在完成一项工作范例时提供协助的MATLAB。

图1 RF开发工具--FMCOMMS1-EBZ的模拟前端适用于宽广范围运算密集,以及以FPGA为基础的无线电应用,包括SDR在内。在与FPGA开发平台结合时,该RF开发工具能够实现从基频到RF的各种物理层的无线通信功能。

SDR借力参考设计 滤波器设计挑战有解

举例来说,有一项常见的SDR挑战就是设计可编程滤波器。在SDR平台当中有可编程的TIA滤波器、低通滤波器、数字半波段滤波器,以及可编程有限脉冲响应(FIR)滤波器,而每个滤波器都会对组件链当中的下一个滤波器造成冲击;因此当某项功能不能运作时,设计者会发现很难找到问题所在。

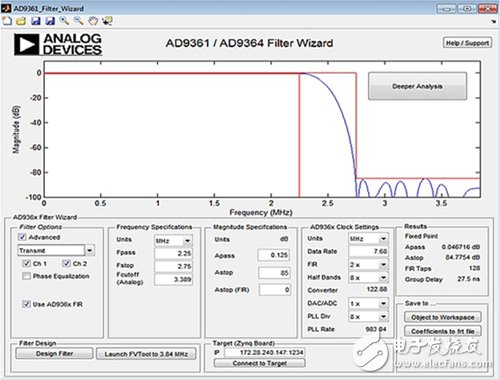

使用参考设计时,设计者可以看到不同的滤波器级并了解每个滤波器级如何在通带中产生出独特的振幅下滑与群组延迟,了解独特的振幅下滑与群组延迟是如何发生以及发生于何处之后,设计者可以针对FIR滤波器当中的延迟加以补偿,并在数字基频装置中建立一个平坦的频带响应(图2)。

图2 SDR系统功能方块图

另一项设计者所将面临的挑战就是如何设计FIR滤波器,使其能够针对前面各级累积的所有影响而加以补偿。针对此一需求,有一个小型的滤波器设计MATLAB App(图3),可以用来设计发射器与接收器FIR滤波器,协助设计者将来自于滤波器链中其他模拟与数字级的强度,以及相位响应纳入计算。

图3 由MathWorks所开发的MATLAB,可以应用于无线SDR系统与组件中复杂滤波器的设计。

透过挑选具备合适规格的组件,来获得评估工具、应用支持、参考设计,以及第三方知识与产品,开发团队将更有可能符合他们的多重设计目标,以及成本与时间指标。

无论系统工程师较喜欢使用FMC或是商业用的SDR平台,藉由支持工具与资源所获得的好处将会使系统工程师赢得先机。

新型收发器实现次世代SDR平台

值得注意的是,大量无线标准各有其不同的频率、带宽、通讯协议、格式,虽为使用者带来前所未见的连结与存取能力,但这同时也代表无线系统工程师在设计或是调查问题、性能、选项时,将会面对严苛挑战。

然而,解决方案似乎显而易见,即是将专用型硬件的使用降至最小,并且以SDR取而代之,尽可能的执行和管理大部分的发射与接收功能。现今的高性能、低功率处理器(包含FPGA在内)以及它们高速执行复杂算法则的能力,已经让实时执行方案得以实现。

但是上述解决方案有一项挑战,毕竟要针对接收器与发射器讯号路径设计宽带模拟电路是相当困难的;因此大部分的宽带SDR会使用一组重迭、并联的模拟通道,其分别针对总体波段中的特定部分予以优化,并具有能够和每个区段中所需讯号匹配的带宽,虽然这种方法在技术上颇具效率,但是它需要大量的硬件、印刷电路板空间、电力,以及必然的成本。

这就是Epiq Solutions在开发最新的SDR单元--Maveriq多信道可组态重设RF收发器时所面临的挑战(图4),该收发器结合了多重RF收发器先进平台、记录数据的固态硬盘(SSD)、执行Linux的内建Intel x86 CPU,以及使用于高速数据存取的Gigabit以太网络接口。

图4 Maveriq多通道可组态重设RF收发器

该装置以小巧的机体提供强大的SDR能力,并且涵盖了100MHz-6GHz的调整范围。身为设计者与建构者,该公司对于作为关键任务应用装置的可组态重设无线电系统的目标,便是提供比目前的Matchstiq SDR具备更强而有力的多通道版本。

尽管具有先进的特点与能力,Maveriq却是一款可携式的低功率平台,不同于先前的解决方案需要大量而且繁重的硬件组态设定,Maveriq结合了随时可运作的专门软件应用程序的函式库,可以立即应用于解决具挑战性的讯号处理需求,包含对来自于基地台与移动电话的蜂巢式无线电讯号的扫描与译码,将宽带RF记录到内部硬盘当中与RF重放,以及执行2×2多重输入多重输出(MIMO)波形。

Epiq的工程师之所以能够将许多的性能集结在一个小巧而且低功率的单元中,其所仰赖的就是亚德诺(ADI)的新IC--AD9361 RF捷变收发器,该组件乃是针对SDR应用领域所特别量身打造的。依据Epiq的执行长与系统架构师John Orlando表示,AD9361提供了必要的RF弹性与整合性,使该公司得以实现次世代的SDR平台。

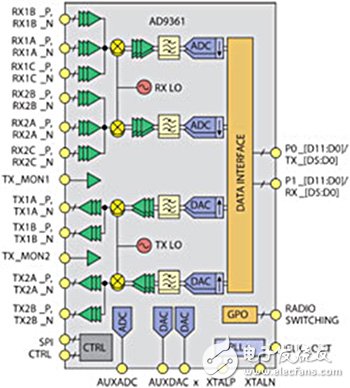

这款10×10毫米(mm)芯片等级的组件具有双重独立信道,如图5所示,带宽可以在200kHz-56MHz间调整,12位的模拟/数字(A/D)与数字/模拟(D/A)转换器也能够以高达61.44Msps的速度运作,并具备其他在建构横跨70MHz-6GHz之讯号链时所必须的特点与性能。

图5 RF的捷变收发器IC方块图

关键性的作业参数都是用户可以在作业中调整的,藉以和应用装置之需求达成优化的匹配;使用上述组件可以降低整个模拟前端(AFE)的总体基底尺寸,同时又可以使这种设计的功率耗损维持在1瓦的区间内,而保持在产品电力预算内是相当重要的。

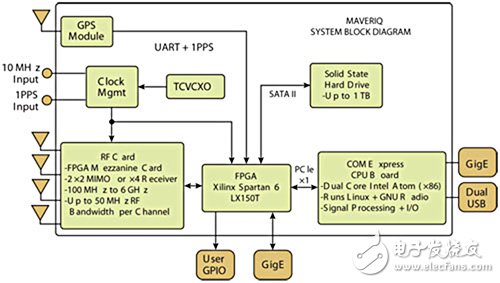

整个Maveriq单元,如图6所示,藉由一对AD9361支持2×2 MIMO或是四通道接收器组态设定,可具100MHz-6GHz的RF调节范围、1kHz的步进大小,以及2毫秒(msec)的调节时间,并包含一组具有1PPS性能的整合式全球卫星定位系统(GPS)接收器,而高达1TB的内部SSD则可支持100+MB/sec的数据持续记录,以及用来链接至外部系统的Gigabit以太网络。

图6 Maveriq单元的简化版系统方块图

处理功能的中心为执行Linux的双核心Intel x86 CPU,再加上负责讯号处理任务的FPGA,以及运行时可加载/可执行的软件应用程序,而这些全都能够针对客户应用而以现有的软件开发工具包支持。整个单元的尺寸为9.1×6.6×1.7(23×16.7×4.3cm),重量为1.9磅(0.9公斤),功耗15W(依据FPGA与I/O使用量而定)。

当然,若没有适合的RF性能其处理能力也会不足。该接收器具有低于8dB的典型噪声系数,以及10dBm的典型IIP3。发射端性能参数(像是带宽、调整、以及速度等)与接收端的数字相互搭配,输出功率为+5dBm。

AD9361 IC是此项设计中具有关键性的推手,然而额外的改善也具有同等的重要性,如特定的应用装置须要将延伸RF性能下降至20MHz范围以及更低,而这已经超过了AD9361所能到达的范围。此外,RF组件(像是能够下降至20MHz运作的低噪声放大器)的挑选可能也会是一项挑战,特别是对于尺寸与功率有所限制的设计而言。

如果认为低功率处理搭配大量的内存,再加上高速数字I/O与链接性等方面(这些都是由摩尔定律所驱动)的进步就已经足以胜任小型的高性能SDR,那是把事情太过单纯化了;现实的状况是,使用于发射与接收路径两者的前端信道具有同等的重要性,而结合了模拟处理、滤波与转换的RF IC,不仅能够将算法的负担最小化,同时也可以尽可能的提高SDR的实际性能(图7)。

图7 透过该款RF捷变收发器,可以提高SDR的实际性能。 图片来源:亚德诺

- 相关推荐

- SDR

-

基于纹理复杂度的快速帧内预测算法2010-05-06 0

-

ADI发布首款同步射频收发器快速原型制作套件AD-FMCOMMS5-EBZ2014-08-07 0

-

RadioVerse生态系统中的宽带收发器2018-08-16 0

-

捷变频收发器AD936X的特点和优势2018-10-22 0

-

全面了解基于射频捷变频收发器AD9361的软件定义无线电解决方案2018-10-22 0

-

基于混合信号RF IC的宽带SDR设计方案2018-11-12 0

-

JEM软件复杂度的增加情况2019-07-19 0

-

RadioVerse生态系统中的宽带收发器分享!2019-09-17 0

-

Wi-Fi和RF捷变收发器在宽带无线应用方面有哪些优缺点?2021-03-10 0

-

高级RF收发器满足SDR应用的需求是什么?2021-05-19 0

-

如何利用集成收发器简化AISG控制系统设计?2021-05-25 0

-

时间复杂度是指什么2021-07-22 0

-

各种排序算法的时间空间复杂度、稳定性2021-12-21 0

-

DIY一个SDR HF收发器2022-07-14 0

-

业界首款采用射频收发器SDR快速原型制作套件2019-06-14 2847

全部0条评论

快来发表一下你的评论吧 !