UItraScale架构FPGA的高性能低功耗内存接口

接口/总线/驱动

描述

如果你正在为你的下一个设计项目考虑DDR4 SDRAM,这里有一篇全新的白皮书,你应该研读一番,题目叫做“UItraScale架构FPGA的高性能低功耗内存接口”(WP454)。很多下一代的系统将会需要具有更高带宽的DDR4 SDRAM,更低的系统功耗,或者对两者都有要求来满足系统级的目标要求。DDR4 SDRAM 是DDR3 SDRAM的提升和进化产品,但是当把数据从DDR3传输到DDR4时对内存控制器和内存的物理层提出了新的要求,因此要做很多的改变。这个全新的赛灵思白皮书(WP454)带你认识理解这些所做的改变,指导你能够成功的使用DDR4 内存的优越性能。

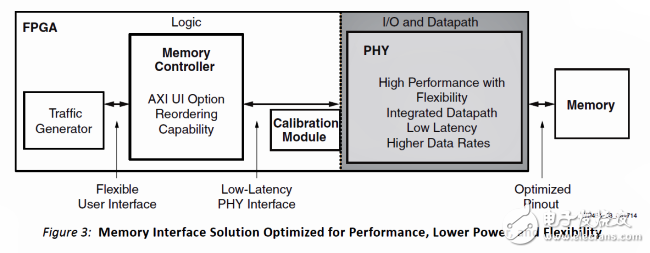

下面的这个模块框图展示的是可配置的UItraScale DDR4内存控制器和物理层结构,使用Vivado MIG(内存接口发生器)可以创建:

我们可以注意到DDR4内存控制器与内存物理层被一个低延迟的接口清晰的分离开,同时这个接口也用来连接这两个模块。分离的结构让你更加的简单容易的配置每个部件,根据你想要的方式精确的运用到你设计的系统中。同样我们还注意到有一个校准标定模块附加在DDR4 内存的物理层上---以后会更多的介绍这一点。

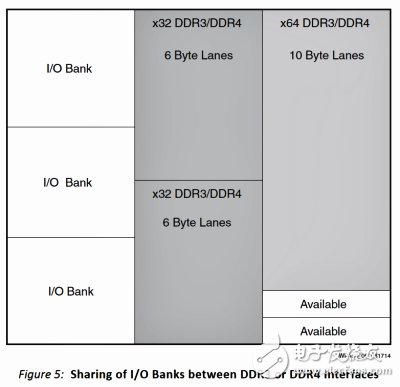

基于UItraScale架构的内存物理层的每个I/O模块由四个字节宽的物理层接口组成,外加两个专用的高速 Tx (发送数据)锁相环和一个MMCM(混合模式的时钟管理器 ),用来产生较高灵活性的时钟信号。这两个 Tx (发送数据)锁相环能够实现将每个I/O模块分成两个独立的内存接口,这就意味着你可以使用三个这样的I/O模块来创建两个32位(6字节)的DDR3接口或者创建一个64位(10通道)的接口,如下面的框图所示:

数字物理层是建立在通信协议的最底层,是为高速内存(包括DDR4 SDRAM)操作而设计的没有协议要求的物理层解决方案。没有通信协议的束缚意味着这个物理层支持DDR4 数据传输的速率,在能够满足FPGA I/O模块所要求的灵活性和可配置型的同时可以实现低功耗。

UItraScale内存控制器也已经为DDR4 SDRAM进行了优化。优化后的内存控制器集成了DDR4 SDRAM模组的优势来提高数据总线的效率,降低数据访问延迟。此外,增强的内存控制器,采用优化的命令队列结构,这样可以通过命令重新排序的方式提高带宽效率和通过使用批处理读取和写入事项更高速度的总线数据周转。软件控制器让你能够定制页面管理算法,在你的具体的应用设计中最大化DDR4 内存的带宽。

最后,关于DDR4校准的一些注意事项。这个UItraScale内存接口解决方案适用C程序精心DDR4内存的初始化和校准信息,运行在一个小型的赛灵思MicroBlaze软核处理器上,当然当我们使用Vivado 工具的内存接口控制器(MIG)的时候,C程序和MicroBlaze软核都会自动生成。

更多关于使用Vivado 设计工具集配置UItraScale内存控制器的信息,可以查看“UltraScale FPGA存储器接口解决方案产品指南”

更多关于赛灵思UItraScale架构器件DDR4的功能介绍信息,可以查看Xcell日报。“准备好DDR4-2400,需求带宽?需求低功耗?观看这个8分钟的视频吧。

© Copyright 2014 Xilinx Inc.

-

FPGA低功耗设计小贴士2015-02-09 0

-

低功耗DFM和高速接口2019-05-20 0

-

怎么实现低功耗单芯片高性能音频CODEC的设计?2021-06-03 0

-

基于ZU3EG的低功耗高性能嵌入式AI高性能计算模组2021-12-14 0

-

基于Cortex-A53架构的低功耗高性能处理器RK3328有哪些功能呢2022-03-09 0

-

统一工艺和架构,赛灵思28纳米FPGA成就高性能和低功耗的完2010-03-02 596

-

采用低成本FPGA实现高效的低功耗PCIe接口2013-02-26 986

-

一种高性能低功耗SEU免疫锁存器_黄正峰2017-01-08 730

-

汽车中的各种ECU,如何实现低功耗、高性能2018-01-03 17639

-

Microsemi 基于闪存FPGA架构低功耗SmartFusion2 SoC FPGA开发方案2018-05-14 7038

-

可提高性能并降低功耗的UltraScale架构2018-11-22 3120

-

莱迪思推出全新低功耗FPGA技术平台 带来低功耗、高性能的开发优势2019-12-11 942

-

Xilinx FPGA提供DDR4内存接口解决方案2020-05-28 4071

-

低功耗高性能DSP—C665x介绍2021-04-02 3064

-

设计低功耗和高性能的工业应用2023-11-16 90

全部0条评论

快来发表一下你的评论吧 !