SMC主机接口模块设计导入Xilinx环境

FPGA/ASIC技术

描述

SMC主机接口模块可轻松将通过Synphony模型编译器创建的设计集成在赛灵思嵌入式平台中。

Synphony模型编译器(SMC)是一款Synphony提供的、基于模型的工具,其可综合在Simulink®及MATLAB®中创建的设计,从而可为ASIC和FPGA目标应用生成优化的RTL。SMC包含一个综合而全面的高级模型库,可在Simulink环境中创建数学、信号处理及通信设计。该库可在高级模型设计环境中简化定浮点单速率或多速率算法的捕获及功能调试。SMC RTL生成引擎可使用这些经过验证的模型自动创建RTL,为占位面积、性能、功耗以及吞吐量利弊权衡实现多架构的硬件实施及快速探索。SMC的高级综合引擎采用顶级设计以及MATLAB语言输入,可生成针对所选硬件目标而优化的RTL。此外,SMC还可针对设计自动生成一个RTL测试平台,并配以比特及周期高精度的C模型与SystemC封装程序,可在SystemC仿真环境中实现对所生成硬件的验证。

在许多应用中,设计人员通过创建外设来执行一些信号处理功能,并必须通过主机处理器(例如赛灵思 MicroBlaze™软处理器内核)来配置该外设。主机处理器通常采用标准总线接口(例如AMBA® AXI4或AXI4-Lite)连接外设。SMC库包括主机接口模块,其可来实现主机处理器的从接口。该主机接口模块不仅支持AXI4-Lite、APB、通用接口以及Avalon-MM总线接口协议标准,而且还可通过实现必要的内存映射的寄存器来配置SMC设计,其中包括FIR滤波器系数、数控振荡器(NCO)的频率与相位设置以及各种长度FFT模块的FFT长度。此外,该主机接口模块在实现内存映射的控制寄存器时可以采用任意需要的采样频率,可以与总线接口时钟异步。您可在主机接口模块的UI中指定总线接口及存储器映射设置。设计人员可使用主机接口模块将SMC设计连接至总线互联或者总线主控。

现在我们来详细了解一下,如何将通过SMC主机接口模块设计的外设导入并集成到赛灵思嵌入式开发套件(EDK)项目中。此外,我们还将考证如何仿真通过标准总线互连连接的从MicroBlaze主机处理器到外设的AXI4-Lite总线的数据传输。该过程有四个主要步骤:

1. 使用IP、主机接口模块以及SMC RTL生成引擎在Simulink中创建外设,为设计生成优化的RTL实施方案;

2. 将该外设导入赛灵思EDK工程,并将其与余下的设计集成;

3. 在SDK中开发软件应用;

4. 生成RTL并对其进行仿真,以检查软硬件功能是否正确。

第1步:使用SMC库创建外设

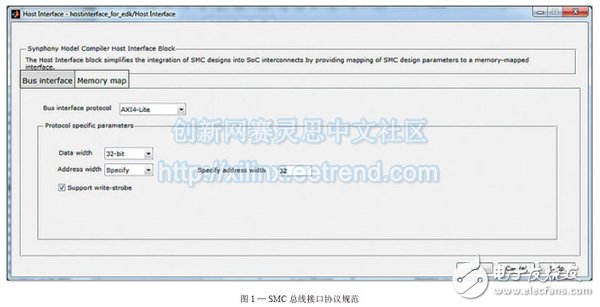

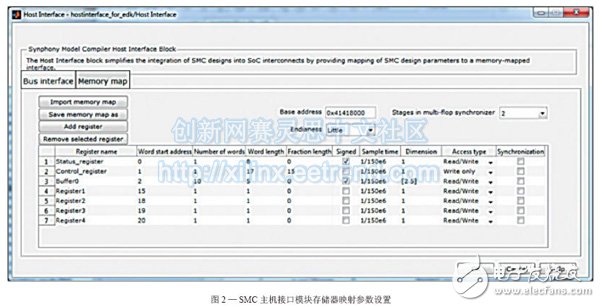

您要做的第一件事是使用SMC库模块创建外设的算法实施,并验证功能性。然后根据两个因素配置SMC主机接口模块:算法部分的配置数据(其可定义存存储器映射参数)与系统的互联总线协议(其可定义总线接口参数)。然后将主机接口模块与外设算法部分联系起来。主机接口模块的一些参数(例如总线互连、地址宽度与基址)将取决于您的目标平台。例如,我们选择赛灵思Virtex®-7 FPGA作为平台,并选择AXI4-Lite作为总线接口。该平台对每个外设的地址宽度、基址以及地址空间都有一定的限制。地址宽度必须为32位,而基址必须为4K字节的倍数,最小可用地址空间为4K字节。图1和图2是总线接口协议及存储器映射如何使用主机接口模块进行配置的视图。

为了便于集成,虽然不是强制性的,但也强烈推荐SMC模型中的总线接口端口遵循赛灵思EDK要求的命名惯例。请为标准AXI4-Lite接口信号名称添加“S_AXI_”。例如,AXI地址编写通道(AWADDR)的地址信号应该命名为S_AXI_AWADDR。如果信号不遵循AXI4-Lite的命名惯例,则在外设导入赛灵思EDK时就有可能将端口名称映射到AXI4-Lite信号名称上。另外,Simulink模型名称中不要使用大写字母,因为EDK不支持其名称中带有大写字母的外设。

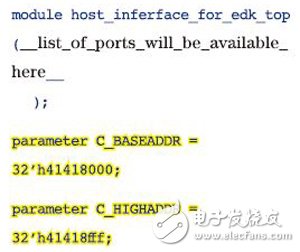

添加、配置和连接主机接口模块后,就可使用SMC的RTL生成引擎为外设生成RTL。请在SMC UI中指定目标设备、实施参数和优化限制,以促使RTL生成引擎为目标设备生成优化的硬件。在SMC生成的顶级RTL中添加两个虚拟参数(顶层RTL一般为VHDL),命名为:“C_BASEADDR”和“C_HIGHADDR”。根据IP要求将其默认值分配给存储器映射空间的基址和存储器映射空间的最大地址。这一步必需确保EDK可识别外设的存储器映射地址空间。SMC生成型设计的顶级Verilog RTL的实例如下所示,有两个参数需要高亮显示。

为了便于集成,虽然不是强制性的,但也强烈推荐SMC模型中的总线接口端口遵循赛灵思EDK要求的命名惯例。

第2步:将外设导入赛灵思EDK并对其进行集成

下一步是将外设硬件导入EDK的赛灵思Platform Studio(XPS),并在系统中进行必要的连接(总线接口端口以及功能端口)。在本示例中,我们已经创建了具有MicroBlaze处理器的基本系统、用于存储可执行软件的模块RAM (BRAM)、本地存储器总线(LMB)、AXI4-Lite互连以及MicroBlaze调试模块。

在XPS GUI的硬件目录下选择“创建或导入外设”选项。这将打开创建并导入外设向导。在该向导中选择“导入现有外设”选项。然后指定外设的存储路径、设计名称以及文件类型(HDL)。现在添加所有SMC生成的RTL文件。成功编译RTL之后,您需要识别外设支持的总线接口,即AXI4-Lite从接口,如图3所示。

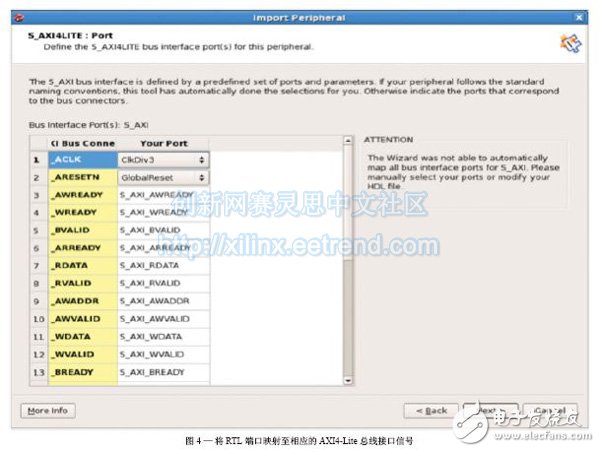

在向导的下一个页面中选择外设的AXI4-Lite端口,并将其映射到标准AXI4-Lite端口上,以便EDK能够连接总线接口。如果SMC模型中定义的总线接口端口名称与标准总线端口名称相匹配,则EDK将自动映射端口(参见图4)。

如果端口名称不匹配,则可能要覆盖自动映射,如AXI4-Lite时钟(Clk-Div3)和复位(GlobalReset)信号所示。

然后,按照第一步中插入RTL的C_BASEADDR和C_HIGHADDR参数,指定寄存器空间基址和高位地址。请取消选择存储器空间选项,因为主机接口模块具有可寻址的配置寄存器空间。但是在下个页面中要保持RTL参数的默认属性不变,以确保与主机接口模块中指定的参数一致。

下个页面的标题为“端口属性”。在这里,您必须指定时钟属性,或者所有其它时钟上的复位或设计中的复位。请点击下个页面中的“完成”,添加外设至XPS项目。SMC外设现已成功导入XPS。您可通过查看

/pcores文件夹(XPS使用外设名称在此创建一个目录)验证是否成功。浏览该目录,检查RTL文件是否正确导入。

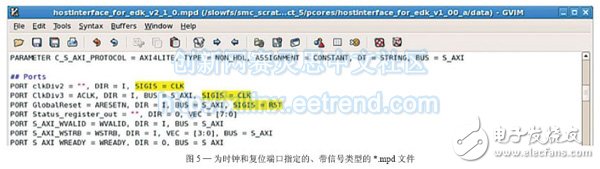

此外,XPS还将创建一个与HDL目录并列的目录,名为“数据”。该数据目录包含微处理器外设描述(*.mpd)文件以及相关外设参数及其端口信息。查看SIGIS = CLK和SIGIS = RST参数是否已在时钟及复位端口上定义。如果没有定义,则需要编辑*.mpd文件并手动添加定义。图5是添加了这些参数的文件实例。

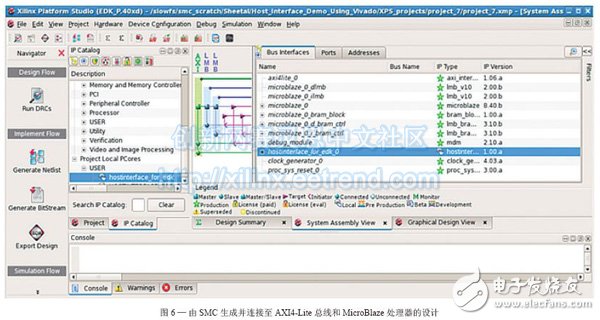

现在,您将在XPS GUI的IP目录部分看到您的外设位于项目本地PCores下的“用户”子目录中。请右键点击外设名称,并选择“添加IP”。XPS核心配置窗口将打开。不要编辑本窗口中的任何参数,保持默认设置不变,以符合赛灵思EDK流程。如果EDK不接受指定的地址空间,则代表指定的存储器映射与设计中的某些其它外设有冲突。您必须返回SMC,使用新的基址值重新生成RTL,并重复上述步骤导入SMC外设。当正确的基址及高位地址值可用时,请点击核心配置窗口中的“确定”按钮。XPS将打开“举例说明并连接IP”GUI。您既可命令工具自动链接外设与互联总线(由可用处理器驱动),也可选择手动连接外设。连接完成以后,就会看到图6中显示的接口连接。

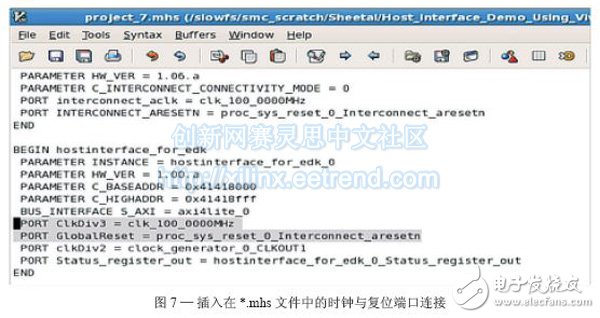

在图形设计视图选项卡中的总线接口连接中再次检查与AXI4-Lite相关的时钟与复位是否已连接。如果没有自动连接,请编辑中的微处理器硬件规范文件

.mhs。图7是添加了时钟与复位端口的*.mhs文件。

下一步,使用系统装配视图窗口的端口选项卡连接设计中的非AXI4-Lite端口。在系统装配视图的地址选项卡中,请确保外设地址空间可见,并确保地址范围已锁定。

现在,通过在XPS GUI的项目目录中选择“导出硬件设计至SDK”将硬件导出至赛灵思软件开发套件。如果你只想运行RTL仿真,则不需要生成比特流。完成后,XPS会创建一个*.xml文件,用以描述导入SDK的硬件。该文件一般会在

/SDK/SDK_Export/hw文件夹中创建。

第3步:使用赛灵思SDK开发软件驱动程序

集成的下个步骤是使用赛灵思SDK开发软件驱动程序。请启动SDK并创建一个硬件平台规范项目,以源出*.xml文件。如果已经在EDK中选择了“导出并启动”选项,则会自动创建该项目,而且IP模块和地址映射信息已在SDK项目中提供。

在创建板级支持包(BSP)之前,您必须为您的外设创建驱动程序文件。典型的驱动报头文件必须定义存储器映射的寄存器偏移地址以及读取和写入这些寄存器的原型。

将驱动程序文件复制到SDK项目资源库中,用以识别驱动程序并创建BSP项目。打开一个新的空白应用项目创建软件,然后从外设读取和写入数据。在该项目中,请指定按照该步骤第一个任务创建的硬件目标平台以及您刚刚创建的BSP。请在BSP设置窗口中查看设计的外设驱动程序内核。

应用项目包含一个main.cc文件,其中写有用于应用的软件代码。创建该文件后,SDK会自动编译代码,并创建一个*.elf文件,其可用于仿真RTL仿真环境中的软件代码。

应用项目包含一个main.cc文件,其中写有用于应用的软件代码。例如可将各种值写入存储器映射前两个寄存器(Status_register和Control_register)中的程序。创建该文件后,SDF会自动编译代码并创建一个*.elf文件,其可用于仿真RTL仿真环境中的软件代码。该*.elf文件随后可用于验证功能性,见第4步。

通过AXI4-Lite从接口使用主机接口模块将SMC生成的外设与赛灵思嵌入式平台集成非常简单。

第4步:在XPS中生成RTL文件

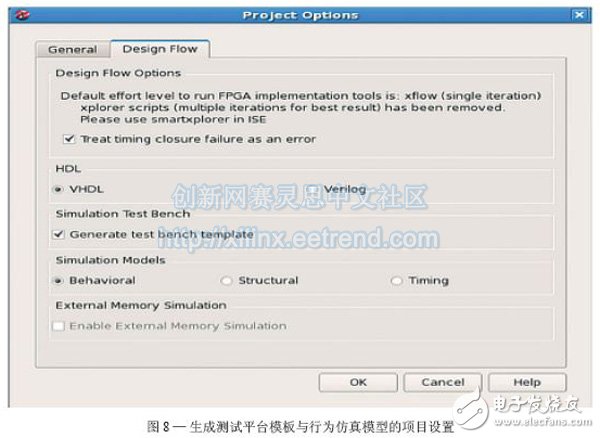

最后一步是在XPS中生成RTL,并对其进行仿真,以便验证软硬件功能是否正确无误。在XPS GUI中的项目目录下选择“选择Elf文件”选项,然后选择“选择仿真Elf文件”,以指定Elf文件(SDK创建的)的路径。该文件在应用项目文件夹中提供。要创建测试平台模板与行为仿真模型(参见图8),您需要在GUI的项目目录下选择项目选项的设计流程选项卡设置。

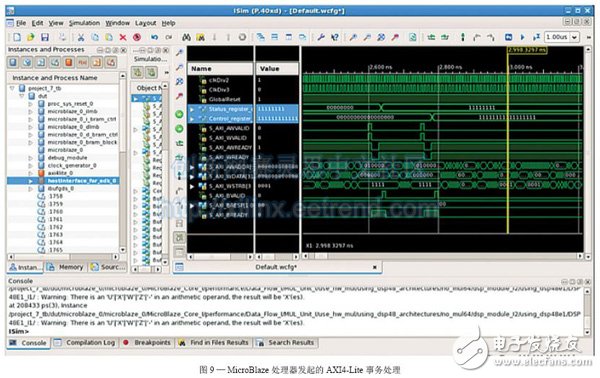

然后,通过选择“生成HDL文件”创建HDL文件,并启动ISE® (ISim)HDL仿真器,以检查功能的正确性。图9是MicroBlaze处理器针对SDK项目中的软件C代码发起的AXI4-Lite事务处理。请注意,外设的前两个寄存器(Status_register和Control_register)可根据计划改变其值。位于外设接口的相应AXI4-Lite信号显示,SMC创建的外设已经成功集成在嵌入式项目中。

强大的工具套件

通过AXI4-Lite从接口使用主机接口模块将SMC生成的外设与赛灵思嵌入式平台集成非常简单。SMC和赛灵思嵌入式平台的完美结合可带来一款功能强大的工具套件,能够帮助您设计和开发与主机处理器集成的DSP外设。SMC中的主机接口模块不仅可提供完成无缝集成所必需的接口,而且还可为嵌入式平台创建功能强大的解决方案。

-

【经验】蓝牙模块主机和从机透传2017-09-09 1373

-

教你如何搭建Xilinx开发环境2012-02-29 0

-

解决Xilinx ISE的license无法导入的问题2021-05-17 0

-

SMC1602的封装尺寸及接口信号说明2008-11-01 5065

-

USB接口控制器参考设计VHDL代码(Xilinx)2016-06-07 847

-

基于XILINX的SPARTAN板的VGA接口显示程序2016-06-07 631

-

e² studio开发环境之导入教程2018-07-23 2690

-

在Xilinx Zynq UltraScale+ MPSoC中实现的NVMe主机加速器2018-11-26 5718

-

SMC1602A显示模块的使用说明书2019-12-04 1323

-

基于CPU-319F组态的SMC模块介绍2020-09-08 2732

-

导入Python库失败的缺失库怎么解决2020-11-21 2677

-

如何通过CPU-319F组态一个SMC模块?2021-01-02 1909

-

组态一个PROFINET网络下的SMC阀导EX245模块2022-10-10 1918

-

import模块的导入方法2023-09-11 788

-

python如何导入模块2023-11-22 518

全部0条评论

快来发表一下你的评论吧 !