基于声纳探测技术的水下三维场景实时成像系统

FPGA/ASIC技术

描述

摘 要:针对目前水下三维声纳实时成像系统前端信号通道多、波束形成计算量大的问题,提出一种基于现场可编程门阵列(FPGA)的水下三维场景实时成像系统。采用FPGA 阵列控制多路信号同步采样,优化波束形成算法对海量数据进行并行处理,同时利用嵌入式处理器PowerPC 控制系统,最终由主控PC 完成三维图像实时显示。实验结果表明,该系统能够在水下200 m 的范围内实现分辨率为2 cm 的三维成像,三维图像刷新率可达20 帧/秒。

1 概述

近年来,随着人们对海洋资源的不断需求与开发,水下探测技术得到了飞速发展。人们对海洋的主要探测手段是声波,即声纳技术。因此,利用声纳进行水下探测成为了当今海洋研究的重点课题。然而,大部分声纳系统都是通过声波来判断有无声纳目标,以及目标的方位和距离。目前,国内外在海底三维声纳成像技术方面已经取得了一定的成果[1]。例如:美国RESoN 公司开发的新一代数字声纳SeaBat8125,欧洲共同体和挪威共同开发的Echoscope系列三维声纳,美国的海洋工业公司开发的双频识别声纳以及美国的Farsounder 公司开发的三维前视声纳[2-3]。我国三维成像声纳也得到一定的发展,中科院声学所、715 所和哈尔滨工程大学等单位等都研制了三维声纳成像系统的试验样机并发表了相关论文[4]。但这些声纳成像技术大多基于二维映射三维图像,或者小范围的慢速三维成像,成像效果不佳,实时性太差[5]。

本文提出基于三维声纳探测技术的水下三维场景实时成像系统,设计并实现48×48 路信号的同步采样,128×128 个空间波束形成的大规模数据处理和实时水下三维场景成像。

2 系统总体设计

2.1 系统技术特点

目前,实时高分辨率的三维声纳系统面临2 个问题[6]:

(1)大量前端信号通道的硬件成本昂贵;(2)进行波束形成算法所需的乘累加计算量大。

首先,该系统采用了优化后的模拟退火算法[7],对二维平面上的每一个换能器分配权重系数,在最大旁瓣可以接受的条件下,部分换能器的权重系数可以分配为0,即达到对换能器稀疏化,减小系统运算量的效果[8]。最终实现系统2 304(48×48)个换能器组成的声学信号接收平面阵。

同时,该系统采用优化后的分步波束形成算法,将空间入射的声波信号进行空间分解,对相移参数进行优化,从而减小相移参数储存空间,并将声学信号接收平面阵划分成48 条线性子阵,分组并行实现分步波束形成,最终完成128×128 个波束形成[9]。

由于FPGA 具有数据位宽可配置性、多级流水线处理以及内部集成大量的数字信号处理单元(DSP Slices)等特性,因此FPGA 在声纳信号处理方面的运算效率远大于数字信号处理器(DSP)的运算效率[10]。为了做到实时的海量数据处理,该系统采用了基于FPGA 平台的系统设计,利用FPGA 阵列对数据进行并行处理,并通过阵列间的数据交互完成波束形成。

2.2 系统总体构架

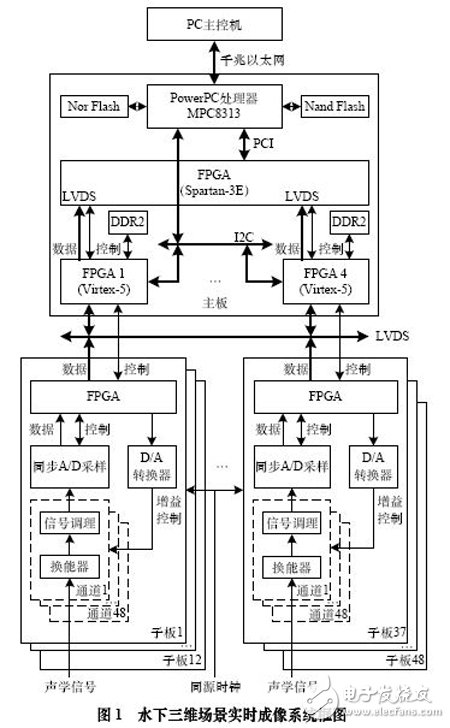

水下三维场景实时成像系统总体结构如图1 所示,由48 块子板、主板和主控PC 组成。子板负责完成信号采集功能,主板负责完成波束形成与数据汇总,并实现对子板的采样控制和与主控PC 通信的功能,最终在主控PC 上完成实时三维成像。其中,每块子板有48 个信号接收通道。

3 系统硬件设计

3.1 子板硬件设计

子板主要由输出放大器ADA4841、4 路功率放大器SSM2164、12 bit 串行AD 转换器ADS7886 和DA 转换器LTC2641、LTC1019、Xilinx Spartan-3E 系列FPGA XC3S1200E以及其他外围电路构成。

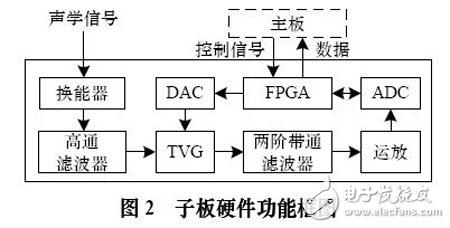

子板数据采集功能如图2 所示。各通道首先对从换能器接收的微弱的电信号进行调理,将信号通过一个高通滤波器滤除中低频的环境噪声后,再经过一款二阶带通滤波器,以实现当输入信号频率大于570 kHz 时使信号衰减20 dB 以上,同时保证有效的信号范围270 kHz~330 kHz(考虑水声信号的多普勒频移)衰减小于3 dB。然后在外部同源时钟驱动下,Spartan-3E 控制A/D 采样芯片对声学信号的幅度和相位信息进行同步A/D 采样和采样数据处理,并通过低压差分信号(Low-voltage Differential Signaling, LVDS)接口将数据上传主板。同时,Spartan-3E 通过串行外设接口(Serial Peripheral Interface, SPI)向D/A 转换器发送数据,经转换后输出时间增益(Time Variation of Gain, TVG)控制信号,以控制采样信号压缩比。

3.2 主板硬件设计

主板主要由1 片PowerPC 嵌入式处理器MPC8313、1 片Xilinx Spartan-3E 系列FPGA XC3S1200E 和4 片高性能Xilinx Virtex-5 系列FPGA XC5VSX95T,以及其他外围电路组成。

每块Virtex-5 通过LVDS 接口接收12 块子板上传的数据,通过高速差分对数据线彼此进行数据交互。每块Virtex-5对数据进行计算处理并完成波束形成,经2 片64 MB 外部DDR2 暂存,将波束形成结果上传至Spartan-3E 进行数据汇总。MPC8313 通过外设部件互连标准(Peripheral Component Interconnect, PCI)接口对Spartan-3E 中的数据进行读取,将波束形成汇总结果通过千兆以太网口传输给PC 主控机。同时,MPC8313 使用系统双线式串行(Inter-integrated Circuit,I2C)总线对Virtex-5 寄存器进行配置,生成D/A 驱动信号下发子板。MPC8313 外围扩展有Nor Flash 用于存储系统代码,Nand Flash 用于存储有效传感器的编号和相应的权重系数等系统相关数据。

4 系统FPGA 功能设计

系统各模块FPGA 设计是水下三维场景实时成像系统的核心,一共包括3 个部分:子板FPGA 设计,主板高性能FPGA 设计和主板接口FPGA 设计。

4.1 子板FPGA 设计

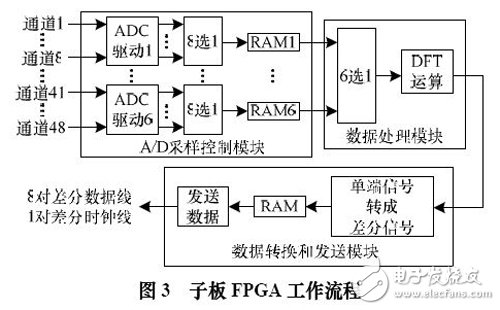

子板FPGA 主要完成ADC 芯片的控制、数据的采集、24 点离散傅里叶变换(Discrete Fourier Transform, DFT)运算与主信号处理板的通信等功能。如图3 所示,在子板FPGA中,A/D 采样控制模块从48 个通道串行读取数据,并分存在6 个大小均为6 KB 的双口RAM 内。数据处理模块按通道顺序,依次从6 个RAM 中读出24 个采样点,并对采样数据进行DFT 计算,计算得到一个频点为300 kHz 的DFT值。数据转换与发送模块按通道顺序读取DFT 计算结果,将单端信号转成差分信号,通过LVDS 接口将数据上传。同时FPGA 通过SPI 接口向D/A 转换器发送数据,经转换后的模拟信号输出TVG 控制信号,以控制采样信号压缩比。

4.2 主板高性能FPGA设计

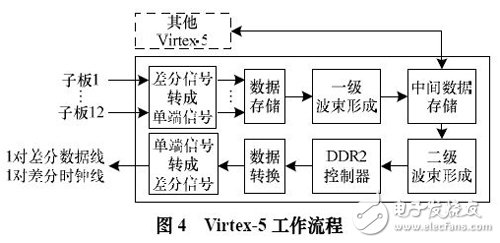

为了实现对48×48 路信号的大规模数据处理,最终完成128×128 个波束形成, 系统选择了高性能的Xilinx Virtex-5 系列FPGA。由于系统数据运算量很大,任何一块FPGA 都无法独立完成,因此根据最终形成的波束数,将采集数据平均分配给4 块FPGA 同步进行处理与计算,并通过彼此的数据交互完成波束形成,如图4 所示。

每块Virtex-5 从12 块子板接收数据后储存。一级波束形成模块从数据存储模块读取数据,计算形成12 条线性阵在一个方向上的波束,并将数据存储。一级波束形成的中间数据有1/4 结果被保留,其他3/4 通过自定义高速差分对数据线传递给其他3 块Virtex-5,同时每块Virtex-5 从其他3 块Virtex-5 得到中间波束。二级波束形成模块从中间数据存储模块读取数据,计算形成12 条线性阵在另一个方向上的波束。每块Virtex-5 共完成32×128 个波束形成。最终数据经DDR2 缓存,通过2 对差分传输线传输给主板接口FPGA。

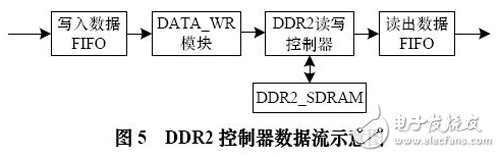

数据存储模块和中间数据存储模块都分配1 个双口RAM,1 个作为数据接收缓存的FIFO 和1 个作为数据发送的FIFO。DDR2 控制器由DDR2_WR 模块和FPGA 内部DDR2 读写控制IP 核组成,数据流如图5 所示。DDR2_WR模块按照一定的顺序从写入数据FIFO 中读出12 块子板的波束形成结果,并按照读取的先后顺序写入DDR2 中,读出数据FIFO 在写DDR2 操作的间隙从DDR2 中读出数据。

嵌入式处理器PowerPC 通过系统I2C 总线对每块Virtex-5 的寄存器进行读写操作,修改TVG 参数,并通过

Virtex-5 将TVG 参数发送给每块子板,达到对每个采样模块进行增益控制的功能。

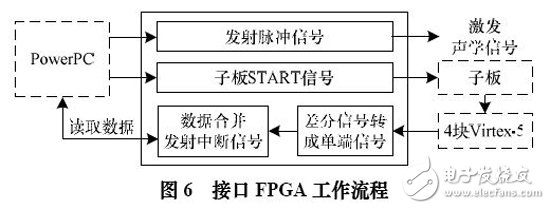

4.3 主板接口FPGA 设计

主板接口FPGA 负责将4 片主板高性能FPGA 上传的数据合并,便于PowerPC 读取。PowerPC 控制FPGA 生成脉冲信号,驱动系统发射声学信号,并通过FPGA 控制子板开始采集数据。数据汇总完成后生成中断信号,PowerPC根据中断信号读取数据。具体工作流程如图6 所示。

5 系统软件设计

系统软件设计分为2 个部分完成:(1)在PowerPC 上完成的嵌入式操作系统移植与应用软件开发;(2)在主控PC上完成的实时可视化显示系统设计。

5.1 PowerPC 软件设计

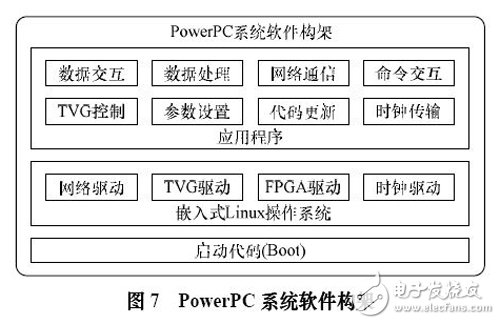

嵌入式处理器PowerPC 采用嵌入式Linux 操作系统为核心,完成整个操作系统的移植、系统启动代码开发、驱动程序开发和应用程序开发等多层次任务。系统构架如图7所示。

系统构架分为3 个层次:(1)完成系统Boot loader 开发,以及文件系统镜像、启动脚本等。(2)在操作系统上开发1 000 兆以太网驱动、TVG 驱动、FPGA 驱动、时钟驱动。(3)应用程序实现与主控PC 和主板等数据交互、数据处理、网络通信、命令交互、TVG 控制、参数设置、代码更新、时钟传输等功能。

5.2 实时可视化显示系统设计

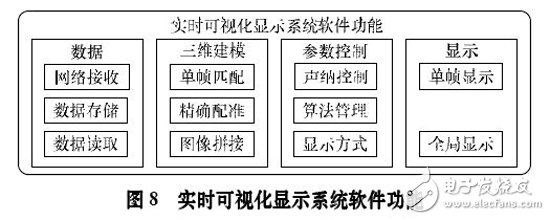

实时可视化显示系统的全部功能一共可以划分为4 个部分,如图8 所示。

数据模块通过网络接收相控阵上传的数据,一方面直接对数据进行实时可视化处理,另一方面将数据保存以用于离线处理。三维建模模块是本系统的主要功能模块,单帧匹配是将相邻点连接成三角面片,使点集形成拓扑结构[11]。精确配准是采用邻近点迭代(Iterated Closest Point,ICP)算法把点集摆放在更加合适的位置[12]。图像拼接是使输入的新帧与旧帧融合成一帧更加完整的图像。在参数控制模块分别对三维建模模块和显示模块进行参数控制。显示模块是将单帧匹配结果显示在小窗口中,将全局配准和拼接结果显示在大窗口中,各窗口皆具有交互显示功能。其中,参数控制模块包括声纳控制、算法管理和显示方式控制。声纳控制包括测量量程和采集模式控制,算法管理包括配准精度和拼接分辨率控制,显示方式包括配色方案和帧率控制。

6 系统性能

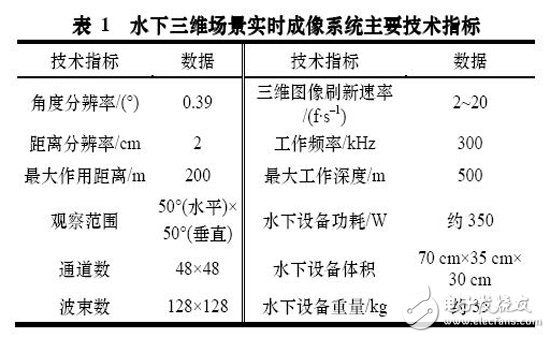

目前,水下三维场景实时成像系统试验样机的研制已完成,国内还没有相关的研究成果,国际上只有英国Coda Octopus 公司在2006 年推出的产品Echoscope Mark II[13]。表1 给出了试验样机的主要技术指标,该系统与Coda Octopus 公司Echoscope Mark II 产品的技术指标基本一致。其中,角度分辨率是指相邻2 个接收波束之间的夹角;距离分辨率是指同一接收波束上前后相邻2 个像素点之间的距离;最大作用距离是指反射强度为0 dB 的目标能被有效探测到的最远距离。

图9 为试验样机在浙江省千岛湖水声试验站采集到的湖底数据,可以清楚地从主控PC 用户界面上看到千岛湖湖底拼接效果图,其中有一条铁索沉在湖中。

7 结束语

本文提出的水下三维场景实时成像系统方案,基于优化后的波束形成算法,利用大规模FPGA 阵列,较好地解决了大量换能器信号采样和海量数据并行计算的问题。该系统在大坝水下部分监测、海港墙壁检查、水下工程实施、海底管道检查、水下航行器的避障和导航等方面具有广泛的应用前景。下一步将针对实际的应用,设计相应的优化算法,并在提高系统性能和降低系统功耗方面做进一步的改进。

-

如何使用labview根据XYZ坐标实时绘制三维曲线2014-04-12 0

-

三维触控技术突破“二向箔”的束缚2016-12-19 0

-

三维快速建模技术与三维扫描建模的应用2018-08-07 0

-

广西扫描服务三维检测三维扫描仪2018-08-29 0

-

电厂三维安全定位系统迎考察获盛赞2018-10-12 0

-

三维设计应用案例2019-07-03 0

-

三维立体成像X射线显微镜在元器件失效分析中的应用2019-08-31 0

-

怎么设计基于FPGA多波束成像的声纳系统?2019-10-09 0

-

结合三维可视化的智慧电厂方案设计2020-06-28 0

-

基于STM32的三维旋转显示平台设计(立体成像)!!!2020-08-27 0

-

三维可视化运维系统将成为未来趋势2020-09-03 0

-

三维可视化技术在生物质锅炉防磨防爆管理中的应用2020-09-17 0

-

三维可视化的应用和优势2020-12-02 0

-

上海黄浦三维媒体动画技术2021-06-30 0

-

基于激光差频扫描的水下三维图像2009-12-14 840

全部0条评论

快来发表一下你的评论吧 !