基于FPGA芯片的数据流结构分析

FPGA/ASIC技术

描述

摘要:Virtex 型FPGA 芯片是Xilinx 公司芯片系列中的一种,Virtex 系列的数据流及配置逻辑与XC4000 的数据流及配置逻辑有显著不同,但却与Xilinx 的FPGA 家族保持了很大的兼容性。这里详细介绍了Virtex 系列FPGA 芯片的数据流大小及结构。

1 引言

Virtex 支持一些新的非常强大的配置模式,包括部分重新配置,这种配置机制被设计到高级应用中,以便通过芯片的配置接口能够访问及操作片内数据。但想要配置芯片,对它的数据流结构的了解是必不可少的。在这里对Virtex 系列的数据流结构进行了一个概述,讲述每一个bit 在数据流中的位置,这对访问及改变片内数据是很重要的。

Virtex 系列的数据流可以看作是整块芯片的地址与数据所确定的点的集合,竖直方向为地址,水平

方向为数据,通过这个二维坐标所确定的点的集合便构成了整块芯片的数据流。而整块芯片的地址空间又被分为两种不同的块类型,一类是CLB 块类型,另一类是RAM 块类型。每一块类型地址中,又被分别分成若干的帧及相关的主地址、附地址等,在下面将具体讲述这些内容。

2 帧、块类型、主地址、附地址

2. 1 帧

Virtex 配置内存能以位的阵列形式显示。这里涉及到“帧”的概念,帧是配置的基本单元,它由位组成,宽度等于一位宽,长度等于芯片阵列的最顶端到最底端。帧是能从配置内存中读或写的最小部分。

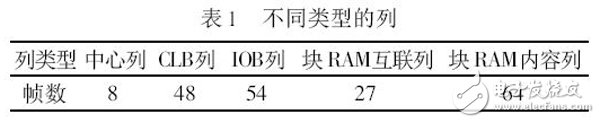

帧被组织成大一些的单元,称为列。在Virtex,Virtex - E 和Virtex - Eextended 内存器件中,有不同类型的列。如表1 所示。

每个Virtex 器件包含一个中心列,在中心列中包括全局时钟端口的配置; 两个IOB 列, IOB 列描述

了器件位于左边和右边所有IOB 的配置; 最多的列是CLB 列,CLB 列中包含这列的CLB 以及在这列CLB 的上面及下面所对应的IOB 的配置; 剩下两列类型为RAM 列: 一个为块RAM 内容列,另一个为块RAM 互联列。

2. 2 块类型、主地址、附地址

所有的地址空间被分成两种块类型: RAM 块类型和CLB 块类型。RAM 块类型只包含块SelectRAM内容列( 不包含互联) 。CLB 块类型包含所有其它列类型。

RAM 地址和CLB 地址又细分为主地址和附地址。每个配置列在RAM 或CLB 地址空间有一个唯一的主地址,每个配置帧在它的列中有一个唯一的附地址。

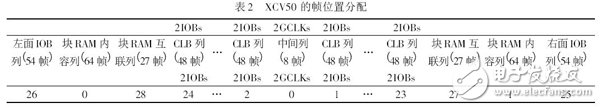

Virtex,Virtex - E 和Virtex - E extended memory器件的块类型和附地址有相同的编码顺序。不同系列器件的主地址编码顺序是不同的。但是在这两种系列中,都是偶地址在器件的左半边,奇地址在器件的右半边。CLB 地址空间以“0”开始于中间列,然后交替于器件的右半边和左半边,然后是IOB 列,最后是块SelectRAM 互联列。RAM 地址空间的“0”为左边块SelectRAM 内容列,“1”为右边块SelectRAM 内容列。如表2 为XCV50 的帧位置分配,最下一行为主地址。

3 帧大小及结构

3. 1 帧大小

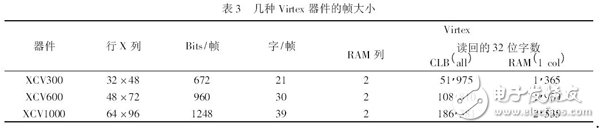

帧的大小取决于器件的行数。一帧的配置位的数目等于18X( # CLB_rows + 2) 加填充字。为流水作业,填充字被加在每一帧的未尾,以0 为填充位,使每一帧的配置位数目都是32 的整数倍。如表3显示了几种Virtex 器件的帧大小。同时这个表也显示了CLB 地址空间的位流大小以及每个RAM 块的字数。

3. 2 帧结构

3. 2. 1 CLB 帧结构

在器件中,每一帧坐落在竖直方向,表4 为CLB帧的结构,帧的前面为上端( 帧里面bit 的顺序为由上到下) 。对于CLB 列,第一个18 bit 控制上端的两个IOB,接下来的18bit 分配每一行的CLB; 最后的18bit 控制最下面的两个IOB,最后帧中加入了足够多的填充位“0”使之成为32 位的整数倍。

3. 2. 2 IOB 帧结构

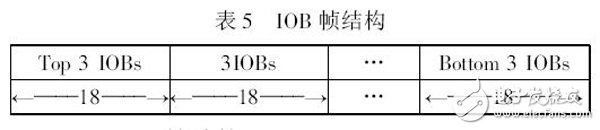

对于芯片两边的IOB 帧,每三个IOB 分配18bits,最后加入填充位“0”使之成为32 的整数倍。如表5 所示。

3. 2. 3 RAM 帧结构

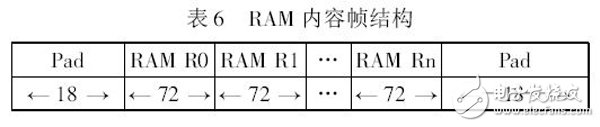

对于块SelectRAM 内容帧,如表6 所示,第一个18bits 是PAD 位,然后72bits 分配为每一RAM 行;最后的18bits 为PAD 位,帧中加入了足够多的填充位使之成为32 位的整数倍。

4 具体实例

例XCV300 芯片,阵列大小为32X48,在生成的. bin文件中,共有51, 975 个32 位字, 2475 个CLB 帧。

5 结束语

Virtex 芯片中,数据流是由帧构成的,数据流的大小取决于芯片的阵列大小,数据流中每一帧的最后用填充位“0”使之成为32 位字的整数倍,再把所有的帧按主地址顺序连接起来,这样就构成了完整的Virtex 数据流。了解帧结构及帧内的每个bit 位,对于回读芯片配置或重新配置数据流有重要意义。

-

本田数据流分析手册pdf2008-06-15 0

-

丰田数据流分析2008-06-15 0

-

奇瑞数据流分析手册2008-06-15 0

-

日产汽车数据流分析2008-06-15 0

-

大众数据流分析2008-06-15 0

-

国产汽车数据流分析2008-06-15 0

-

大众防盗数据流2013-08-31 0

-

研究labview的数据流2013-12-31 0

-

LabVIEW数据流控制方法研究2014-12-23 0

-

LabVIEW中的数据流编程基础2018-11-20 0

-

LabVIEW数据流语言的特点和有效控制方法2019-04-11 0

-

【工程源码】基于FPGA的OV5640数据流接收和应用基本逻辑设计2020-02-18 0

-

labview顺序结构中数据流问题2020-08-13 0

-

关于高速数据流盘处理技术看完你就懂了2021-04-29 0

-

ADC的数据流是怎样的?2022-02-28 0

全部0条评论

快来发表一下你的评论吧 !