光开关模块控制电路工作时序的FPGA实现方法

FPGA/ASIC技术

描述

摘要: 基于光开关在光传输交换中所起的重要作用,本文简要介绍光开关驱动电路的硬件连接,重点阐述光开关工作时序的FPGA 实现方法。

0 引言

光开关是按一定要求将光信号从一个光通道转换到另一个光通道的器件。随着通信网络的容量和速度的提高,组建全光网络( All Optical Network,AON) 成为通信技术的发展方向。全光网[1-2]的主要特征之一就是光分插复用( OADM) 和光交叉互联( OXC) 模块的广泛应用,光开关是OADM 和OXC 的核心器件,研制高性能、低成本的光开关和光开关模块对于光纤通信技术的发展具有重大意义。光开关是较为重要的无源光学器件,省去光/电、电/光转换过程,简化设备,提高网络可靠性,提供灵活的信号路由平台。光开关的作用包括信号在同一通道中的通断、光信号在同一通道中的波长转换和光信号在不同通道间的转换。

除了光开关模块本身的设计原理与结构外,其控制和驱动电路也是影响光开关模块[3-4]性能的重要因素。目前光开关控制系统[5-10]通常由单片机实现,由一台PC 机的相应程序模拟本地控制,发出相应的路由信息。PC 机的信息通过串口发送给单片机,单片机再进行进一步的控制动作。MEMS 光开关路由成功与否等信息由单片机读取其内部寄存器中控制数据,与原始的正确数据进行对比完成。操作完成后,又由单片机通过串口向PC 机产生相应的反馈信息。

本文提出一种光开关模块控制电路的FPGA 设计方法。通过硬件设置通道,由FPGA 读入通道信息后对其进行译码,并送到光开关的驱动电路。光开关通道切换成功标志信息由光开关反馈回的状态信号与FPGA 所读入的原始数据比较而得: 如果两者相同,则通道切换正确,若两者不同,则通道切换错误。

用FPGA 实现专用集成电路,不仅可以快速、灵活地修改和实现各种逻辑功能,还可以简化接口和控制,有利于提高系统的整体性能和工作可靠性,同时还能很好地满足各种高速设计的速度要求。另外在实际的使用过程中,如果产品在客户那里硬件逻辑上有问题或需要升级,不需要重新开发产品,只需让客户下载一个程序即可,节约了售后维护和升级成本。

1 、1 ×8 光开关模块的基本结构和工作原理

1. 1 MEMS 1 × 2 光开关的基本结构

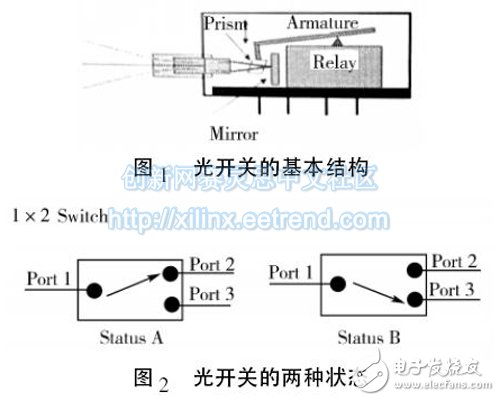

MEMS 光开关[11-12]是利用MEMS 技术在硅晶上刻出若干微小的镜片,通过静电力或电磁力的作用,使可以活动的微镜产生升降、旋转或移动,从而改变输入光的传播方向,以实现光路通断的功能。如图1、图2 所示: MEMS 1 × 2 光开关由一种受静电控制的微小镜面和继电器组成。光束在二维空间传输微镜的排列只有两个状态,即经过通道2 或通道3 两种状态。在控制电路中只要提供足够的驱动电压使继电器工作继而使微镜偏转即可改变光传输的通道[13]。

1. 2 MEMS 1 × 8 光开关模块的组成

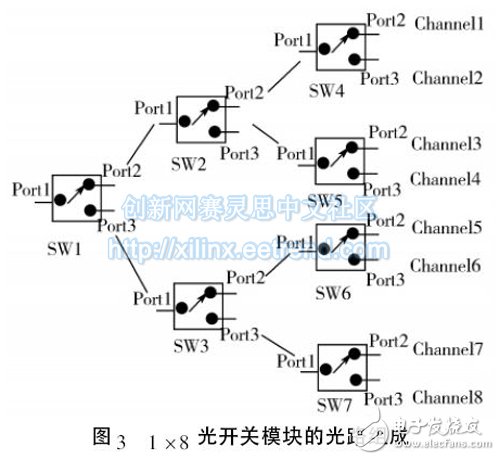

MEMS 1 × 8 光开关是由3 组1 × 2 光开关级联而成,如图3 所示,该模块的功能是光从SW1 的Port1进入,可从Channel1-Channel8 中的任一个通道输出。

2、 1 × 8 光开关模块控制电路

2. 1 总体结构

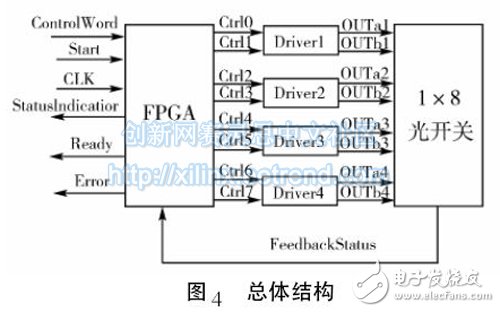

光开光模块电路的总体结构如图4 所示,整个电路主要分为3 个模块: FPGA 控制模块、光开关驱动电路、1 × 8 光开关模块。

( 1) FPGA 控制模块: 该模块主要实现光开关工作的时序、输入通道的译码、光开关通道选择正误的

提示等功能。

下面对该模块各信号进行说明:

ControlWord: 选择通道的控制字,可通过手动设置实现。

Start: 启动信号,低电平有效即此时光开关进行通道切换。

StatusIndication: 状态指示信号,指出经过驱动电路后反馈回FPGA 的状态信号是否与所要求的通道一致,如果不一致则报警处理。

CLK: FPGA 的时钟输入,在此CLK 为3. 17kHz。

Ready: 转换开始到结束的标志位。

Error: 通道转换正确与否的标志位。

Ctrl0-Ctrl7: FPGA 的译码信号。

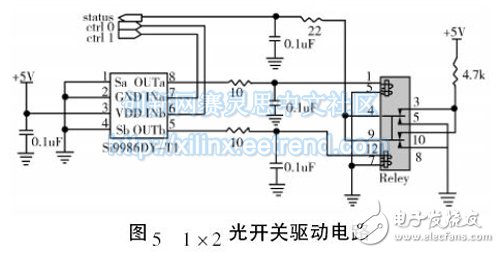

( 2) 光开关驱动电路: 该驱动电路主要是对通道的译码信号进行电流放大,使其转换成能够驱动光开关的信号,如图5 所示。

在图5 中,Ctrl0 和Ctrl1 为FPGA 输入的控制信号,控制信号加载到驱动电路,输出的脉冲电信号

OUTa 和OUTb 控制继电器开或者关,然后驱动微镜的转动,进而进行光输出通道的选择。Status 为反馈的状态信号。

在1 × 8 光开关模块中采用4 组驱动电路对通道的译码信号进行电流放大,OUTa1 和OUTb1 驱动SW1,OUTa2 和OUTb2 驱动SW2 和SW3,OUTa3 和OUTb3 驱动SW4 和SW5,OUTa4 和OUTb4 驱动SW6和SW7。

( 3) 1 × 8 光开关模块: 接收到驱动信号后进行通道选择,使输入的光从所设置通道输出。

整个控制电路的基本原理为: 由手动设置光通道的序号,按下Start( 启动信号) 光开关工作,进行通道切换,FPGA 模块将所设置的通道信号译号成驱动信号经过驱动电路对光开关进行控制。最后由光开关反馈给FPGA 其当前的状态信息,FPGA 将其与所设置通道信号比较是否相同,若相同,则通道切换成功,Error 为低电平; 若不相同,通道切换失败,则Error 为高电平。

2. 2 FPGA 的时钟选择

时钟电路如图6 所示。

时钟信号通过14 位计数器实现,此电路中晶振为13MHz,由Q12 作为FPGA 的时钟CLK 的输入信号,此时频率= 13MHz /2^12 = 3. 17kHz。通过FPGA形成开关动作约需10ms 的等待时间,只要在软件程序中设计一个计数程序,从0 计数到31,即等待时间= ( 1 /3. 17) * 32 = 10ms,此时10ms 的等待时间则形成。

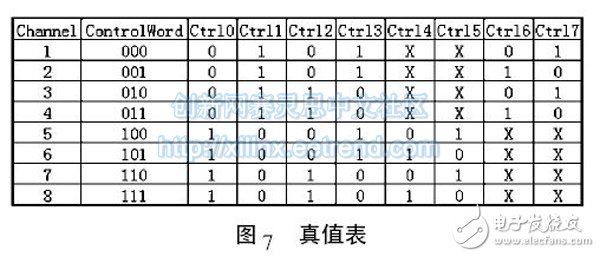

2. 3 光开关通道选择真值表

光开关通道选择各信号真值表如图7 所示。

ControlWord 为所设置的通道,Ctrl0-Ctrl7 为FPGA对通道的译码信号加在驱动电路上,以Status1-Status4 为反馈的状态信号。

2. 4 光开关控制时序的FPGA 实现

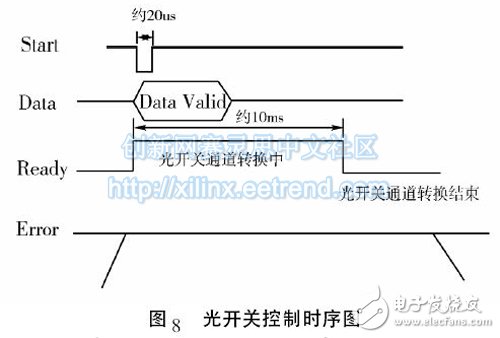

光开关工作的一项重要参数为开关响应速度( Switch Speed) ,它反应了开关切换通道过程的快慢。本设计中选择开关响应速度约为10ms 的光开关,要实现整个光开关的控制过程则设计了以下时序,如图8所示。

图8 中Start 为启动信号,低电平有效,Data 为光开关通道信号即ControlWord 的译码信号,Ready 作为光开关通道切换的开始及结束的提示,Error 用于指出通道切换是否正确,“0”表示错误,“1”表示正确。

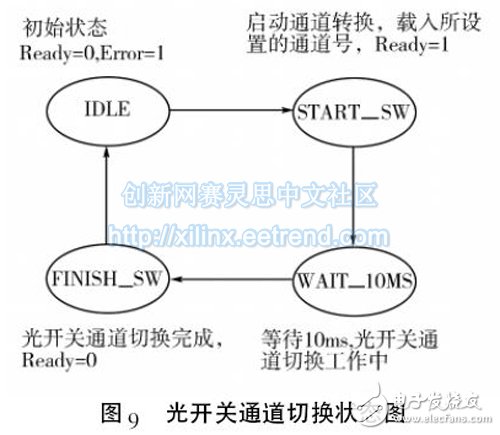

2. 5 光开关通道切换状态图

光开关通道切换状态图[14]如图9 所示。

状态图共分为4 个状态: IDLE、START _ SW、WAIT_10MS、FINISH_SW。在按下启动信号之前初始状态为IDLE,此时通道的译码信号位都为0,且Ready = 0,Convert_Falg = 0,Error = 1。当按下启动信号时状态转到START_SW,此时光开关开始切换通道,将设置的通道号( ControlWord) 经FPGA 译码成驱动信号进入驱动器再送到光开关模块,并且此时将光开关的4、9 引脚作为状态位反馈给FPGA。同时置Ready = 1,Convert_Falg = 1,然后进行等待约10ms,即进入状态WAIT_10MS,等待完成即进入FINISH_SW,此时通道切换完成,置Ready = 0,Convert_Flag = 0。

另外,当光开关通道切换完成后,FPGA 将反馈回的状态与之前所设置的通道信号相比较是否一致,若不一致,则置Error = 0,否则Error = 1。

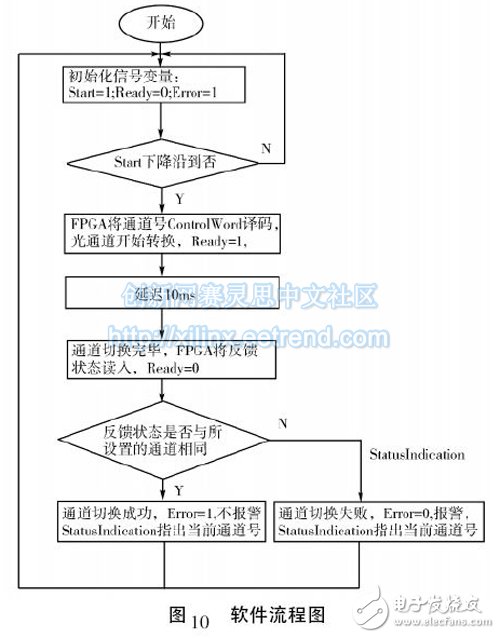

2. 6 FPGA 模块软件实现

程序采用Verilog HDL 语言,流程图如图10所示。

3 仿真结果

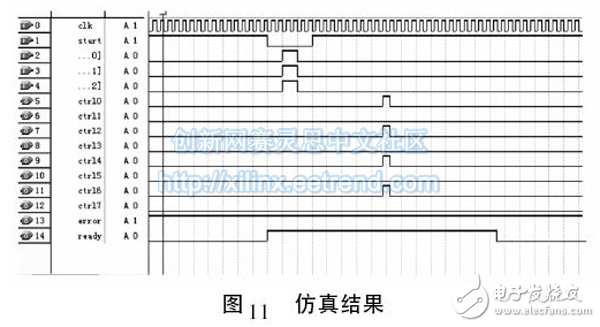

仿真结果如图11 所示。

从仿真结果可看出当设置通道为channel8 时,对应的驱动信号ctrl0 ~ ctrl7 为10101010,与真值表一致,且输出的Ready 与Error 信号也满足时序要求。

4 结束语

本文介绍了MEMS 1 × 8 光开关模块的整体结构,详细阐述了FPGA 在光开关模块控制电路的具体应用,分析了FPGA 如何配合光开关响应速度产生光开关的工作时序,并分析了如何将所需通道译码成光开关驱动信号的方法。此控制电路整体结构简单,有利于提高系统的整体性能和工作可靠性,同时还能很好地满足各种高速设计的速度要求。

-

基于FPGA的汽车尾灯控制电路设计与实现2011-11-10 0

-

时序控制电路2012-10-18 0

-

开关控制电路2018-08-20 0

-

轻松实现复杂电源时序控制2018-10-23 0

-

简单而有效的电源时序控制方法介绍2019-07-03 0

-

沙盘时序控制电路图2009-05-19 834

-

CMOS模拟开关控制电路的组成2010-04-14 2299

-

基于FPGA的OLED真彩色显示的实现2012-05-24 706

-

基于FPGA的OLED真彩色显示设计2012-06-27 1587

-

FPGA时序约束方法2015-12-14 759

-

FPGA如何实现对高速AD转换芯片的控制电路2018-09-21 1662

-

点动自锁混合控制电路工作原理2020-02-16 71388

-

使用通用电源IC实现电源时序控制的电路2022-01-18 4501

-

控制电路和工作电路的区别和联系2023-04-23 2135

-

如何使用继电器模块来控制电路?2023-11-17 1378

全部0条评论

快来发表一下你的评论吧 !