以MicroBlaze 处理器为内核的嵌入式系统开发过程详解

嵌入式技术

描述

当今时代,嵌入式系统已经无所不在,与人们的日常生活息息相关。嵌入式系统以微处理器为核心,以计算机技术为基础,其主要特征是实时性强。据统计,目前世界上微处理器每年生产总量的95 %以上都是面向嵌入式系统应用,围绕Xilinx 公司的MicroBlaze 微处理器,对其体系结构、设计流程和相关开发工具一一做出介绍,并且通过一个简单的实例来说明以MicroBlaze 处理器为内核的嵌入式系统的开发过程。

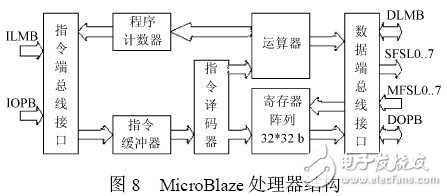

1 MicroBlaze 处理器结构

MicroBlaze 处理器是Xilinx 公司针对嵌入式处理器开发应用推出的一种32 位嵌入式处理器内核,他是一种软核结构,简单但灵活性强,在目标器件中可以进行任意配置。他采用RISC 指令集、Harvard 体系结构,该处理器有以下一些特征:

(1) 32 个32 位通用寄存器和2 个专用寄存器。

(2) 32 位指令系统, 支持3 个操作数和2 种寻址方式。

(3) 分离的32 位指令和数据总线,符合IBM 的OPB总线规范。

(4) 通过本地存储器总线(LMB) 直接访问片内块存储器(BRAM) 。

(5) 具有高速的指令和数据缓存(cache) ,三级流水线结构。

(6) 具有硬件调试模块(MDM) 。

(7) 带8 个输入/ 输出快速链路接口( FSL) 。

说明:

DOPB 器件内部的外围设备数据接口总线,用于处理器与片内的设备进行数据交换。

DLMB 实现数据交换的本地块存储器总线,该总线为处理器内核与块存储器(BRAM) 之间提供专用的高速数据交换通道。

IOPB 用于实现外部程序存储器的总线接口。当程序较大时,需要外接大容量的存储器,该总线提供读取指令的通道。

ILMB 用于取指令的本地存储器总线,该总线与器件内部的块存储器(BRAM) 相连,实现高速的指令读取。

MFSL0. 。 7 主设备数据接口, 提供点对点的通信通道。

SFSL0. 。 7 从设备数据接口, 提供点对点的通信通道。

2 EDK开发流程

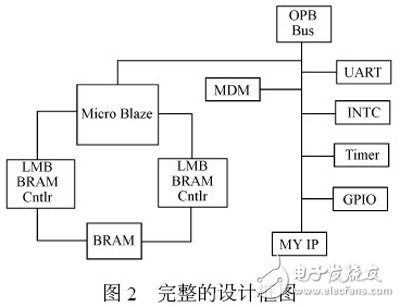

EDK( Embedded Development Kit) 是Xilinx 公司针对FPGA 内部32 位嵌入式处理器开发而推出的开发套件。EDK的工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试等工具,利用其集成开发环境XPS( Xilinx Platform Studio) 可以方便、快速地完成嵌入式系统开发的整个流程。EDK 以IP core的形式,提供诸如LMB ,OPB 总线接口、外部存储控制器、SDRAM 控制器、UART 中断控制器、定时器及其他一些外围设备接口等资源,利用这些资源,设计者能够轻松构建一个完善的嵌入式处理器系统,其完整的设计框图如图2所示。

一个完整的嵌入式处理器系统设计通常包括3 个部分: 硬件系统的构建;存储器映射及软件的开发;应用程序开发。

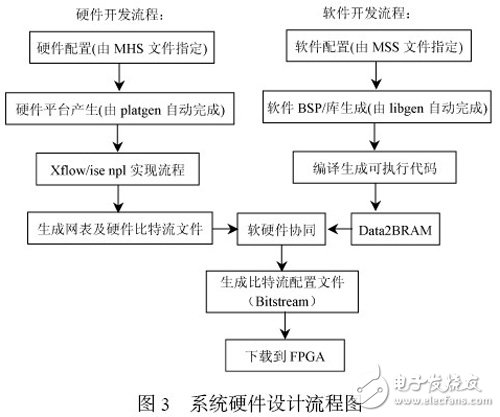

在XPS 集成开发环境下,嵌入式处理器硬件系统的构建由微处理器硬件规范(MHS) 文件和微处理器外围设备描述(MPD) 文件定义; 软件系统结构由微处理器软件规范(MSS) 文件定义,其开发流程如图3 所示。

MHS 文件用于描述硬件系统结构,定义处理器类型、总线接口、外设接口、中断处理和地址空间。该文件可用任意文本编辑器创建,是文本化的原理图输入。MPD 文件包含外围设备的所有有效输入/ 输出接口和硬件参数。MSS 文件主要用来定义软件库、驱动程序和文件系统。

说明:Data2BRAM 的作用是把软件代码文件( 3 .elf) 、FPGA 位流文件( 3 。 bit) 和块存储器(BRAM) 初始化数据文件( 3 。 bmm) 转换成新的FPGA 位流文件( 3 。 bit )和存储器数据文件( 3 。 mem) 。关于应用程序的编写将在下面的实例中详细介绍。

3 一个简单的实例

本实例基于e 元素科技的数字刀剑系列之火龙刀3评估板,简要叙述一个嵌入式处理器系统的开发流程,着重讲述应用程序的编写。对于其他评估板,只需对用户约束文件( 3 。 ucf) 稍做修改即可。为简单起见,与图2 所示一个完整的系统相比,本例所述系统只在OPB 总线上挂MDM(硬件调试模块) 和GPIO(通用输入/ 输出设备) 2 个外围设备,GPIO 对应评估板上8 个L ED 输出,当完成下载到FPGA 后,8 个L ED 将不停地闪烁。具体描述如下:

第一步,硬件系统构建,在XPS 集成开发环境下,利用BSP(Base System Builder ) 向导自动创建一个以Mi-croBlaze 处理器为核心的简单硬件系统,设置处理器时钟频率为50 MHz ,总线时钟频率为50 MHz ,设置片上读/写调试模块为调试接口,在处理器IP 中,只加入MDM 和GPIO。根据向导逐步操作,即可完成硬件系统的构建。

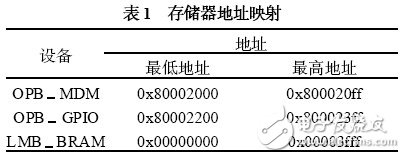

第二步,在硬件系统建立后,利用XPS 的集成工具,完成网表的生成和软件的配置,存储器地址映射(默认由系统自动生成,分配的地址随系统而异) 如表1 所示。驱动配置和存储器映射的标识符及地址分配包含在文件xparameter s. h 中, 以上两步具体操作实现细节可参考EDK相关文档。

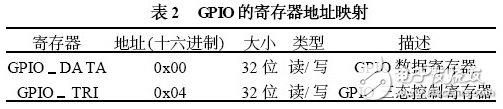

第三步,应用程序的开发。应用程序的编写使用C 语言,其方法有2 种,第一种是可以采用EDK 提供的应用程序接口函数(API) ,接口函数既多又复杂,不易搞懂;第二种方法是采用访问硬件的通用方式即简单的对地址赋值的方式。本例选用后者,要采用地址赋值方式,首先要了解GPIO 的寄存器地址映射,参见表2 。

相关代码及描述如下:

首先设定一个指针变量,将系统分配给GPIO 的地址赋给指针变量, 即让指针指向GPIO 的基地址, 也就是GPIO 的数据寄存器( GPIO DATA) ,接着向GPIO 三态控制寄存器写零(其地址为基地址加上偏移量4 ,即让指针变量加4) ,将GPIO 设置为输出,接下来就可以往GPIO数据寄存器送数,以控制8 个L ED 的状态。

# include “ xbasic_types. h”

# include “ xparameters. h”

# include “ xutil. h”

# include “ xgpio_l. h”

# define L ED DELA Y 2000000

void main ()

{

Xuint32 Data = 0xaa ;

int Delay ;

int count = 0 ;

Xuint32 3 ledpt r ;

ledpt r = (int 3 ) 0x80002200 ; / / 指针指向GPIO

*(ledpt r + 4) = 0x00000000 ;

/ / 向GPIO_TRI 寄存器写零,将GPIO 初始化为输出

while (1)

{ count + + ;

if (count %2 = = 0)

{

*ledpt r = 0x55 ;

/ / 向GPIO_DATA 寄存器送数,驱动L ED

}

else

{

* ledpt r = 0xaa ;

/ / 向GPIO_DATA 寄存器送数,驱动L ED

}

for (Delay = 0 ; Delay 《 L ED_DELA Y; Delay + + ) ;

/ / 延时以看清L ED 在闪烁

if (count %2 = = 0)

{

* ledpt r = 0x0f ;

/ / 向GPIO_DATA 寄存器送数,驱动L ED

}

else

{

* ledpt r = 0xf0 ;

/ / 向GPIO_DATA 寄存器送数,驱动L ED

}

for (Delay = 0 ; Delay 《 L ED_DELA Y; Delay + + ) ;

/ / 延时以看清L ED 在闪烁

}

}

-

[原创]★★最经典ARM嵌入式开发图书★★2008-11-07 0

-

嵌入式Linux系统开发技术详解--基于ARM(完整版)2017-02-25 0

-

嵌入式系统特点详解 嵌入式系统的六大特点2017-06-15 0

-

嵌入式系统开发过程中的常见问题和解决方法2017-09-12 0

-

ARM嵌入式Linux系统开发从入门到精通2017-10-31 0

-

《嵌入式Linux系统开发技术详解--基于ARM(完整版)》电子版2017-12-29 0

-

ARM嵌入式Linux系统开发详解2018-09-14 0

-

嵌入式视觉系统开发过程有什么技巧?2019-08-15 0

-

《嵌入式Linux系统开发技术详解--基于ARM(完整版)》 电子书免费资源分享2019-08-26 0

-

嵌入式系统开发过程简化2021-10-27 0

-

嵌入式系统的开发过程是怎样的2021-11-09 0

-

嵌入式系统的开发过程2021-12-22 0

-

一个嵌入式系统的开发过程2021-12-22 0

全部0条评论

快来发表一下你的评论吧 !