以FPGA和DSP为基础的光纤微振动传感器设计信号采集和算法处理实时系统

可编程逻辑

描述

随着光纤技术的不断发展,光纤微振动传感器越来越多地应用于周界安防、石油和天然气管道和通信线路监测等系统中。光纤微振动传感器是利用光纤是传感介质的一种分布式光纤传感系统,其中光纤既是传感介质,又是光传输介质。它可以在传感光纤布设长度内,对一定准确度范围内的突发事件进行远程和实时的监测。国内科研单位先后开展了对于光纤微振动传感器的相关研究工作,取得了一定的成果,实现对振动进行定位并报警,但模/数存在误报警的问题。对振动信号进行模式识别是一种降低误报警率的方法。国内各研究单位对光纤传感器的振动模式识别也开展了一些研究,但都是基于PC端的离线处理,满足不了系统实时性和小型化的要求。本文设计的基于FPGA和DSP的光纤微振动传感器数据采集和实时处理系统满足系统对实时性和小型化的要求,能够实现在线对光纤微振动传感器进行数据采集和实时模式识别算法处理。

1 系统设计

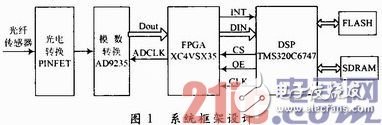

本文设计的系统对基于双M—Z型干涉仪的光纤微振动传感器的信号进行采集和处理,系统功能框架图如图1所示,由光电转换模块、模/数转换模块、FPGA模块和DSP模块组成。光纤微振动传感器的输出信号经光电模块从光信号转换为电信号;然后通过模/数转换模块,把模拟信号转化成数字信号;FPGA模块控制模/数转换模块的时钟,把数字信号采集入FPGA内的FIFO缓冲器,FIFO的半满信号线和DSP模块相连,会触发DSP的EDMA事务,把数据从FIFO转移到DSP的存储器SDRAM;并且存储器中的数据长度达到系统设定值时触发DSP的模式识别算法处理函数。

2 硬件设计

2.1 光电转换和模/数转换

光电转换模块采用SPF1200SF-D08型号的PINFET探测模块。该PINFET工作波长为1 000~1 650 nm,采用正负5 V供电。PIN管的反偏高、输出阻抗与FET的高输入阻抗得到很好地匹配,减少了外部干扰和杂散电容,大大降低了热噪声,而且配合采用AD8065的前置放大电路可以很好地匹配A/D转换电路输入电平范围。

模/数转换模块采用ADI公司的AD923512 bADC,其体积小,功耗低,耐高过载。AD9235有3种不同最大采样频率的型号,别是20 MS/s,40 MS/s,60 MS/s。该系统采用的是20 MS/s,其采样时钟由FPGA的DCM输出,由专用的差分ADC驱动芯片AD8138将单端信号转换为差分信号作为AD9235的输入。采样时钟和FIFO的写时钟配合,把模/数转换的数据写进FPGA内的FIFO。

2.2 DSP模块

DSP模块采用T1公司生产的TMS320C6747型号,时钟频率为300 MHz,是浮点、低功耗应用处理器。其中主要功能是完成数据的EDMA转移和算法处理,硬件设计主要包括EMIF接口和EDMA3控制器。

2.2.1 EMIF接口

C6747通过它的2个EMIF接口:EMIFA和EMIFB,可连接外部存储器,或其他外设。C6747的EMIFA接口时钟频率可达100 MHz,既可接SDRAM也可接FLASH。本系统通过EMIFA接口外接1片16 MB的NOR FLASH S29GL128M,在CE2地址空间内实现代码的存储,配置寄存器CE2CFG=0x04842 32D;EMIFA接口同时还和FPGA内的FIFO相连,使FPGA内的FIFO空间映射到DSP的CE3地址空间,CS3控制FPGA端的FIFO,CE3CFG=0x0484 222D。

C6747的EMIFB接口的时钟频率可达133 MHz,只可接SDRAM。本系统通过EMIFB接口外接2片SDRAM芯片IS42S16160B组成64 MB的存储器,用于存放实时采集的数据和算法运算过程中的临时数据;配置寄存器之前需先置SDCFG.TIMUNLOCK为1,然后才可更改其他寄存器:SDREF=0x00 000410,SDTIM1=0x10912A10;SDTIM2=0x70090005,SDCFG=0x00010421。

2.2.2 EDMA3控制器

TMS320C6747内的EDMA3控制器是一个高效的数据传输引擎,可在没有CPU参与的前提下,完成DSP存储空间内的数据转移,保证CPU核心专注于信号处理算法的运算。

EDMA3传输有3种触发方式:事件触发、连锁触发和CPU触发。本系统设计选择事件触发,FPGA内FIFO的half_full输出信号和DSP的GP4[2]相连,满足条件会自动触发一个EDMA请求,执行对应于参数RAM的数据传输。

EDMA3数据传输的控制通过设置参数RAM来实现。本系统设计设置OPT=0x0010000C。其中TCINTEN位置1,当最后传输事务完成之后会触发DSP系统的EDMA中断;STATIC位置1,在EDMA事务传输请求完成之后参数RAM不会被更新或者链接到别的参数RAM;SYNCDIM位置1,EDMA传输类型是二维,每一个传输请求传输BCNT x ACNT字节。

为使EDMA事件传输及中断能够被触发并顺利执行,本系统设计进行下列配置:

(1)GPIO4[2]配置为边沿触发,且打开中断使能;

(2)对EDMA寄存器EESR相应位写1,使EER相应位置1,使EDMA3CC监测外部触发事件;

(3)配置EDMA的参数RAM并写进配置寄存器,定义EDMA数据传输的参数;

(4)配置EDMA寄存器DMAQNUM,映射GP4[2]中断对应的28号事件到队列0;

(5)配置EDMA寄存器DRAE[1],使能EDMA传输完成产生的中断;

(6)置EDMA寄存器IER相应位为1,使对应通道的传输完成能触发EDMA中断;

(7)DSP控制寄存器IER.NMIE置1,使能DSP所有非重启的中断;

(8)DSP控制寄存器CSR.GIE置1,打开DSP中断的总开关。

2.3 FPGA和DSP接口

系统设计采用FPGA和DSP双核心,FPGA在并行运算方面有很高的效率,可负责控制信号的采集和预处理,而DSP擅长信号处理,负责信号的算法,保证系统的高效运行。FPGA和DSP的接口设计是保证两者进行有效通信的关键。

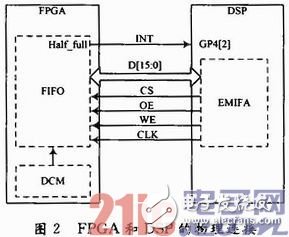

本系统设计中DSP通过EMIFA和FPGA相连的物理接口如图2所示。接口的信号线可分3部分:DSP对FPGA的控制线,FPGA通知DSP的中断信号线和数据线。

(1)控制线:在FPGA内部和DSP相连的是一个输出FIFO,它的片选信号、时钟信号和写使能信号对应于TMS320C6747的信号EMA_CS3,EMA_ CLK,EMA_WE信号;而读使能信号由EMA_OE,EMA_CS3和EMA_CLK共同产生,因为EMIFA的每一个读时序包含多个EMA_CLK时钟周期,在EMA_OE有效电平期间,FIFO的读使能信号只能持续一个时钟周期,否则多个数据将被读出。

(2)中断信号线:FIFO的信号线half_full和C6747的其中一个通用管脚GP4[2]相连,通过配置GPIO的配置寄存器SET_RIS_TRIG45,CLR_ FAL_TRIG45和BINTEN,GPIO4[2]电平由低到高的变化将会产生中断。

(3)数据线:EMIFA的数据线是16位,12位的FIFO的输出数据线直接和EMIFA的EMA_D低12位相连,在FPGA中配置与EMA_D高4位相连的管脚一直为0。

3 软件设计

系统软件设计包括FPGA模块和DSP模块的软件流程控制,FPGA模块内部主要是FIFO设计,控制数据的采集以及配合DSP进行通信,而在DSP模块中主要包含EDMA数据传输控制和算法处理。

3.1 FPGA的FIFO

FPGA模块采用Xilinx公司的XC4VSX35型号,其内部设计有DCM模块和FIFO模块。DCM模块和外部的晶振相连,引入时钟信号,通过DCM输出时钟信号给AD9235作时钟信号以及FPGA内部FIFO的写时钟信号。FIFO模块设有相互独立的读写时钟,是异步读写方式,能够协调模/数转换模块和DSP模块之间的工作,把数据从模/数转换模块的输出转移到DSP模块。

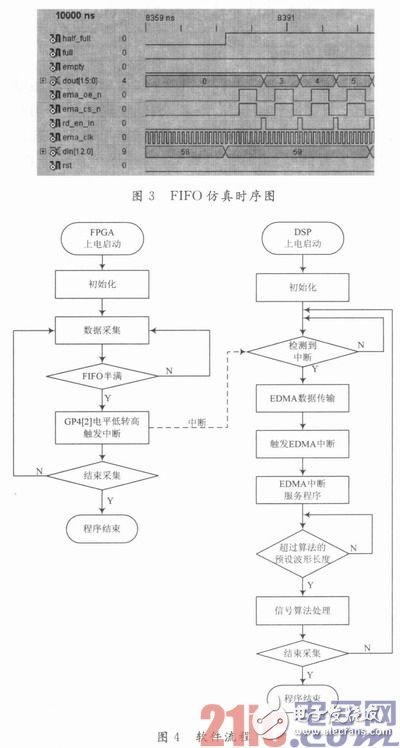

FIFO模块采用XC4VSX35内部的Block RAM,通过IP核配置的方式,生成所需的FIFO缓冲存储器,FIFO的写入时钟由FPGA内部的DCM提供。在写入时钟的控制下AD9235的输出数据写入FIFO缓冲器,当FIFO内数据数量达到设定值时,FIFO的half_full信号线电平由低转高,以GPIO中断的方式触发DSP的EDMA事务进行数据转移。图3是ISE7.1中FIFO的仿真时序图。

为了避免系统重置之前half_full信号上升沿导致错误的触发DSP的EDMA事件,在rst置位之前half_full置1。模/数转换模块的AD9235输出位数是12位,FIFO的输入和输出均设为12位。

3.2 DSP的软件流程

DSP模块的软件流程设计采用TI的DSP集成开发环境CCS3.3。DSP中的软件配合FPGA上的FIFO一起控制信号的采集和数据的实时处理。软件实现的功能分3个部分:系统初始化,EDMA传输控制和中断服务程序,算法处理。软件流程图如图4所示。

C6747上电后,首先进行系统初始化,设置各配置寄存器使DSP各功能模块按设计要求运行,主要配置管脚复用、PLL、PSC和EMIF。FPGA同时启动并开始控制AD9235开始采集数据,传感器的信号经过模/数转换进入FPGA的FIFO缓冲器,当FIFO内的数据量达到设定长度时,half_ full信号线电平由低转高,输出中断信号。然后,因为此信号线和DSP的通用管脚GP4[2]相连,DSP内部的EDMA3控制器会检测到此GPIO中断事务,并产生一个传输请求,按照设定的参数把数据从FPGA内的输出FIFO转移到DSP模块的SDRAM存储器。在完成此EDMA传输请求之后触发一个EDMA中断,在中断服务程序中检测SDRAM内数据长度。最后,当SDRAM内存储的数据长度达到设定的长度时,触发信号处理函数进行信号处理,譬如对信号进行滤波、小波变换、功率谱分析等。

4 结语

本文基于FPGA和DSP,针对M—Z型光纤微振动传感器设计了一种结构简单、低功耗、实时性能好的信号采集和算法处理的实时系统。测试结果表明系统能采集传感器信号,准确传输到DSP。并进行算法处理;为光纤微振动传感器的数据采集和处理提供了一个良好的解决方案。该系统基于FPGA和DSP,能适应不同的算法,有利于系统的扩展和改进。

-

差动式光纤微弯传感器2018-10-25 0

-

基于FPGA与DSP的视频处理系统设计2019-06-19 0

-

基于FPGA+DSP架构的视频处理系统设计2019-06-28 0

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 0

-

一种基于FPGA的振动信号采集处理系统设计介绍2019-07-01 0

-

浅析差动式光纤微弯传感器的原理2019-07-18 0

-

基于压电薄膜(PVDF)传感器以及无线传输的振动信号测量系统2020-08-26 0

-

VHDL 基于FPGA的高速数据处理系统设计思路2020-08-31 0

-

FPGA的高速数据处理系统结构和硬件设计2020-09-04 0

-

基于FPGA和DSP芯片的光纤传感信号实时采集系统设计2021-07-05 0

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 622

-

基于DSP和DSP/BIOS的实时雷达信号采集与处理系统2010-01-16 497

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 994

-

基于FPGA的振动信号采集系统设计及实现2017-11-17 6136

-

基于FPGA的振动信号采集处理系统设计并实际验证2017-11-18 3303

全部0条评论

快来发表一下你的评论吧 !