利用FPGA实现千兆以太网业务在SDH上的封装和映射设计

可编程逻辑

描述

随着人们对数据业务需求的不断增长,以太网作为全世界应用最为广泛的网络通信技术之一,在全世界得到了大规模的普及。SDH是电信部门常用的通信传输设备,具有高可靠性和高安全性的特点。EOS(Ethernet over SDH)技术即借现有的SDH传输设备实现以太网业务的传输,具有非常重要的现实意义。

基于以太网的七层架构,在第二层数据链路层传输的是以太网的MAC帧。由于以太网和SDH系统的传输速率不匹配,需要通过封装进行速率调整后才能映射到SDH的虚容器中。目前来讲,常用的是GFP(Generic Framing Procedure)封装。GE(千兆以太网)信号在SDH系统中的映射可以分为相邻级联和虚级联两种模式。相邻级联是在整个传输过程中保持连续带宽,各个级联的VC是相邻的,在SDH网络系统中需要有能够进行相邻级联处理的中间设备,而虚级联的应用方式比较灵活,将连续带宽分解到多个VCs上传输,不一定相邻,在传输的终端再将多个VCs重新组合成连续带宽。因此,虚级联方式有效地节省了带宽,在系统中只需能够进行处理的终端设备即可。在实际使用中,这种方式的应用比较广泛。

1 FPGA收发模块设计

本文实现的传输方式是在STM-16中传输1路GE信号,需要对以太网MAC帧进行GFP封装。GFP帧分为GFP-F和GFP-T两种模式,本设计采用的是GFP-F封装模式。STM-16的传输速率是2.488 32 Gb/s。STM-16一共包括16路STM-1信号,STM-1的传输速率是155.52 Mb/s。STM-1信号采用虚级联方式,利用VC-4-XV(X=1~7)最多采用7路STM-1信号即可传输1路GE信号。剩余STM-1通道的信号用来传输其他数据业务。

以太网数据在SDH设备中传输过程如下:在SDH发送部分中,以太网通过接口处理芯片产生MAC数据帧,通过GMII接口传送给FPGA。FPGA将MAC帧进行GFP协议的封装,然后映射到SDH的虚容器VC当中,再通过添加复用段和再生段开销,生成STM-16数据帧,发送给光模块再上到光网络;在SDH接收部分中,光接收模块从光网络将STM-16数据帧接收F来发送给FPGA,FPGA在内部处理相关的开销,再将GFP数据帧从VC虚容器中提取出来,通过解帧处理,将以太网的MAC帧还原出来,经过处理后发送给以太网。

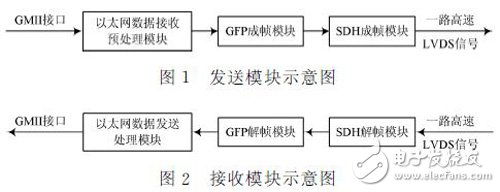

FPGA的内部设计可以分成发送模块和接收模块两部分。其中,发送模块可以分为以太网数据接收预处理模块、GFP成帧模块、SDH成帧模块;接收模块可以分为SDH解帧模块、GFP解帧模块、以太网数据发送处理模块。发送和接收模块示意图分别如图1和图2所示。

发送部分的三个模块的功能分别如下:以太网数据接收处理模块利用FIFO缓存模块存储每一个有效MAC数据帧的数据和长度。同时实现数据从以太网时钟域到SDH时钟域的转换;GFP成帧模块对以太网MAC帧进行GFP封装,通过调整GFP数据帧和GFP空闲帧的插入,将以太网MAC帧映射到SDH的高阶VC-4虚容器中;SDH成帧模块对虚容器进一步处理,添加开销字段,生成STM-16数据帧,再利用FPGA内部的GTP接口将16位155. 52MHz的并行数据转化为一路2 488.32 MHz高速LVDS差分信号发送出去。

接收部分实现的过程是发送部分的逆过程。

GFP成帧模块分为GFP数据帧产生模块、空闲帧产生模块、插入帧选择模块、GFP扰码模块;GFP解帧模块分为GFP帧同步模块、GFP解扰模块、GFP接收帧处理模块。

GFP数据帧产生模块在去掉MAC帧8 B前导码后,将剩余部分的数据封装为GFP数据帧。按照GFP协议添加4 B的核心头部和4 B的净负荷域头部,将非定长的以太网MAC帧添加到净负荷信息字段,在帧尾添加4 B的净负荷帧校验序列(FCS)。

空闲帧实际上属于GFP用户管理帧的一种,没有净负荷域,只包含一个GFP核心帧头,是4 B的全0比特与序列“B6AB31E0”异或所得。

插入帧选择模块根据流量情况调整数据帧和空闲帧的插入,在没有数据帧要发送时,插入空闲帧,以保证GFP数据流的连续性。

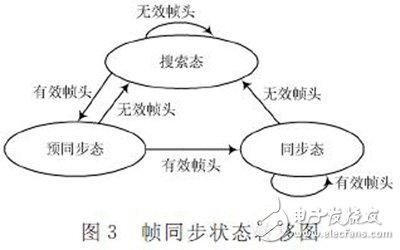

在整个FPGA设计中,接收端的帧同步模块是比较重要的,它主要进行GFP帧的帧头搜索和同步保持处理。同步状态转移图如图3所示。

用一个状态机表示三种状态,即搜索态、预同步态和同步态。在预同步状态和同步状态时都只取1帧进行状态跳转判断。状态机在FPGA初始化时默认处于搜索状态,然后在连续的GFP数据流中进行帧头的搜索判断,将连续的数据流在每个时钟周期按字节存入缓存器中,在每个时钟周期进行4 B的扰码判断,即连续的4个字节与扰码序列“B6AB31E0”进行异或,得到的4 B数据中前2个字节根据扰码多项式G(x)=X16+X12 +X5+1生成2个字节的校验值,然后与后2个字节进行比较,如果一致则表示找到了帧头,进入到预同步态。在预同步态继续在一帧帧头的相应时刻进行帧头的判断,如果正确则跳转到同步态,否则重新跳转到搜索态,继续寻找帧头。如果进入到同步态,和预同步态一样,也在一帧帧头的相应时刻进行判断,如果正确则继续保持在同步态,否则跳转到搜索态,重新在数据流中进行帧头的搜索。只有在处于同步状态时才能继续对数据进行后续处理。

在SDH和GFP协议的成帧解帧里都要进行扰码和解扰处理。SDH的扰码多项式为G(x)=X7+X6+1,GFP对核心头部PLI的扰码多项式为G(x)=X16 +X12+X5+1,GFP净负荷域的扰码多项式为G(x)=x43+1。这些扰码器都为串行扰码器,对于GE这种速率的数据如果也采用串行处理方式的话,FPGA内部是无法实现的。经过转换处理,可以将串行扰码器变为并行扰码器再进行扰码,即可降低处理速度,满足时序要求。

2 仿真综合及实现

本设计采用VHDL硬件描述语言,使用的是XILINX公司带有高速SERDES接口的SPARTAN-6芯片,利用ISE 12.1和仿真软件进行了综合和仿真。由于FPGA的内部资源较为丰富,本身自带的IP核具有可靠性、方便性和灵活性的特点。时钟部分使用了XIUNX芯片内部的DCM时钟管理模块,双端口RAM以及FIFO缓存器都使用了FPGA的内部IP核资源。高速数据接口部分使用的是芯片内部的GTP模块,去掉了外部高速接口转换芯片,简化了电路板的设计,不但提高了设计效率,也提高了系统设计的稳定性。

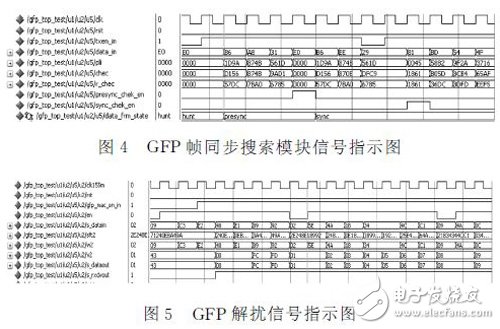

图4和图5表示的是对EOS数据进行VC-4-7V虚级联后的部分时序仿真图。

图4中,data_frm_state信号表示的是帧同步状态机。在数据流中,状态机一开始处于hunt状态,一旦找到帧头,则进入到presync状态;如果帧头检测没有错误,则继续跳转到sync状态;如果帧头判断正确,那么状态机就一直保持在sync状态。

图5中,s_datain信号表示的是解码前的数据,s_dataout信号表示的是根据扰码多项式G(x)=X43+1解扰后的数据。

3 结语

综上所述,利用FPGA可以实现千兆以太网MAC帧在SDH数据帧中的封装和映射,配合外围接口电路的使用,可以实现GE在STM-16中的传输。EOS技术既增强了以太网传输的覆盖范围,也丰富了SDH设备的传输接口,极大地方便了用户的使用。同时,利用FPGA进行设计,大大缩短了开发的周期,也便于以后的升级和维护。

-

ATM上的以太网服务介绍2009-05-25 0

-

采用StratixIV FPGA实现100G光传送网2011-07-13 0

-

基于AlteraFPGA的千兆以太网实现方案2013-06-10 0

-

百兆以太网改千兆,要怎么修改程序?2013-10-03 0

-

【FPGA开源教程连载】DDR2+千兆以太网2016-12-30 0

-

简谈基于FPGA的千兆以太网2018-02-03 0

-

如何使用斯巴达FPGA实现千兆以太网接口?2019-08-07 0

-

如何实现kc705以太网10千兆位设计?2019-09-27 0

-

什么是基于Xilinx FPGA的千兆以太网及E1信号?2019-10-15 0

-

如何在stm32 f407上实现千兆以太网?2019-11-01 0

-

分享一款不错的基于Altera FPGA的千兆以太网实现方案2021-05-08 0

-

简谈基于FPGA的千兆以太网设计2023-06-01 0

-

基于FPGA的十端口千兆以太网接口的设计与实现2009-08-29 535

-

基于Altera FPGA的千兆以太网实现方案2010-12-23 699

-

FPGA如何为以太网和千兆以太网解决低功耗问题2022-05-07 3377

全部0条评论

快来发表一下你的评论吧 !