基于Xilinx MicroBlaze 软核处理器的嵌入式GPS 接收机系统设计研究

可编程逻辑

描述

随着超大规模集成电路(VLSI)和现场可编程门阵列(FPGA)技术的发展,GPS接收机也正朝着小型化、高度集成化的方向发展。应用FPGA进行数字系统设计,不但能减小系统的体积,而且还能提高系统运行的可靠性。FPGA可使数字系统在线重新配置,设计更加灵活,且易于更改和升级[1-3]。更为重要的是,目前,Spartan3E系列现场可编程阵列中可以嵌入32位MicroBlaze软核处理器。因此,利用FPGA完成GPS接收机中对实时性要求比较高的处理,由MicroBlaze完成GPS接收机中相应的控制以及运算工作,使得整个GPS接收机的功能实现在一个FPGA芯片内完成,这不仅提高了系统的抗干扰性能,而且为系统将来进行ASIC设计提供基础。

现针对Xilinx MicroBlaze 软核处理器的GPS 接收机系统的设计进行了深入的研究,给出了软硬件的设计、存储器空间的详细设置方法。

1 嵌入式GPS 接收机系统的总体设计

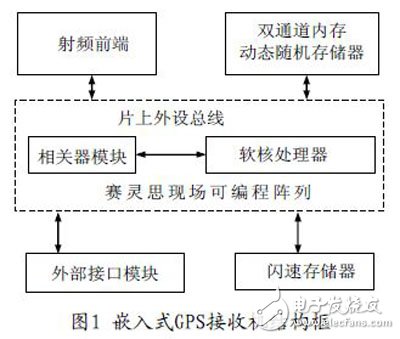

嵌入式GPS接收机系统是基于Xilinx公司的Spartan™-3E Starter进行开发的。在嵌入式GPS接收机设计中,采用NJ1006A作为射频前端;利用FPGA的逻辑单元执行相关处理;利用FPGA中的软核处理器MicroBlaze执行基带信号处理、位同步、帧同步以及导航解算功能;FPGA的逻辑部分和嵌入式软核处理器之间通过处理器内部的片上外设总线(OPB)进行通信;从而,使得整个GPS接收机的中频信号处理可以在一个FPGA芯片内完成。系统设计的总体框图如图1所示。

2 基于MicroBlaze的嵌入式GPS接收机设计

利用MicroBlaze 嵌入式处理器进行GPS 接收机系统设计主要包括两大部分:系统硬件的构建和系统软件的开发。

2.1 系统硬件框架的建立

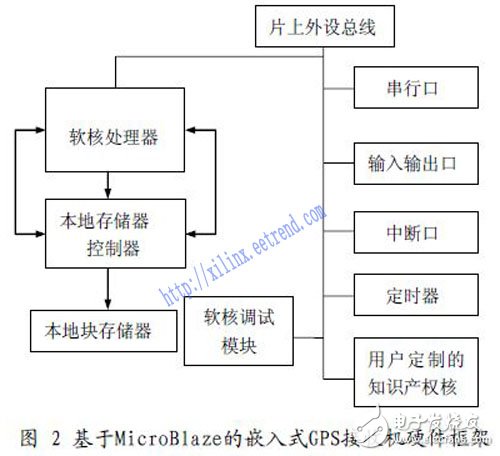

在用Xilinx公司的FPGA进行嵌入式设计时,Xilinx公司提供嵌入式开发工具EDK。EDK提供了本地存储器总线(LMB)、OPB总线接口,外部存储器接口,同步动态随机存储器(SDRAM)控制器,闪速存储器(Flash)控制器,串口中断控制器,定时器以及其他一些外围设备接口资源。这些接口都是以IP core的形式进行应用。用户可以根据自己的实际需求通过IP core来建立一个完善的嵌入式处理器系统[4],GPS接收机系统完整的硬件框架[5]如图2所示。

2.2 系统软件的开发

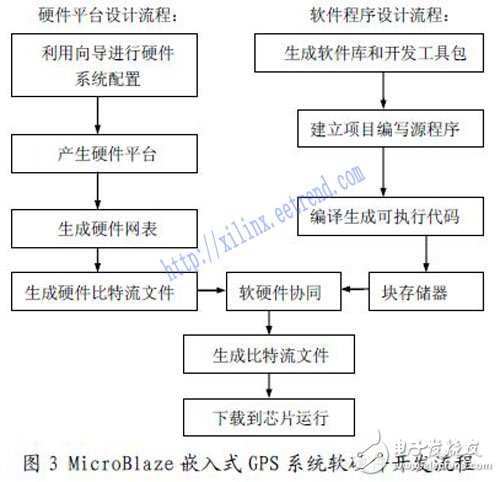

在嵌入式工具套件(XPS)中,嵌入式处理器硬件系统的构建由微处理器硬件规范(MHS)文件和微处理器外围设备描述(MPD)文件定义;软件系统结构由微处理器软件规范(MSS)文件定义,其中,MHS 文件用于描述嵌入式处理器平台FPGA 的硬件系统结构,主要定义当前平台FPGA 设计的处理器类型、总线结构、外设接口、中断处理和地址空间。MSS 文件用于完整描述嵌入式处理器平台的FPGA 的软件系统结构,主要定义当前平台FPGA 设计的软件库、驱动程序和文件系统。其开发流程如图3 所示。

3 嵌入式GPS接收机GPIO外设的程序设计

为了方便说明,下面以GPS 接收机中对外的用户输入/输出(I/O)接口为例说明嵌入式开发的具体方法。在进行Microblaze 开发时可以把Microblaze 作为Top Module,那么在开发过程中,不需要使用ISE,只用嵌入式开发套件(EDK)。另外,也可以把Microblaze 作为Sub Module,这时,在ISE 工程中可以像调用诸如时钟管理模块(DCM)的IP Core一样,调用Microblaze 软核处理器。在本程序设计中利用XMD 调试时将Microblaze 作为Top Module 来设计,利用ISE和modelsim 进行仿真时Microblaze 作为Sub Module 来处理。本程序是在Xilinx 公司Spartan-3E STARTER KIT 开发板上进行设计和实现的。在进行本系统设计时,需要在MicroBlaze的OPB 总线上添加MDM(硬件调试模块)和通用输入/输出驱动(General Purpose IO)。

在建立好硬件系统之后,对system.ucf文件进行引脚约束。在系统硬件建立完成后,MicroBlze产生的库文件和头文件,用户可以直接进行调用,这些应用程序接口(API)函数都提供了调用接口,用户只需给函数传递相应的实参即可对挂在总线上的设备进行操作。

为了验证上面设计的程序正确与否,可以利用ISE 调用Modelsim 对其进行仿真。正如上面所述,此时需要将MicroBlaze 处理器当作一个IP core 添加到ISE 工程中,并在ISE 的顶层文件中编写测试文件,为处理器的输入信号提供激励,输出信号提供端口。测试文件编写完成后,直接可以点击ISE 中的Update Bitstream with Processor Data,随后可以进行Modelsim 仿真。仿真中用到系统复位信号,时钟信号sys_clk_pin 和fpga_0_LEDs_8Bit_GPIO_d_out_pin控制信号。时钟周期与系统的主时钟50 MHz是同步的,系统的复位电平为高电平复位。所以,在系统复位后,复位引脚保持低电平状态。

4 软件程序中各段空间配置的设计

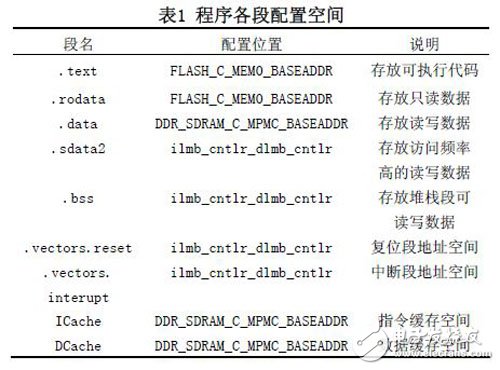

在应用程序中良好正确的链接脚本文件是保证代码高效执行的重要环节。为了满足GPS接收机对实时性的要求,在设计中充分考虑各种存储器自身的优势,通过合理地设置链接脚本文件等措施来提高关键应用程序的执行效率。本系统链接文件各个段配置如表1表述,实验表明,该配置可以较好地满足系统实际运行要求。

5 程序设计和调试时注意的问题

在ISE 下,调用modelsim 进行仿真之前需要对ISE 库进行编译。

在ISE 下,把MicroBlaze 作为子模块来调用进行仿真时,需要对EDK 库进行编译。

在ISE 下使用modelsim 进行仿真microblaze 软核程序时,需要编写测试文件。调试时,可以利用系统外挂的串口设备进行串口打印输出,方便用户对程序的调试和运行中间结果的观察。

6 结语

研究了嵌入式GPS接收机的整体设计。给出了基于软核处理器MicroBlaze的嵌入式开发过程,利用ISE和Modelsim对挂

在MicroBlaze处理器上的GPS接收机的GPIO接口进行仿真。将Xilinx 公司提供的IP core 和用户定制的IP core 挂到

MicroBlze软核上构建嵌入式GPS接收机系统,提高了系统的集成度,改善了系统的电磁兼容(EMC)性能,满足了嵌入式GPS接收机系统的开发。

-

简谈Xilinx Zynq-7000嵌入式系统设计与实现2024-04-10 0

-

嵌入式云计算与视频大数据——基于TI嵌入式处理器2014-07-19 0

-

嵌入式处理器硬件设计2017-11-15 0

-

【下载】《FPGA上的嵌入式系统设计实例(附光盘XILINX大学合作计划指定教材)》2017-12-08 0

-

嵌入式软核Nios Ⅱ串口直接读写寄存器有哪些编程方法?2019-08-06 0

-

嵌入式语音信号录取系统工作原理是什么?2019-08-27 0

-

如何提高FPGA嵌入式处理器的系统除错率?2019-09-17 0

-

怎么设计集软核处理器的嵌入式设计平台?2020-03-13 0

-

MicroBlaze处理器的PetaLinux操作系统怎么移植?2020-03-16 0

-

【正点原子FPGA连载】第一章MicroBlaze简介--摘自【正点原子】达芬奇之Microblaze 开发指南2020-10-16 0

-

求一款双MicroBlaze软核处理器的SOPC系统设计2021-03-16 0

-

请问如何实现片上嵌入式Nios Ⅱ软核六处理器系统的设计?2021-04-19 0

-

嵌入式处理器是什么2021-10-27 0

-

基于Xilinx MicroBlaze的嵌入式I/O系统设计2011-05-14 685

-

基于Xilinx MicroBlaze多核嵌入式系统的设计2011-07-20 877

全部0条评论

快来发表一下你的评论吧 !