什么是并行比较型ADC

电子常识

描述

ADC,Analog-to-Digital Converter的缩写,指模/数转换器或者模数转换器。是指将连续变化的模拟信号转换为离散的数字信号的器件。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。

与之相对应的DAC,Digital-to-Analog Converter,它是ADC模数转换的逆向过程。

ADC最早用于对无线信号向数字信号转换。如电视信号,长短播电台发接收等。

ADC简介

典型的模拟数字转换器将模拟信号转换为表示一定比例电压值的数字信号。然而,有一些模拟数字转换器并非纯的电子设备,例如旋转编码器,也可以被视为模拟数字转换器。

数字信号输出可能会使用不同的编码结构。通常会使用二进制二补数(也称作“补码”)进行表示,但也有其他情况,例如有的设备使用格雷码(一种循环码)。

ADC 并行比较型

1.转换方式

直接转换ADC。

2.电路结构

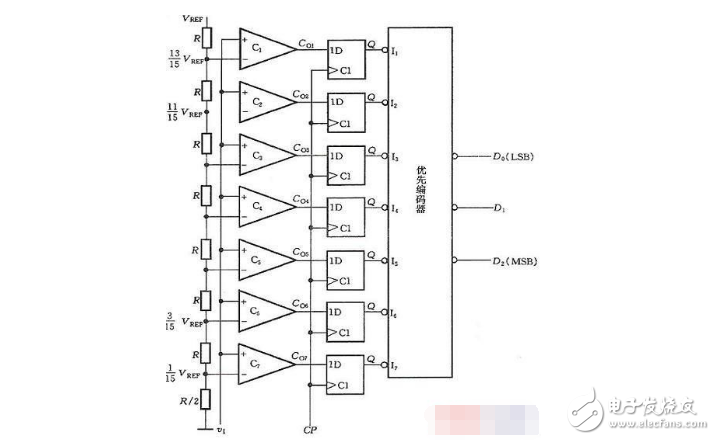

3位并行比较型A/D转换器原理电路如图11.9.1所示。它由电阻分压器、电压比较器、寄存器及编码器组成。

图11.9.1 3位并行A/D转换器

3.工作原理

图中的8个电阻将参考电压VREF分成8个等级,其中7个等级的电压分别作为7个比较器 C1~C7 的参考电压,其数值分别为VREF/15、3VREF/15…、13VREF/15。输入电压为v1,它的大小决定各比较器的输出状态,如当0≤v1《 VREF/15时,C7~C1的输出状态都为0;当3VREF/15≤v1《5VREF/15时,比较器C6和C7的输出CO6=CO7=1,余各比较器的状态均为0。根据各比较器的参考电压值, 可以确定输入模拟电压值与各比较器输出状态的关系。比较器的输出状态由D触发器存储,经优先编码器编码,得到数字量输出。 优先编码器优先级别最高是I7 ,最低的是I1。

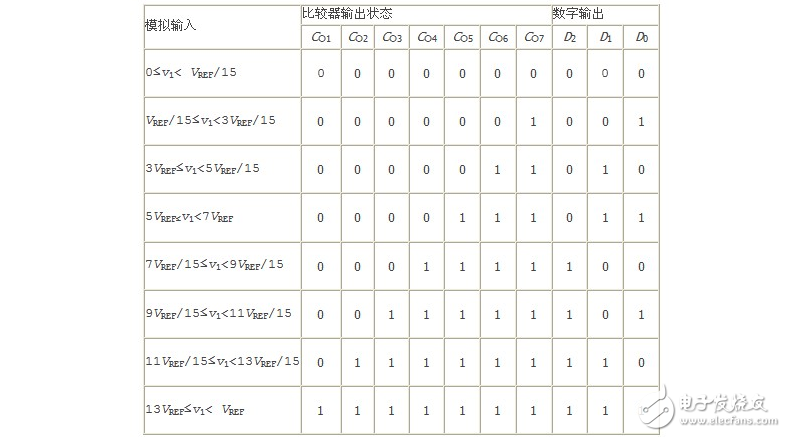

设v1变化范围是 0~VREF,输出3位数字量为D2D1D0,3位并行比较型A/D转换器的输入、输出关系如表10.2.1所示。

表11.9.1 3位并行A/D转换器输入与输出关系对照表

4.特点

(1)由于转换是并行的,其转换时间只受比较器、触发器和编码电路延迟时间的限制,因此转换速度最快。

(2)随着分辨率的提高,元件数目要按几何级数增加。一个n位转换器,所用比较器的个数为2n-1,如8位的并行A/D转换器就需要28-1=255个比较器。由于位数愈多,电路愈复杂,因此制成分辨率较高的集成并行A/D转换器是比较困难的。

(3)精度取决于分压网络和比较电路。

(4)动态范围取决于VREF。

单片集成并行比较型A/D转换器的产品很多,如AD公司的AD9012(TTL工艺,8位)、AD9002(ECL工艺,8位)、AD9020(TTL工艺,10位)等。

5.改进方法

为了解决提高分辨率和增加元件数的矛盾,可以采取分级并行转换的方法。10位分级并行A/D转换原理如图11.9.2所示。图中输入模拟信号v1,经取样-保持电路后分两路,一路先经第一级5位并行A/D转换进行粗转换得到输出数字量的高5位,另一路送至减发器,与高5位D/A转换得到的模拟电压相减。由于相减所得到的差值电压小于1VLSB,为保证第二级A/D转换器的转换精度,将差值放大25=32倍,送第二级5位并行比较A/D转换器,得到低5位输出。这种方法虽然在速度上作了牺牲,却使元件数大为减少,在需要兼顾分辨率和速度的情况下常被采用。

图11.9.2 分级并行转换10位A/D转换器

-

数字电子技术基础:并行比较型ADC#数字电子技术学习电子 2022-11-14

-

ADC学习知识整理2018-03-30 0

-

FPGA驱动并行ADC&DAC2020-09-27 0

-

模数转换器(ADC)的基本原理是什么2021-07-26 0

-

基于RoboMasterC型开发板的ADC测量电压实验2023-02-08 0

-

全并行A/D转换器中电压比较器的设计2010-08-16 647

-

比较ADC的孔径延迟2006-03-24 2510

-

并行编码模数转换器(ADC),ADC的基本原理2010-03-24 2872

-

多比较器快速(Flash)ADC,什么是多比较器快速(Fla2010-03-24 3146

-

什么是逐次比较型adc?逐次比较型adc原理分析2017-11-26 25588

-

单片机的逐次比较器ADC转换原理的详细资料说明2019-12-31 1177

-

如何使用FPGA驱动并行ADC和并行DAC芯片2022-04-21 6075

-

并行接口的ADC、DAC的测试方法2023-11-07 1037

-

如何使用FPGA驱动并行ADC和并行DAC芯片?2024-02-22 2150

全部0条评论

快来发表一下你的评论吧 !