什么是逐次比较型adc?逐次比较型adc原理分析

转换器

描述

1、什么是逐次比较型ADC?

ADC,Analog-to-Digital Converter的缩写,指模/数转换器或者模数转换器。是指将连续变化的模拟信号转换为离散的数字信号的器件。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。与之相对应的DAC,Digital-to-Analog Converter,它是ADC模数转换的逆向过程。ADC最早用于对无线信号向数字信号转换。如电视信号,长短播电台发接收等。

adc模块的精度一般有8位、10位、12位、16位、24位。

以5V的ADC模块为例介绍:

8位的精度:把0~5V分成256份,每份表示5/256=0.02V;

10位的精度:把0~5V分成1024份,每份表示5/1024=0.005V;

12位的精度:把0~5V分成4096份,每份表示5/4096=0.0012V;

16位的精度:把0~5V分成65536份,每份表示5/65536=0.000076V;

24位的精度:把0~5V分成16777215份,每份表示5/16777215=0.00000023V;

2、逐次比较型ADC电路结构

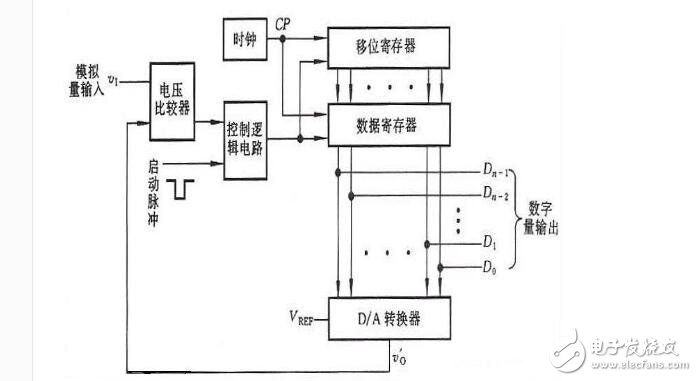

逐次逼近ADC包括n位逐次比较型A/D转换器如下图所示。它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。

逐次比较型A/D转换器框图

3、逐次比较型ADC特点

(1)转换速度:(n+1)Tcp.速度快。

(2)调整VREF,可改变其动态范围。

(3)转换方式:直接转换ADC

4、逐次比较型ADC工作原理分析

逐次比较型ADC原理是从高位到低位逐位比较,首先将缓冲寄存器各位清零;转换开始后,先将寄存器最高位置1,把值送入D/A转换器,经D/A转换后的模拟量送入比较器,称为 Vo,与比较器的待转换的模拟量Vi比较,若Vo《Vi,该位被保留,否则被清0。然后,再置寄存器次高位为1,将寄存器中新的数字量送D/A转换器,输出的 Vo再与Vi比较,若Vo《Vi,该位被保留,否则被清0。循环此过程,直到寄存器最低位,得到数字量的输出。

逐次逼近转换过程和用天平称物重非常相似。天平称重物过程是,从最重的砝码开始试放,与被称物体行进比较,若物体重于砝码,则该砝码保留,否则移去。再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。照此一直加到最小一个砝码为止。将所有留下的砝码重量相加,就得此物体的重量。仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。

对11.10.1的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。输入电压首先与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI《 VREF/2,则为0。比较结果存于数据寄存器的Dn-1位。然后在第二个CP作用下,移位寄存器的次高位置1,其他低位置0。如最高位已存1,则此时 vO=(3/4)VREF。于是v1再与(3/4)VREF相比较,如v1≥(3/4)VREF,则次高位Dn-2存1,否则Dn-2=0;如最高位为0,则vO=VREF/4,与vO比较,如v1≥VREF/4,则 Dn-2位存1,否则存0……。以此类推,逐次比较得到输出数字量。

为了进一步理解逐次比较A/D转换器的工作原理及转换过程。下面用实例加以说明。

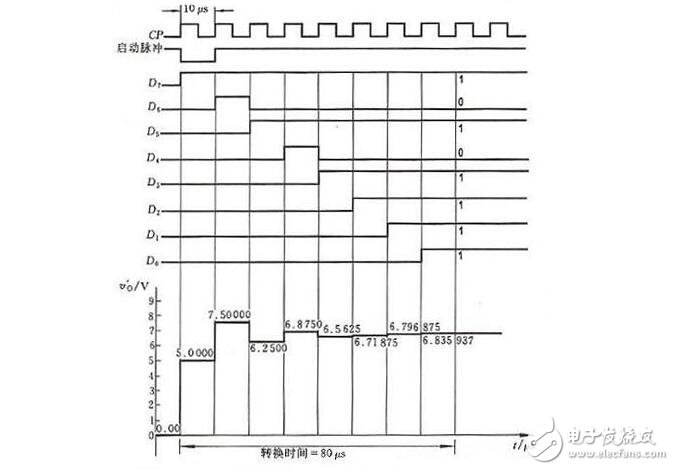

设下图电路为8位A/D转换器,输入模拟量vA=6.84V,D/A转换器基准电压VREF=10V。 根据逐次比较D/A转换器的工作原理,可画出在转换过程中CP、启动脉冲、D7~D0及D/A转换器输出电压vO的波形,如图11.10.2所示。

由图11.10.2可见,当启动脉冲低电平到来后转换开始,在第一个CP作用下,数据寄存器将D7~D0=10000000送入D/A转换器,其输出电压 v0=5V,vA与v0比较,vA》v0存1;第二个CP到来时,寄存器输出D7~D0=11000000,v0为7.5V,vA再与7.5V比较,因vA《7.5V,所以D6存0;输入第三个CP时,D7~D0=10100000,v0=6.25V;vA再与v0比较,……如此重复比较下去,经8个时钟周期,转换结束。由图中v0的波形可见,在逐次比较过程中,与输出数字量对应的模拟电压v0逐渐逼近vA值,最后得到A/D转换器转换结果D7~D0为10101111。该数字量所对应的模拟电压为6.8359375V,与实际输入的模拟电压6.84V的相对误差仅为0.06%。

8位逐次比较型A/D转换器波形图

5、逐次比较型ADC转换器电路举例

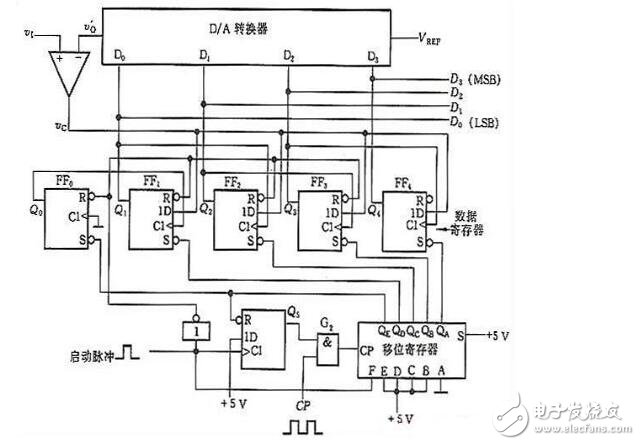

例11.10.1 4位逐次比较型A/D转换器的逻辑电路如下图所示。图中5移位寄存器可进行并入/并出或串入/串出操作,其F为并行置数端,高电平有效,S为高位串行输入。数据寄存器由D边沿触发器组成,数字量从Q4~Q1输出,试分析电路的工作原理。

4位逐次比较型A/D转换器的逻辑电路

电路工作过程分析:

当启动脉冲上升沿到来后,FF0~FF4被清零,Q5置1,Q5的高电平开启G2门,时钟CP脉冲进入移位寄存器。在第一个CP脉冲作用下,由于移位寄存器的置数使能端F已有0变为1,并行输入数据ABCDE置入,QAQBQCQDQE=01111。QA的低电平是数据寄存器的最高位置1,即Q4Q3Q2Q1=1000。D/A转换将数字量1000转换为模拟电压vO,送入比较器C与输入模拟电压v1比较,若输入电压vI》 vO,则比较器C输出vC为1,否则为0。比较结果送D4~D1。

第二个CP脉冲到来后,移位寄存器的串行输入端S为高电平,QA由0变1,同是最高位QA的0移至次高位QB。于是数据寄存器的Q3由0变1,这个正跳变作为有效触发信号加到FF4的CP端使vC的电平得以在Q4保存下来。此时,由于其他触发器无正跳变脉冲,vC的信号对它们不起作用。Q3变为1后建立了新的D/A转换器的数据,输入电压在与其输出电压vO相比较,比较结果在第三个时钟脉冲作用下存于Q3……。如此进行,直到QE由1变0,使Q5由1变0后将G2封锁,转换完毕。于是电路的输出端D3D2D1D0得到与输入电压v1成正比的数字量。由以上分析可见,逐次比较型A/D转换器完成一次转换所需的时间与其位数和时钟脉冲频率有关,位数愈少,时钟频率愈高,转换所需时间越短。这种A/D转换器具有转换速度较快,精度高的特点。

-

STM32f103ADC 用的是哪种方法2015-04-12 0

-

【零基础学习STM32】第九讲:ADC实验——电源监控2018-03-17 0

-

ADC学习知识整理2018-09-07 0

-

浅析adc的六种分类以及六大关键性能指标2019-01-04 0

-

浅析STM32 ADC的采集原理2019-07-08 0

-

12位逐次比较型AD转换器AD574A电子资料2021-04-08 0

-

模数转换器(ADC)的基本原理是什么2021-07-26 0

-

STM32 ADC知识总结2021-08-05 0

-

STM32 ADC的转换模式有哪几种2021-11-01 0

-

12位逐次逼近型ADC转换的原理是什么2022-02-25 0

-

八位逐次比较型模一数变换器2009-04-10 380

-

AD转换的基本原理和技术(逐次逼近型)2016-03-04 2994

-

单片机的逐次比较器ADC转换原理的详细资料说明2019-12-31 1177

-

逐次比较式模数转换器如何获取最佳采样频率2020-08-01 2764

-

CKS32F4xx系列ADC单通道电压采集的实现2023-07-21 461

全部0条评论

快来发表一下你的评论吧 !