资料下载

×

PCB中防止共阻抗干扰的地线设计解析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-28

电子电路中,共阻抗干扰对电路的正常工作带来很大影响。在PCB电路设计中,尤其在高频电路的PCB设计中,必须防止地线的共阻抗所带来的影响。通过对共阻抗干扰形式的分析,详细介绍一点接地在电子电路中,特别是在高频电路中对共阻抗干扰的抑制作用,以及采用一点接地防止共阻抗应注意的问题。

同时对PCB板内地线布局的主要形式和要求进行了简要阐述。

0前言

在电子电路中,多数元器件都要通过地线形成回路,线设计合理与否,直接影响电路的工作。尽可能地降低由于地线设计不和理产生对信号传输的干扰。

在电路图中,接地常用符号 来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗(电阻、电感)的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB设计中必须注意和消除地线阻抗的影响。

来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗(电阻、电感)的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB设计中必须注意和消除地线阻抗的影响。

1地线对电路产生干扰的形式

1. 1全电流共阻抗干扰

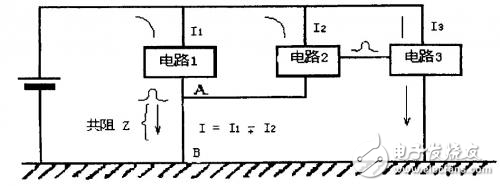

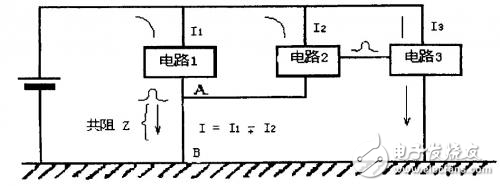

如图1中,电路1和电路2通过公用地线AB与电源形成回路。线段AB可等效为一个电阻和电感的串联回路,因而形成共阻抗效应。在工作时,电路1、2的电流变动,将引起A点电位变化,使电路1、2相互产生干扰。如电路2有输出至电路3,干扰也将窜入电路3中,因此形成全电流共阻抗干扰。

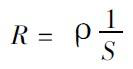

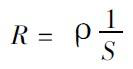

例如有一段长为10cm,宽为1. 5cm的印制导线,其铜箔厚度为50微米,导线电阻为:

若ρ= 0. 02,则R约为0. 026Ω。当电路1工作在低频时,电路的交变电流为1A,则在这段印制导线上约产生0.026V的交变电压降而作用在电路2上。在高频时,地线的共阻抗干扰,主要以导线的电感为主。当一段导线长度远大于其宽度时,导线的自感量可按0. 8微亨/米计算。同样一段长10cm的导线,当其通过的工作频率为30MHz时,此段导线所呈现的感抗RL= 2πL≈16Ω。可见在频率升高时,导线的感抗将比导线本身的电阻要大几个数量级。即使导线中流过很小的高频电流,如为10mA,在导线上将产生0.16V的高频电压。因而,对于高频电路,在制作PCB时,印制导线要尽可能短,以减少导线感抗对电路带来的损耗与干扰。

图1地线共阻抗干扰

同时对PCB板内地线布局的主要形式和要求进行了简要阐述。

0前言

在电子电路中,多数元器件都要通过地线形成回路,线设计合理与否,直接影响电路的工作。尽可能地降低由于地线设计不和理产生对信号传输的干扰。

在电路图中,接地常用符号

来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗(电阻、电感)的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB设计中必须注意和消除地线阻抗的影响。

来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗(电阻、电感)的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB设计中必须注意和消除地线阻抗的影响。1地线对电路产生干扰的形式

1. 1全电流共阻抗干扰

如图1中,电路1和电路2通过公用地线AB与电源形成回路。线段AB可等效为一个电阻和电感的串联回路,因而形成共阻抗效应。在工作时,电路1、2的电流变动,将引起A点电位变化,使电路1、2相互产生干扰。如电路2有输出至电路3,干扰也将窜入电路3中,因此形成全电流共阻抗干扰。

例如有一段长为10cm,宽为1. 5cm的印制导线,其铜箔厚度为50微米,导线电阻为:

若ρ= 0. 02,则R约为0. 026Ω。当电路1工作在低频时,电路的交变电流为1A,则在这段印制导线上约产生0.026V的交变电压降而作用在电路2上。在高频时,地线的共阻抗干扰,主要以导线的电感为主。当一段导线长度远大于其宽度时,导线的自感量可按0. 8微亨/米计算。同样一段长10cm的导线,当其通过的工作频率为30MHz时,此段导线所呈现的感抗RL= 2πL≈16Ω。可见在频率升高时,导线的感抗将比导线本身的电阻要大几个数量级。即使导线中流过很小的高频电流,如为10mA,在导线上将产生0.16V的高频电压。因而,对于高频电路,在制作PCB时,印制导线要尽可能短,以减少导线感抗对电路带来的损耗与干扰。

图1地线共阻抗干扰

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章