资料下载

×

基于VHDL语言的数字时钟的设计

消耗积分:0 |

格式:rar |

大小:1.3 MB |

2017-11-28

介绍了VHDL语言的特点及优势,表明了EDA技术的先进性,采用自上而下的设计思路,运用分模块的设计方法设计了数字时钟系统,并在QuartusⅡ环境下进行编译和仿真,完成了24 h计时和辅助功能设计,证明了方案的可行性,体现出了“硬件设计软件化”的新趋势。

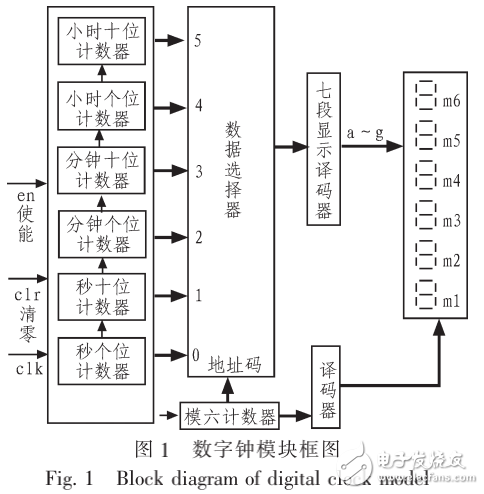

系统的模块框图

如图l所示,采用白顶向下的设计方法141,通过对功能框图的分析,将系统分模块来进行设计,然后冉通过例化语句完成各模块间的衔接,最终实现了顶层描述,完成系统预定功能。

系统的工作流程描述

如图1,时钟系统具有一个使能端en、一个异步清零端clr以及时钟脉冲输入端clk。由6个计数器分别完成小时、分钟、秒的计时,并分别通过数据选择器的6个输入端送入选择器,数据选择器的使能端由一个模为六的计数器控制,轮流选中数据选择器的6个输入端,这样,6个输入端口的数据在数据选择器的输出端口就得到了串行轮流的输出。此输出作为七段显示译码器的字符输入端,经译码后在数码管显示电路上显示m对应字形。数码管显示电路上的6个数码管同样采用轮流点亮的方式。南于循环的速度非常快,所以肉眼看起来仍然是同时显示的感觉。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章