什么是3D IC?它们有什么区别?

EDA/IC设计

描述

减少IC之间互连的长度可能会给移动系统应用的性能、功率和封装尺寸带来一种巨大的飞跃,主要动力就是3D IC。将一只移动处理器芯片与独立的存储芯片结合到一起,这是一种自然发展出来的3D结构。例如,三星电子公司推出了一款3D IC,该公司将一只存储芯片堆叠在硅片芯上,两者间采用了(垂直的)TSV(硅通孔)金属化孔,在芯片的顶部和底部都建立了连接(图1)。TSV技术能够实现一种广泛的I/O存储接口,较其它方案的功率降低多达75%,因为其互连与I/O电路的负载电容较小。

Tezzaron半导体公司专业从事存储器产品、3D晶圆工艺以及TSV工艺,它采用一种晶圆打线技术,在三个层面上堆叠芯片,该技术采用类似于US Mint的铜超级触点,用铜镍合金工艺制作波片。Tezzaron的Super-8051带堆叠存储的微控制器比普通8051微控制器的耗电低90%,因为它没有片外I/O。不过,制造商不能在打线以前做晶圆探测,因为探测会造成缺陷。

为了缓解3D堆叠IC的挑战,很多公司都在采用一种中间方式,即2.5D,用一种无源的硅中介层来连接各个片芯(图2)。包括Mentor Graphics公司首席执行官Walden Rhinies在内的很多业内人士都将2.5D方案看成是到达3D IC的一个缓慢上升的迁移路径。Rhines相信,2.5D方案的时间要比很多人的预期更长久,因为这种方案更多是演化,而不是革命。

Xilinx公司也在自己新的2.5D SSI(堆叠硅互连)FPGA中采用了这种方法,包括Virtex-7 XC7V2000T,它集成了四个FPGA片芯,相当于200万个逻辑门、46512 kbit的块状RAM、2160个DSP片,以及36个10.3125 Gbps的Xilinx GTX(千兆位收发器扩展)收发器(图3)。Xilinx在一个无源硅中介层上堆叠这些片芯,从而能够在FPGA之间做出1万多个互连。Xilinx公司首席技术官Ivo Bolsens表示:“SSI较其它方案在每瓦I/O带宽性能上提高了两个以上数量级,这再次说明了2.5D与3D在功耗与性能方面的差异。”

对于支持新3D IC项目的EDA工具的选择,可能会使实现设计的方式产生差别。尽管可以采用现有的2D IC工具,但如果增加一些应对3D设计挑战的技术还是有好处的。大多数主要EDA供应商都对3D IC采用一种谨慎的观望态度,不到最终不会给自己的2D工具增加功能。同时,很多较小的EDA供应商则正在建立面向3D设计的工具。例如,Tezzaron的3D PDK(工艺设计套件)就包含了新的以及已有的工具,能帮助将设计方法转向3D。

1 TSV的不足

Synopsys公司实现平台的产品营销经理Marco Casale-Rossi认为,3D IC的EDA工具开发必须起始于TCAD,用于建立TSV物理特性的模型。该公司的硅工程部已经与多家选定的合作伙伴做了这一工作。设计人员必须解决一个问题,即TSV会给靠近过孔开口处的有源硅区带来应力,这可能干扰电路的工作。在28nm工艺尺度时,“隔离区”(keep-out zone,即环绕一个TSV的区域,其中不能插入有源电路)可能要占据相当于约5000只晶体管的面积。Casale-Rossi称,如果在一只芯片上布放很多有相应隔离区的TSV,则片芯上会产生大量不可用的区域。Synopsys最近申请了一项解决TSV所产生应力的技术专利。该技术已不是TCAD软件,而是IP(智能产权),Casale-Rossi预测它将有助于减轻3D IC制造中的应力。该公司还申请了RLC建模(电阻/电容/电感)以及3D IC提取的专利应用。

Synopsys 3D IC物理实现工具的开发基础是其2D的布局与布线工具。Synopsys正在开发一种2.5D的设计工具,用于通过一个硅中介层连接多只用微凸块的倒装芯片。一个新出现的3D IC设计流将能在现有流程的每个阶段(从数字设计的综合与布局布线,到提取、物理验证以及时序签核)做到TSV感知(图4)。

2 增加平面规划级

由于现有EDA工具都不支持TSV的自动化布局与布线,因此必须用当前做2D IC设计的工具,手动地增加工具。据Cadence研究员Dave Noice称,要修改2D工具与设计数据库使之支持3D IC概念,会遇到很多挑战。例如,在2D设计中,第一个金属层(或叫metal-1)代表着一片IC上最低的互连层,但3D IC改变了这种布局,它增加了通过TSV做连接的背面金属层。

过去,设计者能够用Cadence的Encounter数字实现工具,自动地为倒装芯片布线,在凸块管脚与I/O处做45°的走线。Cadence还增强了该功能,能支持同时在片芯的顶面和底面的I/O走线。在平面规划与布局阶段给一只芯片增加了TSV以后,下一个挑战将是连接分配。布线工具必须能够分配连接,并优化通过TSV连接到背面凸块的线长。Noice表示,有些用户错误地认为布线器可以布放TSV,其实设计者只能用布线器做连接。在一个堆叠片芯的结构中,设计者的灵活性限制了平面规划,无论是为一只新ASIC增加TSV,还是为采用某种3D封装而修改设计。

对于3D IC设计,Cadence的平面规划工具将这一问题看作一种普通的层次式2D设计。该工具会将每只片芯看作一个独立的子块。例如,如果用一个确定制造工艺来堆叠存储片芯,则片芯“所有者”可以看到用于设计优化的垂直连接界面,但只能编辑自己一侧的TSV堆。

Magma设计自动化公司正在扩展自己的Hydra平面规划工具,它将一只3D芯片看成一组2D块去作物理实现,从而实现3D设计的自动化。据Magma公司首席技术师Patrick Groeneveld称,将一个3D设计划分为2D部件会导致一系列新问题,如设计分区、TSV分配、跨片芯的接口、电源与地的分布,以及相应的IR降与温度分析等。

3 定制工具

一家私有EDA公司Micro Magic的销售与营销经理Mark Mangum认为,3D IC设计工具的市场一直过于狭小,无法吸引大型EDA公司的投入。该公司过去四年来从其开发合作伙伴获得了3D设计专利,一直在做Max-3D布局工具(参考文献5)。Mangum称,普通的布局工具无法处理用于2D设计的传统方案,即将所有独立的数据组织成为一个大文件。而Max-3D则能够在每个晶圆级上维护技术文件,并有一个用于TSV互连的独立文件(图5)。处理器与存储器设计者的工程团队(在3D IC项目中很常见)就可以分别做3D堆叠中自己的一部分,然后再做最终集成。

在3D IC数据库组装以后,必须验证自己的设计,方法是追踪TSV在整个堆叠上的连接,并做完整的DRC(设计规则检查)与LVS(布局与逻辑图对照)检查。有时必须采用2D的物理验证工具,但Max-3D通过与Mentor Graphics的Calibre DRC与LVS工具的整合,消除了这个过程。Micro Magic还与Magma合作,将Magma的Quartz LVS与DRC工具整合到Max-3D中。Magma公司的Groeneveld称,Quartz的未来改进将使用户能够直接采用多种工艺描述,这对3D IC是必需的。采用Quartz LVS,一次运行就可以检查每只2D芯片,以及它们之间的3D互连(图6)。要在一个3D技术文件中,指定层数与顺序、互连材料,以及其它物理参数。然后,对3D IC的连接做一个TSV感知的提取。用Quartz中的调试环境,分析任何LVS的失配问题。

Magma计划与顾客和制造商合作,为Quartz增加3D DRC功能,定义TSV验证设计所必需的规则、设计以及库信息。Groeneveld称,Magma还在做几个其它的3D IC项目,如新增功能使用户能够使用内置Quartz DRC与LVS检查的Titan定制IC布局编辑器,一次对多只片芯做虚拟化和编辑。

Micro Magic的Mangum表示,设计者通常不愿意去转换工具,或改变自己的2D流程,因此,如果可以将一个普通IC布局工具用于自己的3D设计,他们就会这么做。然而,在某些时候,普通工具无法应付处理所需数据库的规模。该公司已对多达1万亿晶体管的设计验证了Max-3D,设计者也已用该工具开发了数据库多达60GB~80GB的设计。Max-3D会在数据变得非常大时,接管3D设计工作,从而成为常见2D IC布局工具,如Cadence的Virtuoso的补充。Micro Magic公司提供对Si2(硅集成行动组织)OpenAccess联盟OpenAccess数据库格式的全面支持,以协助设计流程的整合与互操作,这一数据库格式的目的是提供互操作性,包括通过一种开放标准的数据API(应用编程接口)以及在IC设计中支持该API的参考数据库,实现IC设计工具之间的统一性数据交换。

4 3D分区的设计工具

现在,制造商们提供用于3D IC早期规划和分区的工具。例如,Atrenta公司在SpyGlass-Physical Advanced工具中提供RTL(寄存器传输级)原型技术,用于3D IC的早期规划与分区。2D的Atrenta SpyGlass工具使设计者能够在设计周期的前期就开始做物理实现的可行性分析,此时RTL可能还未完成。可以用它对多个平面规划配置做虚拟化与评估,分析实现的可行性,选择适当的硅IP,创建物理分区,以及生成针对IP和SoC(系统单芯片)实现的实现指导(图7)。

对于3D IC,Atrenta与曾经的Javelin Design Automation公司做了较早的尝试(与IMEC和高通共同完成)。Atrenta最近揭幕了一处R&D设施,主要专注于3D技术以及先进节能技术的开发。当IMEC与Javelin开始与高通合作3D IC工作时,首要的挑战是必须能够在系统级了解一个设计。IMEC首席科学家Pol Marchal表示:“我们必须找到一种能跨多级对设计分区的方式,并了解TSV对整个设计的影响,这样我们才能做一些早期的平面规划。”他说,IMEC能够很容易地将Atrenta的SpyGlass转而用于3D设计。

Atrenta公司研究员Ravi Varadarajan说,为探索与优化3D设计,你需要一种能了解堆叠片芯结构以及工艺技术的工具。在设计过程开始时(Atrenta把它叫做逻辑探路),必须要获得设计者的意图。Atrenta将每个片芯看成一个统一的2D分区,所有工作均基于OpenAccess API与数据库格式。

Atrenta还与IMEC在一个alpha项目上展开合作,该项目将使设计者能够将平面规划的结果送入一个热仿真引擎。现有3D IC的热分析商业工具有Gradient公司的HeatWave等。IMEC正在开发自己的工具,从而能够使用从测试设备获得的测量数据,方便地校正热分析模型。IMEC还开发了自己的工具,与Atrenta的工具一起做机械应力分析,Marchal认同Synopsys关于在3D设计早期评估应力效果的重要性。

新兴的Monolithic 3D公司主要工作是针对3D IC的开发工具与制造技术。该公司正在做用于2D和3D IC的3DSim系统级设计规划仿真器。它可处理各种输入,如晶体管参数、互连材料、3D堆叠层的数量,以及封装等,开发出单根导线、逻辑门、电源分布、散热以及时钟分配等模型。也可以用3DSim研究对3D IC的设计折中。Monolithic公司提供开源Java的工具,可以在该公司网站上直接运行。

5 测试3D堆叠

测试问题是3D堆叠片芯的另外一个挑战。Mentor Graphics硅测试产品的营销总监Stephen Pateras称,该公司正在应对这一挑战,并认为在3D IC的测试中有三大问题:确认好片芯,在封装堆叠中后为需重测片芯提供通道,以及为封装内做片芯间互连的TSV提供通道。考虑到实用中做晶圆级彻底测试的成本与复杂性,单芯片封装内的某些元件将不可避免地无法满足规格要求。产量损失会成为产品工程师成本方程的组成部分,他们必须决定ROI(投资回报)是否足以支撑对已封装片芯测试的额外成本。对于3D IC,这些挑战改变了测试的经济性,因为一只片芯的失效就意味着必须废弃那些好的片芯。

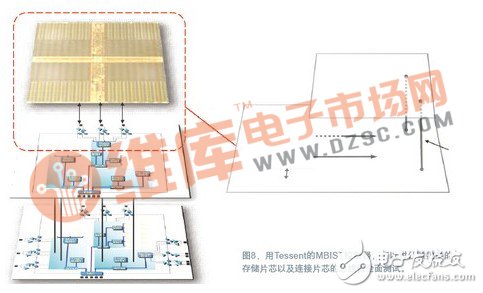

Mentor Graphics公司的Tessent硅测试平台提供针对一只片芯中所有部件的嵌入式BIST(内置自检)的工具,包括逻辑、存储器以及混合信号与高速I/O。采用BIST方案可免除对通道的担忧,而采用一个低速的JTAG(联合测试工作小组)IEEE-1149.1端口。

IEEE标准1149.1-1990定义了IC中用于辅助测试、维护以及已组装PCB(印刷电路板)的内置电路。该电路有一个标准化接口,系统通过该接口传送指令与测试数据。它定义了一组测试功能,包括一个边界扫描寄存器,这样元件就可以响应一个最小的指令集,辅助对已组装PCB的测试。

采用BIST和ATPG(自动测试模式生成),就可以对一只芯片中的各个块,同时做分层的实际测试。这种方案并不新鲜,但对3D IC是一个关键,因为一个堆叠芯片内的中间片芯没有与外部的连接。因此,就不能连接扫描测试的输入与输出。这一约束给3D设计带来了新的需求:必须使用所谓的测试电梯,重新布放到TSV的测试通道。IMEC已向IEEE提交了这个架构,作为1149.1规范的一个扩充。采用测试电梯结构,就必须在整个片芯堆叠中,包含将3D连接转换为测试模式的走线与逻辑。设计要求改变了,因为这种方案意味着一个堆叠中的菊链式测试逻辑。使用测试电梯时,可以在一个片芯上使用多工器,传送来自其它片芯的测试模式。另外,你可能还需要结合来自多个片芯的测试模式。Mentor Graphics的Tessent工具有新的3D功能,能够插入测试电梯,以及可能需要重新确定原本用于一只片芯的测试序列的逻辑,允许通过一个TSV发送各个模式做重新测试。

Pateras说,Tessent对待3D片芯堆叠问题的方式是类似于在单只片芯中的2D层次式测试。层次式测试可单独地处理一个片芯中的每个块,然后在顶层重新排列模式的顺序。可以采用“灰盒子”测试技术,即了解设计测试用例的内部数据结构以及算法。这种方案可以用于多片芯情况(而不是一只片芯中的多个IP块),因此现在一个Verilog网表就能覆盖全部封装。

设计者可以采用Tessent的MBIST(存储器BIST)控制器,对任意数量的存储片芯以及连接它们的总线做完整的测试(图8)。该公司的3D功能能够在一只逻辑芯片上集成MBIST电路(独立于DRAM片芯)。可以使用共享总线功能,支持多个存储片芯,并使用后硅片的可编程能力,支持设计变更。这种方案能够针对不同应用,在一个逻辑芯片上支持堆叠存储器的变动,以及当存储器大小与性能规格发生变化时,支持对测试要求的修改。另外,还可以测试一个通过TSV与其它片芯逻辑相连接的片芯。这个功能同时提供了水平2D和垂直3D的扫描插入方法。

IMEC的3D IC首席科学家Erik Jan Marinissen称,3D IC的测试必须解决三大类挑战。

首先,必须确定需要测试什么,以及在制造周期中何时何地做这种测试。

接下来必须解决的问题是有关3D处理步骤以及TSV互连可能会造成的新缺陷。

第三大挑战是测试通道问题。

IMEC对3D IC可测试性工具的工作包括与Cadence的合作,IMEC与Cadence在发布新闻时曾计划在2011年设计自动化大会上做演示,大会预定在圣地亚哥举办。Marinissen也是IEEE标准委员会P1838项目的工作小组组长,P1838项目是:关于三维堆叠集成电路的测试通道架构的标准。在一份有关3D IC设计挑战的白皮书中,Cadence表示,需要更多的经验性数据,才能确定对新缺陷模型的需求。虽然2D IC缺陷(如开路、短路、静电、延迟以及桥接缺陷)可能也适用于3D IC,但3D技术需要一种新的方法,将TSV缺陷映射到已知缺陷类型上。为满足3D可控制性以及可观测性目标,Cadence还指出,跨多片芯的DFT(可测试性设计)资源的智能分配非常关键。

-

EMPro和HFSS有什么区别?2019-02-28 0

-

ucos和freertos它们有什么区别2020-05-28 0

-

VCC、VDD和VSS它们有什么区别呢?2021-04-13 0

-

连接器的基本性能可分为哪几类?它们有什么区别?2021-05-14 0

-

3D显示技术的原理是什么?有哪些应用?2021-05-31 0

-

投影显示技术有哪几种?它们有什么区别?2021-05-31 0

-

3D软件中实体建模与曲面建模有什么区别?2021-06-05 0

-

MCP和eMCP它们之间有什么区别和联系?2021-06-18 0

-

KEIL、uVision、MDK、KEIL C51、RealView它们到底有什么区别?2021-07-01 0

-

什么是USART和UART以及它们之间有什么区别2021-12-09 0

-

CC2530具有哪几种功耗模式?它们之间有什么区别?2022-01-25 0

-

MCU程序常用的烧录方式有哪些?它们之间有什么区别?2022-02-21 0

-

Linux的2种显示方案它们有什么区别呢2022-03-07 0

-

LSM303AH与ISM303DAC它们之间有什么区别?2022-12-08 0

-

什么是CDMA短码?它和CDMA长码有什么区别?它们有什么用2009-06-01 4970

全部0条评论

快来发表一下你的评论吧 !