soc低功耗设计技术有哪些?汇总分析

控制/MCU

描述

SoC的定义多种多样,由于其内涵丰富、应用范围广,很难给出准确定义。一般说来, SoC称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。

soc定义

SOC,或者SoC,是一个缩写,包括的意思有:

1)SoC:System on Chip的缩写,称为芯片级系统,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。

2)SOC: Security Operations Center的缩写,属于信息安全领域的安全运行中心。

3)民航SOC:System Operations Center的缩写,指民航领域的指挥控制系统。

4)一个是Service-Oriented Computing,“面向服务的计算”

5)SOC(Signal Operation Control) 中文名为信号操作控制器,它不是创造概念的发明,而是针对工业自动化现状提出的一种融合性产品。它采用的技术是正在工业现场大量使用的成熟技术,但又不是对现有技术的简单堆砌,是对众多实用技术进行封装、接口、集成,形成全新的一体化的控制器,可由一个控制器就可以完成作业,称为SOC。

6)SOC(start-of-conversion ),启动转换。

7)short-open calibration 短开路校准。

SOC器件的功耗分析

低功耗研究都从分析功耗的来源入手,主要立足于晶体管级,CMOS功耗可分为三部分,一部分是电路在对负载电容充电放电引起的动态功耗,另一部分是由CMOS晶体管在跳变过程中的短暂时间内,P管和N管同时导通而形成电源和地之间的短路电流造成的功耗,第三部分是由漏电流引起的静态功耗。式(1)、(2)是SoC功耗分析的经典公式:

其中f是系统的频率;A是跳变因子,即整个电路的平均反转比例;C是门电路的总电容;V是供电电压;是电平信号从开始变化到稳定的时间。

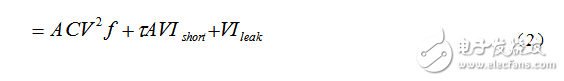

1.跳变功耗

跳变功耗是由每个门的输出端电容充放电形成的,以反相器为例,如图1所示,设Vin是周期为T的方波(上升和下降时间很小,忽略不计),当输入端Vin从高电平变为低电平时,P管逐渐打开,而N管逐渐闭合,所以电源端Vdd给电容CL充电,Vout逐渐变为Vdd;当Vin从低电平变为高电平时,N管逐渐打开,而P管逐渐闭合,电容CL开始放电到地,从而形成跳变功耗。

一个周期包含两个跳变。输出端从0变为1时,电源端损失能量为

22/VCddL,通过P管时,能量消耗于阻性通路,以热量形式释放;当输出端从1变为0时,存储在电容LC上的22/VCddL通过N管时转化成热能。当考虑所有晶体管时,公式(3)就变为公式(2)中的第1项。

因此跳变功耗主要研究器件工艺的工作电压如何降低,单元器件负载电容如何减小,部件工作频率如何降低,电路活动因子如何减小等。

2.短路功耗

短路功耗也叫直通功耗。如图2所示,Vin在高、低电平间不断变化的过程中,当VTn 《 Vin 《 Vdd-|VTp| 时(VTn为N型管导通电压值,VTp位P型管导通电压值),N管和P管都导通,从而有Vdd到Ground的通路,形成短路电流。短路功耗的公式是:

其中为电平信号从开始变化到稳定的时间,由电路的工艺决定,ddV和tV分别表示器

件电源电压和阈值电压,T表示电路的跳变周期。

公式(4)是假设LC对短路电流没有影响下推导出的,实际上当LC变大时所需要放电时间延长,如果比输入端的上升和下降时间长得多,它就不能完全放电,故功耗也会减少。反之,LC很小,就会导致相对于输入端的上升和下降时间太短,功耗会增大,所以半导体器件都设计成输入和输出端的上升和下降时间相当。

降低短路功耗主要包括如何降低器件工作电压,如何提高晶体管导通阈值电压,以及如何改善电路工艺等。

3.漏电功耗

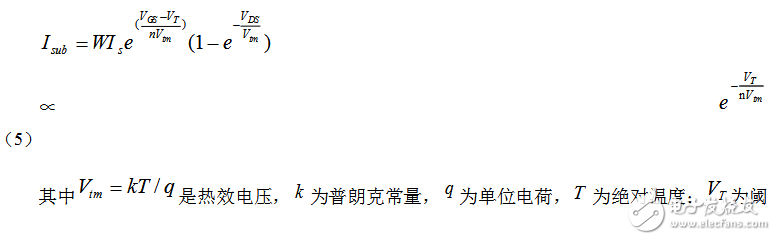

漏电功耗包括由寄生反向PN结漏电和亚阈区漏电引起的功耗,其中寄生反向PN结漏电引起的功耗很小,可忽略不计,而亚阈区漏电流的公式如下:

值电压。从公式(5)可看出,亚阈区漏电流与阈值电压有密切关系。当阈值减小时,亚阈区漏电流会呈指数级快速增大。漏电功耗研究表明其与每个门器件的输入向量控制相关,在0.13微米后的工艺中,漏电功耗研究重点是输入向量控制技术。

SOC的低功耗技术

功耗基础研究表明,功耗的降低是有限度的。首先是要限定在性能的约束范围内,否则功耗的降低可能会导致性能的大幅度降低。SoC低功耗的设计应该从顶层到底层各个阶段进行优化设计的工作,主要运用各级的低功耗策略,如工艺级低功耗技术、电路级低功耗技术、逻辑(门)级低功耗技术、RTL级(寄存器传输级)低功耗技术、体系结构级低功耗技术、算法级低功耗技术、系统级低功耗技术等。

1.工艺级低功耗技术

在当前工艺水平,SoC功耗主要由跳变功耗引起,而从公式(2)得知,通过降低电源供电电压,可以减少跳变功耗,这也是为什么集成电路由原来的5V供电电压降为3.3V,又降为后来的1.8V以及1.3V甚至更低。但降低供电电压会面临一些问题,因为如果阈值电压不变,噪声容限(noise margin)将会减小,抗干扰能力减弱,信号传送准确性就会降低。为保持相当的噪声容限,阈值电压要随供电电压的减少而相应的减少。然而,当进入0.13微米工艺后,从公式(5)可看出,阈值电压的减少会导致静态功耗呈指数级增长。

因此用降低电压的方法来降低功耗,必须用其它的方法补偿相应的延迟损失,以避免系统性能下降。一个方法是通过开发系统的并行性和流水线;第二种方法:根据用户对电路性能的不同要求,通过操作系统动态控制时钟频率和电源电压,达到既保证性能要求,又节约功耗的目的;第三种方法:根据性能的要求,实时改变供电电压,在系统的关键路径上,保持较高的电压,以保证整个系统的性能,而在非关键路径上,降低电压以减少功耗。

此外,还可以通过更新工艺降低功耗,如多阈值工艺MTCMOS (Multi-Threshold VT CMOS)和变阈值工艺VTCMOS (Variable Threshold VT CMOS) 。前者在关键路径上采用阈值较低的器件,而在非关键路径上用高阈值器件。虽然会因此增大延迟,但由此换得漏电功耗的降低;后者采用动态改变衬底偏置电压以改变阈值。工作期间,n型阱(N well)偏置电压维持在Vdd,p型阱(P well) 偏置电压维持在0;当待机或者需要低频工作时,N well偏置电压维持在2Vdd,P well 偏置电压维持在1Vdd,这样也可以通过高阈值达到减少漏电功耗的目的。工艺的进步,会使晶体管长宽尺寸持续减少,互连线长度减小,电容减小,从而大大有助于降低SoC功耗。

2.电路级低功耗技术

SoC中总线的数据线和地址线一般都比较多,比较长,每条线都需要驱动负载,通常占总功耗的15~20%,有的甚至70%以上[3],因而总线低功耗技术是我们关注的焦点之一。

减摆幅是目前比较成熟的技术,其原理是当输出端的输出电压的高电平是Vswing时,跳变功耗部分就是:

因此降低Vswing 可以达到降低功耗的目的,利用Domino逻辑电路已经可以解决这个问题。

电荷再循环总线结构(Charge Recycling Bus)是另外一种降低总线功耗的技术,它把整个电势差分成几等分,利用总线各数据位电容上存储的电荷电势的变化来传输数据,本质上也是利用了减摆幅技术。试验证明,其功耗可以是传统技术的10%。

3.门级低功耗技术

SoC在深亚微米时代,主要通过低电压实现低功耗技术,互补CMOS在许多方面都占有很大的优势,并且各EDA厂商也提供很完善的支持,因此在多数情况下,都选择互补CMOS。传输门在很有限的范围内有其优越性,如全加电路(Full Adder)在高电源电压时功耗低于互补CMOS,在用CPL实现乘法器时,也有很大优点。

4.寄存器传输级(RTL)低功耗技术

RTL低功耗技术主要从降低不希望的跳变(glitch--Spurious switch, hazards)入手,这种跳变虽然对电路的逻辑功能没有负面的影响,但会导致跳变因子A的增加,从而导致功耗的增加。

降低glitch的方法主要是消除其产生的条件,如延迟路径平衡、用时钟信号同步减少glitch、结构重构等。减少延迟不平衡的延迟路径的级数,可以极大地降低glitch。例如16位乘法器,如果采用每位进位运算算法,则最大延迟要用15拍,最少延迟是1拍,因而可能会产生大量的glitch,但如果用Wallace tree体系结构乘法器,可以有效平衡延迟路径级数,从而有效减少glitch。

在电路中插入由时钟信号控制的触发器将待传递的信号同步[8],可以将触发器前面的glitch阻隔在触发器处,避免其层层传递导致glitch爆炸。但此时需要权衡引入时钟树和触发器增加的功耗和面积与得到的改善相比是否值得。

结构重构是利用在电路中插入缓冲(buffer)的方法来消除因路径延迟不同而引起的glitch。这种方法一方面需要精确得到器件和连线的延迟数值,在物理设计完成之前很难做到,另一方面,对工艺偏差很敏感,路径平衡的效果很容易偏离设计期望;还有一种较好的方法是电路中加入冗余电路,可以有效降低glitch,。加入冗余电路可以完全消除glitch对输出的影响,而且不改变原电路实现的功能,不过,冗余电路本身会增加一定的功耗。

5.系统级LP技术

系统级低功耗技术主要有门控技术,异步电路等。

门控时钟技术可以说是当前最有效的低功耗技术。如果没有门控时钟技术,相同的值在每个时钟周期上升沿到来时都会被重复加载进后面的寄存器中,这就使后面的寄存器、时钟网络和多选器产生不必要的功耗。在寄存器槽、时钟网络插入门控电路就可以控制和消除这些不必要的寄存器活动,大幅度降低功耗。

同步电路中的时钟树要消耗大量能量,例如国产通用CPU龙芯1号和龙芯2号的时钟树功耗分别占整个芯片功耗的30%和60%,虽然可采用门控时钟技术缓解,但仍不能从本质上解决问题。由于时钟频率需满足所有模块的正常工作,因此低速模块存在速度浪费。而异步电路的工作模式是“事件驱动”,电路只在需要时工作,因此消除了速度浪费,由于不需同步,没有全局时钟,因此也消除了全局时钟树功耗。

6.零翻转编码地址总线技术

SoC内部,总线上挂着很多功能设备,导致总线的电容负载很大。如果总线与片外设备联系,那么,它还要驱动很长的片外连线以及片外设备,负载高达50pF,比SoC内部各个节点的电容负载0.05pF高出三个量级。一般而言,总线的功耗占SoC总功耗的10%~80%;一个已经对内部电路优化过的SoC,总线功耗约占50%。随着宽度的增加,总线消耗的功率占SoC总功率的比重越来越大,因此,总线的低功耗设计很重要。

很多通过减少总线动态翻转来降低总线功耗的算法已经被提出来。数据总线的数据随机性较大,地址总线的地址向量连续性较大。它们传送的数值各有特点,所以,针对不同类型总线的算法也不一样。针对数据总线有bus-invert算法,针对地址总线有PBE(Page-Based Encoding)算法、WZE(Working Zone Encoding)算法等。

总线宽度为N,t时刻,总线需发送的数据为Bt。如果Bt与Bt-1相等,则时刻总线状态完全不变;如果Bt与Bt-1不相等,则t时刻,总线就会发生电平翻转。Bt与 Bt-1不同的比特位数目(0≤N)越大,总线电平翻转的位数就越多,功耗就越大。当Bt与Bt-1互为反码,则总线每一位都要翻转,此时总线翻转的功耗最大。

零翻转编码法利用降低总线的电平翻转次数,来降低总线功耗。定义bt为内核MCU计算出来的t时刻总线数据(即编码前的数据),Bt是t时刻已放到总线上的数据(即编码后的数据),Jt是解码器解码后的数据。

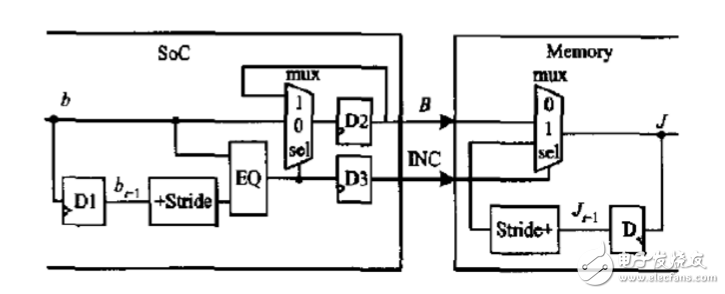

总线连续取址时,相邻两次地址的差是相等的,定义为Stride。一般的ROM寻址Stride=1;对Cache寻址时,Stride根据Cache的寻址特性而定。如果Cache寻址步长是一个word,则Stride=2。编码需要一个额外的状态信号INC。 零翻转编码的算法步骤如下:

计算bt-1+Stride,比较bt与bt-1+ Stride;

如果bt=bt-1+Stride,表明是连续寻址,那么Bt=Bt-1,置INC=1; 如果bt≠bt-1+Stride,表明是不连续寻址,那么Bt=bt,置INC=0; ④ 接收端解码器根据INC来处理收到的总线数据。 零翻转解码的算法步骤如下: 计算Jt-1+Stride;

如果INC=1,表明是连续寻址,那么Jt=Jt-1+stride; 如果INC=0,表明是不连续寻址,那么Jt=Bt。

中断和跳转子程序的多少,会影响功耗的降低。中断和跳转越少,地址向量连续性越高,零翻转编码后总线电平翻转越少,节省的功耗就越大。当地址总线一直连续寻址时,零翻转法理论上可以达到地址总线的零翻转,并且,Stride变量可以根据寻址对象的不同而设置成对应的数值。

零翻转编解码器电路结构:

编码器组成如图3左半部分。D1寄存bt-1,加法器将bt-1与Stride相加。比较器EQ比较bt和bt-1+Stride,输出INC。选择器MUX的两组输入是bt和Bt-1。

编码器是组合逻辑,不可避免的有毛刺。毛刺虽然时间很短,但依然会增加总线功耗,因此,利用D2、D3触发器来同步,过滤掉所有的毛刺。

解码器结构如图3右半部分,在接收设备Memory控制逻辑中实现。寄存器D存储Jt-1,MUX的两组输入是(bt-1+Stride)和Bt。它的结构比编码器简单得多。相对整个SoC而言,编码器和解码器的电路规模很小,带来的额外硬件面积和功耗也很小

图3.零翻转编码器和译码器

SoC低功耗设计技术远不止上述所述的各种方法,从上面的各种降低功耗的方法可以看出,SoC系统的功耗优化涉及到从物理实现到系统实现的方方面面,是芯片设计中一个十足的系统工程。目前,低功耗在学术界已经是一个很热门的研究领域,许多的科研工作者正在研究各种各样的解决方案。

-

480.SOC芯片的数字低功耗方法小凡 2022-10-04

-

蓝牙低功耗技术2011-05-13 0

-

SoC低功耗设计2012-08-13 0

-

【众拳】基于STM8的实验汇总分享2018-01-27 0

-

如何使具备蓝牙低功耗技术功能的设备真正的具备低功耗?2018-10-31 0

-

基于Foundation IP的低功耗IoT SoC实现2019-07-26 0

-

行业最低功耗蓝牙SoC NCV-RSL10有什么优势?2019-08-05 0

-

什么是nRF52840低功耗蓝牙技术?2019-09-11 0

-

如何选择正确的低功耗蓝牙SoC?2021-03-11 0

-

蓝牙低功耗有哪些特性和技术?2021-05-14 0

-

《SoC底层软件低功耗系统设计与实现》基于Linux专门讲解软件低功耗框架和设计的书籍2023-09-08 0

-

Cache结构的低功耗可重构技术分析2009-03-29 677

-

soc芯片上市公司汇总分析2017-12-13 50074

-

国产超低功耗华大MCU资料汇总2021-12-07 832

-

信号与系统的公式汇总分类2022-12-27 253

全部0条评论

快来发表一下你的评论吧 !