SAR型ADC原理简析

转换器

描述

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

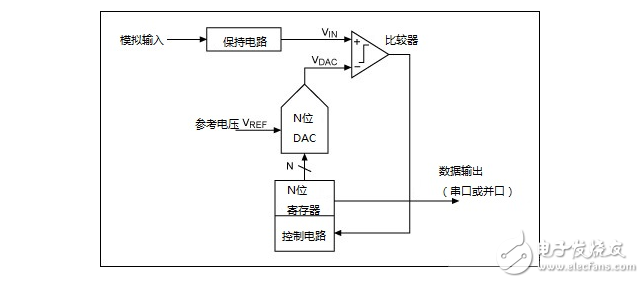

SAR ADC的架构

尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。模拟输入电压(VIN)由采样/保持电路保持。为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100.。。 .00,MSB设置为1)。这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。然后,比较判断VIN是小于还是大于VDAC。如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到LSB。上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

SAR型ADC原理简析

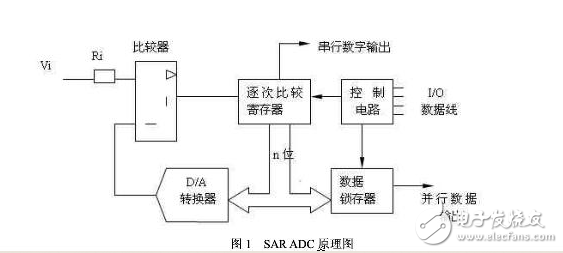

SAR原理框图:

组成:比较器、逐次比较寄存器、D/A转换器、数据寄存器、控制电路。

原理简析:首先逐次比较寄存器最高位置1,指示D/A转换器输出对应电压到比较器反相端与Vi比较,如果Vi大于该电压,则比较器输出为1,逐次比较寄存器采样到1保存最高位为1,反之为0。依次比较直到最后一位,届时所存数据并输出。

特点:从原理分析容易看出,该种ADC是一位一位比较,则每个时钟周期只能比较一次,N位则需比较N次,因此注定该种ADC不能运转在较快速度,同时输入端Vi的带宽也不会太宽,毕竟转换速率在那里了,你Vi变化太快,人家还没转换完你就变化了,转换还有啥意义呢?另一方面可看出该种ADC电路结构简单,硅片面积和功耗比较小,便于实现。同时分辨率完全取决于内部DAC(当然比较器的敏感度也很重要。),则可实现较高分辨率。总之,该种ADC适用于分辨率高、中等速度以下的场合。

网上搜索时无意中发现,然来教科书中常见芯片ADC0809即为SAR型,之前只知道拿过来就用,现在研究ADC才注意到。(后来使用C8051F410,发现集成的12位ADC竟然也是SAR型)

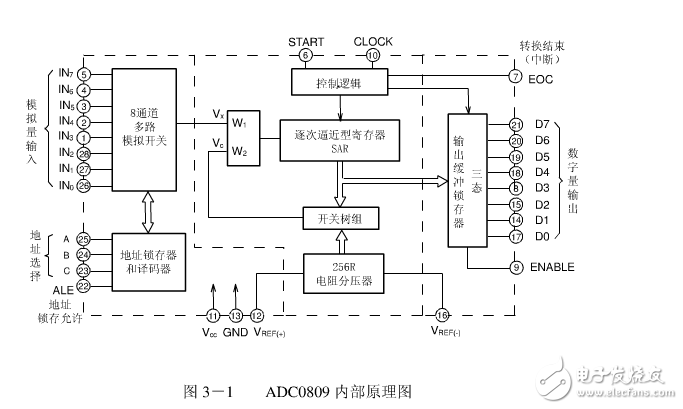

上ADC0809内部原理框图:

注意中间部分即之前所述SAR核心构成,不过这里是用开关数组和256R电阻分压器构成了一个DAC。

-

哈尔滨站-杨松岩:如何实现SAR型ADC系统的设计与调试(2)2019-08-08 1701

-

哈尔滨站-杨松岩:如何实现SAR型ADC系统的设计与调试(1)2019-08-08 2016

-

AD7960高精度SAR型ADC的性能演示2019-06-05 4930

-

SAR型ADC有哪几种输入类型?其区别是什么?2018-08-13 10187

-

AD7767超低功耗SAR型ADC的应用介绍2019-07-29 3764

-

AD7652:16位500 kSPS SAR单极ADC,带参考数据表2021-04-17 559

-

AD7651:16位100 kSPS SAR单极ADC,带参考数据表2021-04-25 540

-

标准的SAR型ADC驱动电路需要基准及驱动电路2022-01-14 1985

-

思瑞浦最新推出16位单通道全差分SAR型ADC2022-10-26 2052

-

SAR型ADC的驱动电路设计2022-11-09 2635

-

SAR型ADC的RC滤波器设计2022-11-09 2829

-

SAR型ADC的结构及采样过程2023-02-07 2642

-

高性能全集成SAR型ADC2023-03-31 768

-

贞光代理品牌 思瑞浦推出全新单通道16位/18位SAR型ADC2022-10-26 778

-

SAR型ADC的模拟输入模型、反冲电压和RC滤波器计算2023-09-14 1239

全部0条评论

快来发表一下你的评论吧 !