一种适用于RFIC的抗击穿LDMOS设计

RF/无线

1779人已加入

描述

LDMOS (Lateral Diffused MetalOxide Semiconductor Transistor,横向扩散金属氧化物半导体)以其高功率增益、高效率及低成本等优点,被广泛应用于移动通信基站、雷达、导航等领域。射频大功率 LDMOS由于具有P、L波段以上的工作频率和高的性价比,已成为3G手机基站射频放大器的首选器件。

随着IC集成度的提高及器件特征尺寸的减小,栅氧化层厚度越来越薄,其栅的耐压能力显著下降,击穿电压是射频LDMOS器件可靠性的一个重要参数,它不仅决定了其输出功率,还决定了器件的耐压能力,因此必须要采取措施以提高器件的击穿电压。

本文将在基本LDMOS的基础上,通过器件结构的改进来提高LDMOS的抗击穿能力。

1、LDMOS耐压特性

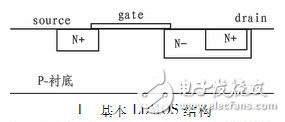

如图1所示,LDMOS最主要的结构特点是采用双扩散技术,在同一窗口进行磷扩散,沟道长度由两种扩散的横向结深决定。LDMOS中产生的击穿形式有栅绝缘层击穿和漏源击穿。

LDMOS高压器件是多子导电器件,由于漂移区将漏区与沟道隔离,Vds绝大部分降落在漂移区上,基本上没有沟道调制,所以当Vds增大时,输出电阻不下降。并且栅电极和漏区不重迭,从而提高了漏源击穿电压。

影响LDMOS耐压性能的因素很多,本文将从埋层、漂移区掺杂浓度、衬底掺杂浓度3方面进行分析各参数对其耐压性能的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

-

如何利用RFIC设计抗击穿LDMOS?2019-07-31 0

-

LDMOS介绍2020-05-24 0

-

一种适用于模拟/数字混合信号环境的接地技术2021-04-25 0

-

求大佬分享一款适用于激光及MRI的宽带LDMOS晶体管2021-06-08 0

-

怎样去设计一种适用于无刷直流电机的Simulink模拟器?2021-07-27 0

-

一种适用于嵌入式系统的模块动态加载技术2021-12-20 0

-

一种适用于空间观测任务的实时多目标识别算法分享2021-12-21 0

-

高压LDMOS功率器件的研究2010-02-23 509

-

一种适用于射频集成电路的抗击穿LDMOS设计2013-05-06 930

-

LDMOS耐压特性与射频集成电路的抗击穿LDMOS设计2017-10-13 1546

-

一种适用于RFIC的抗击穿LDMOS设计2017-11-23 448

-

一种适用于RFIC的抗击穿LDMOS设计文档2018-05-04 711

-

一种适用于RFIC的抗击穿LDMOS设计解析2018-05-03 2902

-

如何使用深阱工艺提高LDMOS的抗击穿能力2020-09-25 1000

全部0条评论

快来发表一下你的评论吧 !