资料下载

×

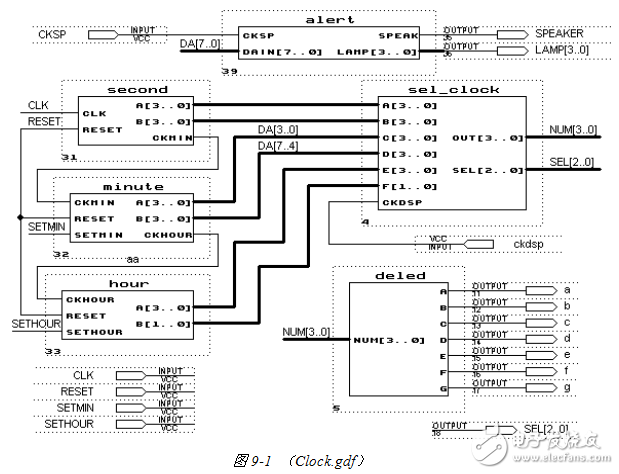

基于CPLD的数字钟的设计

消耗积分:0 |

格式:rar |

大小:0.1 MB |

2017-12-05

在同一CPLD芯片上集成了如下电路模块:

1、时钟计数:秒……60进制BCD码计数。

分……60进制BCD码计数。

时……24进制BCD码计数。

同时整个计数器有清零、调时、调分功能。在接近整数时能提供报时信号。

2、具有驱动8位8段共阴极扫描数码管的片选驱动信号输出和8段字形译码输出。编码和扫描可参考“实验四”。

3、扬声器在整点时有报时驱动信号产生(响声持续多长时间?)。

4、LED灯按个人口味在整点时有花样显示信号产生。

实验内容及步骤

1、根据电路特点,可在教师指导下用层次设计概念。将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口。让几个学生分做和调试其中之一,然后再将各模块和起来联试。以培养学生之间的合作精神,同时加深层次化设计概念。

2、了解软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合。

原理图 如图9-1所示(模块化设计)

模块说明

各种进制的计数及时钟控制模块(10进制、六进制、24进制);

扫描分时显示,译码模块;

彩灯,扬声器编码模块;

各模块都是AHDL语言编写。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

jiajianke

2017-12-08

0 回复 举报正在学习FPFA的知识。谢谢分享 收起回复

jiajianke

2017-12-08

0 回复 举报正在学习FPFA的知识。谢谢分享 收起回复

- 相关下载

- 相关文章