资料下载

×

基于款频率数字系统的低抖动八相位锁相环设计

消耗积分:3 |

格式:rar |

大小:0.65 MB |

2017-12-06

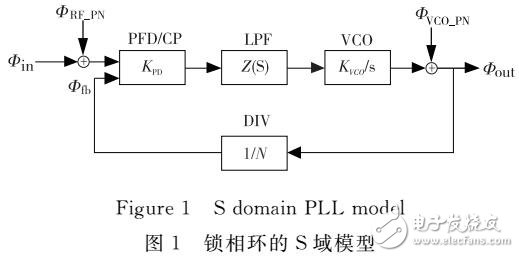

目前,锁相环大都采用经典的结构,虽然也能满足工业使用需求,但随着现代电子技术的发展,对于锁相环性能的要求越来越高,高频率、宽带宽、低功耗、低电压、低抖动、高稳定性等指标已成为人们研究锁相环的侧重点口]。电荷泵锁相环CPPLL(ChargePump Phase Locked Loop)是数模混合锁相环的典型代表,因其具有理论上零静态相位误差、高速、低功耗、低抖动等特征,成为目前使用最为广泛的锁相环。特别是多相位锁相环(Multiphase PhaseLocked Loop)精准的相位关系在时钟和数据恢复电路(Clock and Data Recovery)和高速串行传输(SerDes)领域备受关注。因此,锁相环如果可以在较宽频率范围内输出多相位且低抖动的信号,该锁相环就能够应用于更多集成电路。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章