基于PCI Core的链式DMA控制器设计

嵌入式设计应用

描述

摘 要:介绍一种基于PCI总线的高效链式DMA控制器的设计与实现,用于高速宽带的计算机外设接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的数据采集平台,并成功应用在DVB数据接收卡中。

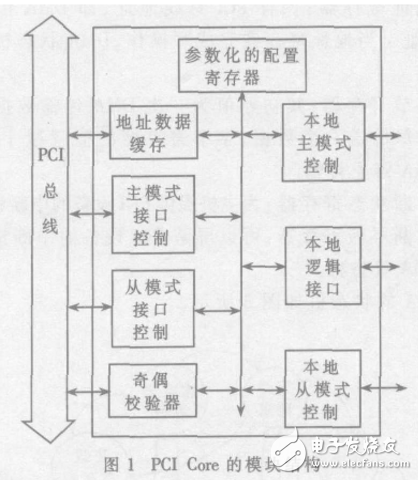

1991年PCISIG(外围部件互连专业组)成立,提出了PCI的概念Altera公司提供的软件包:PCICompiler可以参数化地生成用于PCI接口的IP核——Megacore。该IP核包含了PCI控制电路的所有功能,完成总线协议的转换,并将复杂的、电气和时序要求高的PCI转换为易于操作的本地接口逻辑。用户可以基于其生成的IP核模块,设计自己的外部设备接口逻辑。Altera的MegaCore包括四种类型:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。它们都具有灵活的通用接口,遵循PCI协议2.2版,严格的工业级验证和多款优化FPGA。考虑通常的PC主板都支持32位PCI,而且DMA控制器必须工作在主模式下,因此选择了PCI_MT32,其模块结构如图1所示。

·参数化的配置寄存器:保存PCI设备的基本信息,可以通过软件参数设定寄存器。

·地址数据缓存:缓存PCI总线上的地址数据。

·主模式接口控制模块控制模块:在主模式下对PCI总线的操作。

·从模式接口控制模块:在从模式下对PCI总线的操作。

·奇偶校验器:当校验出错时,生成一个报错信号输出到配置寄存器。

·本地主模式控制模块:主模式下,控制本地逻辑的接口。

·本地从模式控制模块:从模式下,控制本地逻辑的接口。

·本地逻辑接口模块:控制本地端接口的地址、数据、控制、字节使能等。

1DMA控制器

针对高带宽、低延时和大数据量的多媒体数据,设计了基于PCIcore的DMA数字卫星电视接收卡。DVB协议中的基本数据单元为192字节,因此把一次DMA传输的数据包定为192字节。

1.1DMA控制器的结构

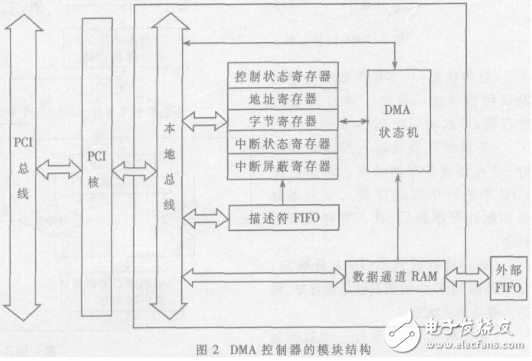

DMA控制器由DMA寄存器、描述符描述符FIFO、DMA状态机、数据通道RAM四个模块构成,如图2所示。

DMA寄存器是主机控制DMA的窗口,包括控制状态寄存器状态寄存器、地址寄存器、字节寄存器、中断状态寄存器和中断屏蔽寄存器。描述符FIFO是一个32×256的FIFO,在链式DMA模式下可以暂存128组DMA的描述符。DMA状态机是控制PCI总线数据传输的核心,主模式下的DMA有主模式写和主模式读两种类型。主模式写是把数据通道RAM里的数据包通过PCI总线传送到从设备,主模式读则读取从设备的数据包传送到数据通道RAM中。

1.2DMA寄存器

DMA寄存器的地址直接映射到PCI的地址空间,其基地址由PCICore中的配置寄存器Bar0决定。主机通过访问这些寄存器来控制DMA操作。

·控制状态寄存器:主机通过寄存器配置DMA状态机,同时也可以获得当前数据传输的状态。

·地址寄存器:保存PCI总线地址,即DMA传输的目标地址。当地址寄存器完成写操作,DMA状态机将被启动。

·字节寄存器:其初始值为一次DMA传输数据的大小,PCI每传送一个数据,字节寄存器的值就减1,减到0则DMA停止传输。

·中断状态寄存器:为主机提供PCI设备的中断状态。

·中断屏蔽寄存器:可以屏蔽PCI设备的中断请求。

1.3DMA状态机

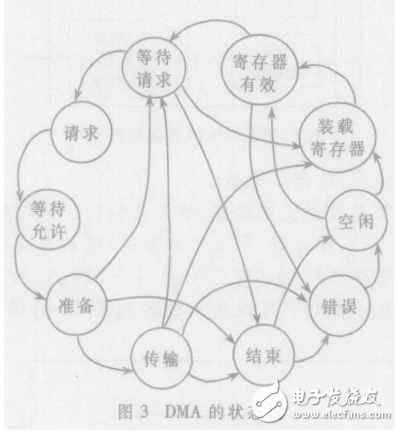

DMA的状态机如图3所示。

·空闲状态:状态机无数据传输时默认停留在这一状态。通过写DMA寄存器,可启动一次DMA传输。

·装载寄存器状态:当链式传输时,进入装载寄存器状态。将描述符FIFO中的一组描述符装入字节寄存器和地址寄存器后,进入寄存器有效状态。

·寄存器有效状态:DMA传输前,如果外部FIFO中的数据已经准备好,则进入等待请求状态。

·等待请求状态:等待一个数据包从外部FIFO送入数据通道RAM,进入请求状态。

·请求状态:申请PCI总线的控制权,进入等待允许状态。

·等待允许状态:当PCI设备获得了总线的控制权,进入准备状态。

·准备状态:当数据传输结束或者PCI总线终止传输,则进入结束状态;当PCI总线插入等待周期,则返回等待请求状态,重新申请总线的控制权;当PCI总线的地址期结束将要进入数据期,则进入传输状态。

·传输状态:当数据传输结束或者PCI总线终止传输,则进入结束状态;当PCI总线插入等待周期,则返回等待请求状态,重新申请总线的控制权;当本次数据传输结束,但是本次链式DMA没有结束,则进入装载寄存器状态。

·结束状态:一次DMA结束,或者一次链式DMA结束,状态机进入结束状态,同时发出中断信号。

·错误状态:当PCIabort、PCIsystemerror、PCIparityerror、FIFOfull等错误出现时,状态机进入错误状态,同时发出中断信号。

1.4DMA操作流程

以非链式DMA的主模式写为例,主机首先写控制状态寄存器、中断屏蔽寄存器、字节寄存器、地址寄存器,而后状态机启动;当外部FIFO数据准备好,数据先传到数据通道RAM,再以DMA方式写到目标地址;判断DMA是否完成或出错,写中断状态寄存器,发出中断信号;主机收到中断后,读中断状态寄存器确定中断类型,如果发现DMA完成,则处理数据,如果发现DMA出错,则丢弃数据。

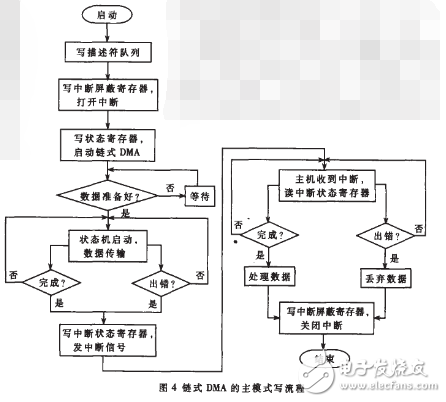

链式DMA可以认为是一组DMA的串连,其流程如图4所示。其中每一次DMA的数据包大小和目标地址可以不同,直到这一组DMA结束,发出一个中断信号。以主模式写为例,主机首先把多组字节寄存器和地址寄存器的值写入描

述符FIFO,每一组字节寄存器和地址寄存器就是一个描述符;主机再写中断屏蔽寄存器和控制状态寄存器即启动了DMA状态机,开始链式的数据传输。

与非链式DMA相比,链式DMA有更多的优点,以一次写入128个描述符的链式DMA为例:

·节省软件的开销。非链式DMA每启动一次传输,只能传一个数据包,而链式DMA一次写入128组描述符,就可以传128个数据包。非链式DMA一个数据包传输结束主机就响应一次中断,而链式DMA每128个数据包传输结束主机响应一次中断。链式DMA启动和响应频率降为原来的1/128,从而提高了传输速度。

·节省硬件资源。如果希望用非链式DMA可靠地传输一个大数据包,需要RAM的容量至少等于这个数据包的大小。例如非链式DMA一次传128×192字节的数据,则需要192K位的存储容量。而链式DMA可以把此数据包分成128次传输,仅使用1.5K位的存储容量,节省RAM资源。

·灵活的地址管理。链式DMA可以对每个数据包任意分配目标地址,那么一次操作可以读写一个从设备的多个地址空间,甚至多个从设备的多个地址空间。

2设计结果

用VHDL编写逻辑代码,用ModelSim仿真,图5是部分仿真波形:PCI的关键信号、DMA状态机、DMA寄存器。这是链式DMA启动写操作时的信号变化,数据包的大小是192字节,目标基地址是0x40000104。

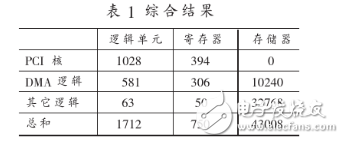

使用Altera公司的QuartusII对设计综合,选用器件CycloneEP1C6Q240C8,综合结果如表1所示。

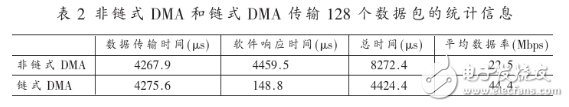

最高时钟频率可以达到86.57MHz。综合生成网表文件下载到FPGA,经过实际测试,系统运行正常。用逻辑分析仪测试PCI的关键信号,非链式DMA和链式DMA传输128个数据包的统计信息如表2所示。

链式DMA的平均数据率达到44.4Mbps,几乎是非链式DMA的2倍,这主要得益于软件响应时间的缩短。因此,对于非链式DMA,数据包越大数据率就越快;对于链式DMA,在数据包大小固定的前提下,数据包个数越多,相对响应时间会越少,数据率越快。

-

PCIe/PCI Master DMA、Nand Flash、DRAM、RocketIO/SRIO、SERDES、ADV2122012-05-21 0

-

PCI Express Endpoint Master DMA2014-08-23 0

-

PCI Express Endpoint Master DMA设计实现2015-06-21 0

-

DMA控制器介绍2015-11-04 0

-

请问ADSP-21364 Singly Chained Buffer单缓冲链式DMA怎么运作的?2018-09-29 0

-

基于FPGA的PCI Express总线接口应用2019-05-21 0

-

PCI Express的DMA子系统如何连接到DDR4控制器IP?2020-05-08 0

-

浅析DMA控制器与FSMC控制器2021-12-09 0

-

一文读懂DMA控制器2021-12-13 0

-

PCI总线从设备控制器的设计与实现2010-01-13 604

-

利用WinDriver实现链式DMA2013-05-15 1080

-

Crossbar的多通道DMA控制器设计2017-12-07 4651

-

dma控制器由什么组成2017-12-07 5181

-

dma控制器的组成2019-04-01 10115

-

dma控制器是什么_dma控制器工作方式2019-11-15 12555

全部0条评论

快来发表一下你的评论吧 !