NiosⅡ系统中DMA控制器的原理及应用

控制/MCU

描述

一、DMA控制器介绍

DMA控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。它之所以属于外设,是因为它是在处理器的编程控制下来 执行传输的。

传输结构与设置

目前有两类主要的DMA传输结构:寄存器模式和描述符模式。无论属于哪一类DMA,表1的几种信息都会在DMA控制器中出现。当DMA以寄存器模式工作时,DMA控制器只是简单地利用寄存器中所存储的参数值。在描述符模式中,DMA控制器在存储器中查找自己的配置参数。

(1)基于寄存器的DMA

在基于寄存器的DMA内部,处理器直接对DMA控制寄存器进行编程,来启动传输。基于寄存器的DMA提供了最佳的DMA控制器性能,因为寄存器并不需要不断地从存储器中的描述符上载入数据,而内核也不需要保持描述符。基于寄存器的DMA由两种子模式组成:自动缓冲(Autobuffer)模式和停止模式。在自动缓冲DMA中,当一个传输块传输完毕,控制寄存器就自动重新载入其最初的设定值,同一个DMA进程重新启动,开销为零。如果将一个自动缓冲DMA设定为从外设传输一定数量的字到 L1数据存储器的缓冲器上,则DMA控制器将会在最后一个字传输完成的时刻就迅速重新载入初始的参数。这构成了一个“循环缓冲器”,因为当一个量值被写入 到缓冲器的最后一个位置上时,下一个值将被写入到缓冲器的第一个位置上。

自动缓冲DMA特别适合于对性能敏感的、存在持续数据流的应用。DMA控制器可以在独立于处理器其他活动的情况下读入数据流,然后在每次传输结束时,向内核发出中断。

停止模式的工作方式与自动缓冲DMA类似,区别在于各寄存器在DMA结束后不会重新载入,因 此整个DMA传输只发生一次。停止模式对于基于某种事件的一次性传输来说十分有用。例如,非定期地将数据块从一个位置转移到另一个位置。当你需要对事件进 行同步时,这种模式也非常有用。例如,如果一个任务必须在下一次传输前完成的话,则停止模式可以确保各事件发生的先后顺序。此外,停止模式对于缓冲器的初 始化来说非常有用。

(2)描述符模型

基于描述符(descriptor)的DMA要求在存储器中存入一组参数,以 启动DMA的系列操作。该描述符所包含的参数与那些通常通过编程写入DMA控制寄存器组的所有参数相同。不过,描述符还可以容许多个DMA操作序列串在一 起。在基于描述符的DMA操作中,我们可以对一个DMA通道进行编程,在当前的操作序列完成后,自动设置并启动另一次DMA传输。基于描述符的方式为管理 系统中的DMA传输提供了最大的灵活性。

基本组成

(1)内存地址计数器:用于存放内存中要交换的数据的地址。在 DMA传送前,须通过程序将数据在内存中的起始位置(首地址)送到内存地址计数器。而当 DMA 传送时,每交换一次数据,将地址计数器加“1”,从而以增量方式给出内存中要交换的一批数据的地址。

(2)字计数器:用于记录传送数据块的长度(多少字数)。其内容也是在数据传送之前由程序预置,交换的字数通常以补码形式表示。在DMA传送时,每传送一个字,字计数器就加“1”。当计数器溢出即最高位产生进位时,表示这批数据传送完毕,于是引起DMA控制器向CPU发出中断信号。

(3)数据缓冲寄存器:用于暂存每次传送的数据(一个字)。当输入时,由设备(如磁盘)送往数据缓冲寄存器,再由缓冲寄存器通过数据总线送到内存。反之,输出时,由内存通过数据总线送到数据缓冲寄存器,然后再送到设备。

(4)DMA请求”标志:每当设备准备好一个数据字后给出一个控制信号,使“DMA

请求”标志置“1”。该标志置位后向“控制/状态”逻辑发出DMA请求,后者又向CPU发出总线使用权的请求(HOLD),CPU响应此请求后发回响应信号HLDA,“控制/状态”逻辑接收此信号后发出DMA响应信号,使“DMA 请求”标志复位,为交换下一个字做好准备。

(5)控制/状态”逻辑:由控制和时序电路以及状态标志等组成,用于修改内存地址计数器和字计数器,指定传送类型(输入或输出),并对“DMA请求”信号和CPU响应信号进行协调和同步。

(6)中断机构:当字计数器溢出时,意味着一组数据交换完毕,由溢出信号触发中断机构,向CPU提出中断报告。

二、NiosⅡ介绍

Nios Ⅱ嵌入式处理器是ALTERA公司推出的采用哈佛结构、具有32位指令集的第二代片上可编程的软核处理器, 其最大优势和特点是模块化的硬件结构, 以及由此带来的灵活性和可裁减性。

NiosⅡ特点

Nios II系列支持使用专用指令。专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个Nios II处理器创建多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和本身Nios II指令相同,能够从多达两个源寄存器取值,可选择将结果写回目标寄存器。同时,Nios II系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。 Nios II系列能够满足任何应用32位嵌入式微处理器的需要,客户可以将第一代Nios处理器设计移植到某种Nios II处理器上,Altera将长期支持现有FPGA系列上的第一代Nios处理器。另外,Altera提供了一键式移植选项,可以升级至Nios II系列。Nios II处理器也能够在HardCopy器件中实现,Altera还为基于Nios II处理器的系统提供ASIC的移植方式。

开发环境

Nios II处理器具有完善的软件开发套件,包括编译器、集成开发环境(IDE)、JTAG调试器、实时操作系统(RTOS)和TCP/IP协议栈。设计者能够用Altera Quartus II开发软件中的SOPC Builder系统开发工具很容易地创建专用的处理器系统,并能够根据系统的需求添加Nios II处理器核的数量。

使用Nios II软件开发工具能够为Nios II系统构建软件,即一键式自动生成适用于系统硬件的专用C/C++运行环境。Nios II集成开发环境(IDE)提供了许多软件模板,简化了项目设置。此外,Nios II开发套件包括两个第三方实时操作系统(RTOS)——MicroC/OS-II(Micrium),Nucleus Plus(ATI/Mentor)以及供网络应用使用的TCP/IP协议栈。

三、NiosⅡ系统中DMA控制器的原理及应用

1、dma控制器的原理

1.1dma功能介绍

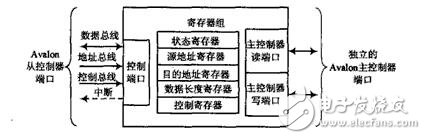

nios ⅱ中的dma控制器包含2个avalonmm类型的主控制器端口(读端口和写端口),1个用于dma控制avalonmm类型的从端口以及内部一些寄存器组所构成,其结构图如图1所示。

图1dma控制器的结构图dma控制器可以将数据从源地址搬移到目的地址。源地址或者目的地址可以是存储器中的一段地址范围也可以是avalon从控制器的外设。因此,在nios ⅱ系统中,存在3种类型的dma操作,即存储器到外设,外设到存储器以及存储器到存储器。dma控制器还具备流处理能力,允许固定或者可变长度的数据传输。当dma操作结束时,dma控制器发出中断(irq)请求。典型的dma数据传输过程如下:

(1) cpu通过写控制端口配置dma控制器用于数据传输;

(2) dma控制器向cpu发出hold信号请求占用总线;

(3) cpu响应dma控制器的请求,并让出总线,dma控制器获得总线的控制权;

(4) dma控制器读端口从源地址读数据,写端口向目的地址写数据,读写端口间利用fifo缓存数据;

(5) 当传输完指定的数据时,dma传输结束并向nios ⅱ cpu发出中断请求;

(6) cpu响应中断请求,dma交出总线控制权。

1.2dma寄存器组描述

dma控制器共有8个32位寄存器,其中5个为当前有效的寄存器,另外3个为以后扩展所用。寄存器的映射表如表1所示。 表1dma控制器内部寄存器映射表

偏移量寄存器名称功能0状态寄存器指示dma控制器内部 的详细情况1源地址寄存器读取数据的起始地址2目的地址寄存器写入数据的起始地址3数据长度寄存器从读端口传输到 写端口的字节数6控制寄存器设置dma的工作方式

状态寄存器的每个状态位指示dma控制器内部的详细情况。

位编号位名称描述0donedma传输完成。当检测到数据包结束信号或指定长度的数据传输完成时,done位为1。写0到状态寄存器使done位为0。1busy当dma传输正在进行时,busy位为12reop当传输完成事件由读数据包结束信号引起时,reop位为13weop当传输完成事件由写数据包结束信号引起时,weop位为14len当长度寄存器递减为0时,len位为1.

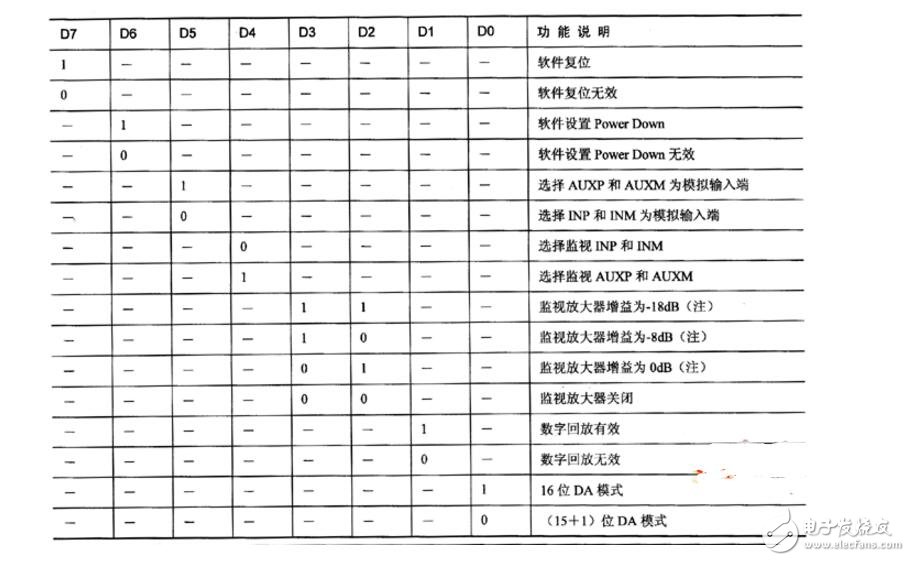

源地址寄存器指定dma传输的数据源的起始地址;目的地址寄存器指定了dma传输的目标数据区的起始地址;数据长度寄存器指定从读端口传输到写端口的字节数。如果是字传输,则数据长度寄存器的值需乘以4;若为半字传输,则需乘以2。主控制器写端口每写一个字节数据时,数据长度寄存器减1。当数据长度寄存器为0时,状态寄存器的len位置位;控制寄存器每个位设定dma的工作方式。控制寄存器每个位的意义如表3所示。dma传输的数据宽度用字节、半字、字、双字和4字位指定。这些位只能有一位设置为1。数据传输的宽度由2个读/写传输设备中传输宽度窄的一方决定。例如,将数据从16位的外部sdram存储器中搬移到内部32位的片内存储器时,传输数据宽度应该设置为半字。

表3控制寄存器位

位编号位名称描述0byte设置为字节(8位)方式传输1hw设置为半字(16位)方式传输2word设置为字(32位)方式传输3go使能dma传输。当设置为1且数据长度寄存器不为0时,开始dma传输4i_en使能中断(irq)。当i_en为1时,若状态寄存器的done位也为1,则dma控制器产生中断请求。5reen终止读数据传输。6ween终止写数据传输。7leen数据长度寄存器为0时传输结束。当leen位为1时,若数据长度寄存器达到0时,则结束dma传输。8rcon读地址固定。当rcon为0时,读地址在每次数据传输后增加;当rcon为1时,读地址在每次数据传输后不增加。9wcon写地址固定。当wcon为0时,写地址在每次数据传输后增加;当wcon为1时,写地址在每次数据传输后不增加。10doubleword设置为双字(64位)方式传输。11quadword设置为4字(128位)方式传输。

1.3软件编程

altera 提供了hal dma设备的驱动程序[45],该驱动程序把dma传输抽象成2种数据通道:发送数据通道和接收数据通道。当存储器从外设接收数据时,使用数据接收通道;当存储器向外设发送数据时,使用数据发送通道;当存储器间进行数据传输时,既要使用数据接收通道又要使用数据发送通道。与dma发送数据通道相关的函数有

alt_dma_txchan_open(),alt_dma_txchan_send(),

alt_dma_txchan_space(),alt_dma_txchan_ioctl(),

alt_dma_txchan_close();而与dma接收数据通道相关的函数

alt_dma_rxchan_open(),alt_dma_rxchan_prerare(),

alt_dma_rxchan_depth(),alt_dma_rxchan_ioctl()。

alt_dma_txchan_open()和alt_dma_rxchan_open()

函数分别打开dma控制器的发送数据通道和接收数据通道,获得dma控制器的发送数据通道和接收数据通道的句柄,返回非0值表示成功。

调用alt_dma_txchan_send()函数产生一次dma发送数据请求。其函数原型为int alt_dma_txchan_send(alt_dma_txchan dma,const void* from ,alt_u32 length, alt_ txchan_done* done ,void* handle)。调用此函数时,length字节长度的数据将从地址from处被发送。当发送结束时,函数返回值为非负则表示dma传输成功,否则表示传输失败。当传输结束时,回调函数done将被执行,handle为函数done的参数。

dma接收函数的用法与dma发送函数的用法大致相同,其函数原型为 int alt_dma_rxchan_prepare(alt_dma_rxchan dma,const void* data ,alt_u32 length, alt_ txchan_done* done ,void* handle)。参数data表示dma接收数据存放的起始地址。length表示接收数据的长度,单位为字节。函数返回值为非负表示接收成功。当接收结束时,回调函数done将被执行,handle为函数done的参数。另外,与发送通道和接收通道相关的还各有2个函数。与发送通道相关的函数为alt_dma_txchan_space()和alt_dma_txchan_ioctl()。alt_dma_txchan_space()返回传送到dma发送信道的发送请求数目。alt_dma_txchan_ioctl()则是执行了与器件相关的控制操作。与接收通道相关的函数为:

alt_dma_rxchan_depth()和alt_dma_rxchan_ioctl()。alt_dma_rxchan_depth()函数返回dma接收通道的最大接收请求数。alt_dma_rxchan_ioctl()执行了与器件相关的控制操作。

2、dma控制器应用举例

在软硬件的调试过程中,有时需要将内存中的一段数据通过串口打印出来,作为调试信息,这时就可利用dma技术进行数据传输。图2为在sopc builder中构建的dma传输的硬件连接图,实现了sdram到串口的数据传输。

图2硬件连接图如下的程序实现了将sdram中以chr为起始地址的20个字节的数据通过dma方式发送到串口。其实现的核心代码如下:

3、结语

在某雷达信号网络化数字传输系统的研制中,将雷达信号接口单元与网络接口单元分别映射为nios ⅱ系统中的2个外设,利用外设间的dma方式进行数据传输。实践证明,利用dma方式进行数据传输,cpu可从繁重的数据传输工作中释放出来,提高了cpu进行数据处理的能力。

- 相关推荐

- DMA控制器

-

NIOS II处理的数据如何返回到VGA控制器2015-05-19 0

-

DMA控制器在DSP数据采集系统中的应用2009-04-28 0

-

STM32 DMA控制器使用2015-01-13 0

-

DMA控制器介绍2015-11-04 0

-

浅析DMA控制器与FSMC控制器2021-12-09 0

-

一文读懂DMA控制器2021-12-13 0

-

一种以DMA控制器为基础的SoC系统设计2010-09-08 2302

-

Crossbar的多通道DMA控制器设计2017-12-07 4649

-

dma控制器芯片8257资料介绍2017-12-07 15914

-

dma控制器由什么组成?2017-12-07 3411

-

基于AXI总线的DMA控制器的设计2017-12-07 5923

-

dma控制器由什么组成2017-12-07 5180

-

dma控制器的组成2019-04-01 10110

-

dma控制器是什么_dma控制器工作方式2019-11-15 12550

-

ZYNQ开发案例之DMA控制器系统设计2020-12-05 3650

全部0条评论

快来发表一下你的评论吧 !