基于FAS466存储系统的DMA控制器设计

控制/MCU

描述

随着光电子信息技术的迅速发展 , 直接把光学信息转化为数字图像已经成为发展趋势 ,机载CCD相机是基于数字相机的基本原理 ,将图像以数字信息的形式存储、转移,并与地面实现通信。由于大面阵 CCD 机载相机的图像数据量非常巨大 而且图像输出速率也比较高 ,所以高速图像数据的实时记录是一个急需解决的问题。大面阵CCD 相机的数字视频存储的一般方案是基于高性能计算机体系结构,把 PCI总线的视频采集卡与高性能 IDE硬盘系统或基于 PCI SCSI桥的 SCSI存储硬盘系统结合起来完成任务。这种方案实现起来比较容 ,但存在总线瓶颈问题,一次存储占用两次PCI总线 ,而且还受到操作系统和文件系统的限制 ,所以在实际应用中存储速度很难突破 40MB /S。另外基于 PC I总线的存储方式基于计算机平台,占用体积比较大。针对这一问题,设计出脱离计算机平台基于 SCSI总线的图像数据存储方式,这种存储方式存储速度快,占用体积小,适合于机载相机。

1 CCD相机图像存储系统

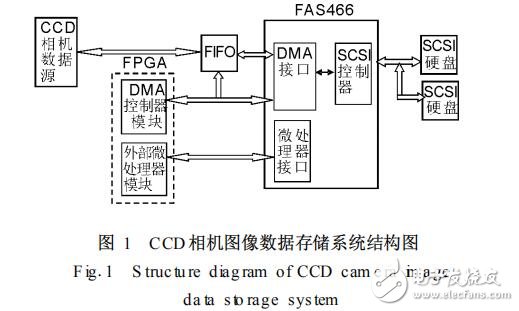

基于SCSI总线的CCD相机图像存储系统主要由数据源、DMA控制器、外部微处理器、FAS466协议处理器及 SC图如图1

存储系统各部分功能如下 :

(1) 外部微处理器

主要负责对各个模块进行协调和控制。完成与CCD相机图像数据的传输起始、结束控制 ; 对FAS466的初始化操作 , 对传输的异常情况进行中断处理 ; 在本系统中 , 采用 FPGA芯片实现外部微处理器功能。

(2) DMA控制器

控制 FIFO与 SCSI协议处理器内部缓冲器之间的数据传送 ,这样通过与协议处理器的 DMA接口相协调以控制数据源与 SCSI总线间的数据传送。本设计采用 FPGA器件实现 DMA 控制器 , 而不用专用的 DMA 控制器 ,主要考虑以下一些因素 :本设计的数据传输速率比较高,一般的专用 DMA控制器难以胜任 ; 专用的 DMA 控制器与 FAS466之间的连接需要大量的逻辑转换电路和外围连线、使设计难度加大。使用 FPGA 器件 ,除了完成DMA控制器的功能之外 , 还可以把电路中的译码、逻辑转换、系统复位等模块设计进去 , 减小了设备的体积 ,方便了以后对系统的升级和改进。

(3) SCSI协议处理器—FAS466

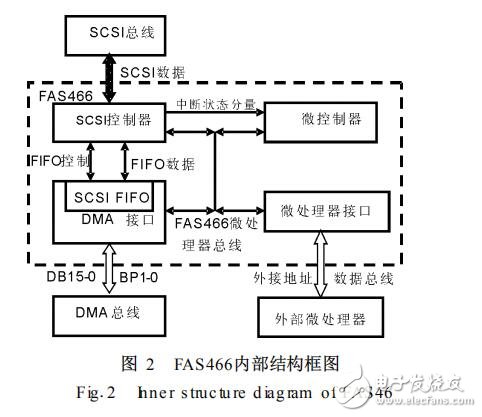

SCSI协议处理器是SCSI总线操作的执行部件。它可提供 Fast40的同步传输速率,它的同步数据宽总线传输速率可达 80MB /S。FAS466区别于其它 SCSI协议处理器的最大特点是它采用微处理器和 DMA接口结构 而常见的 SCSI协议控制器采用 PCI接口总线结构,这是本设计采用 FAS466的一个主要原因。采用微处理器和 DMA 接口结构 ,可以通过外部微处理器对传输进行控制 , 脱离微机平台 ,减少传输带宽限制,使数据存储系统具有非常好的灵活性和可移植性。FAS466 由 SCSI控制器、微控制器、DMA 接口和微处理器接口四个模块组成。图 2为 FAS466的内部结构。

2 DMA控制器设计

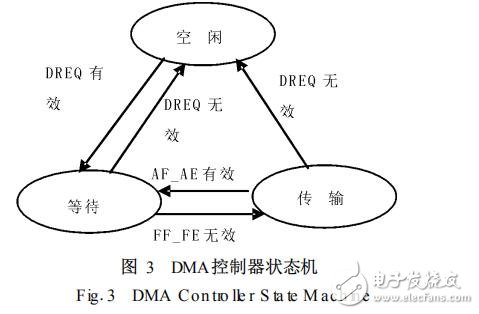

本系的软件计分为外部微处理对FAS466的初始化及 DMA 控制器的软件设计两部分 , 这两部分都通过对 FPGA芯片编程实现 , 本文将重点介绍一下 DMA控制器的软件设计。FAS466外部 DMA控制器利用 Verilog HDL语言对 FPGA 芯片编程实现。FAS466通过置 DREQ信号 有效请求数据传输 ;DMA控制器检测到DREQ有效并且外部 FIFO非空 ,则使 DACK有效并通知 FAS466开始 DMA传输。DMA控制器的状态机如图 3所示。

以下是实现DMA控制器的数据传输控制程序代码 :

always(posedge clock)

begin

if (RESET) begin

DMA state 《 = sIdle;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

else if (DMAEnabled)

begin

case (DMA state)

sIdle: begin

/ /如果 DREQ有效 , 则进入等待状态 ;

if (DREQ) begin

DACK 《 = 1;

DMA state 《 = #1 sDACKDelay;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

else begin

DACK 《 = 0;

DMA state 《 = #1 sIdle;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

end

sDACKDelay: begin

/ /如果 DREQ无效 , 则返回空闲状态 ;

if (

~

DREQ) begin

DACK 《 = 0;

DMA state 《 = #1 sIdle;

end

/ /如果 DREQ有效 , FF_ FE无效 , 则进入数据传

输状态 ;

else if (

~

FF_ FE) begin

DACK 《 = 1;

DMA state 《 = #1 sDataXfer;

RE 《 = 1; W E 《 = 0; DBOE 《 = 0;

end

else begin

DMA state 《 = #1 sDACKDelay;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

end

sDataXfer: begin

/ /如果 DREQ无效 , 则完成传输进入空闲状态 ;

if (

~

DREQ) begin

DACK 《 = 0;

DMA state 《 = #1 sIdle;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

/ /如果 DREQ有效 , AF_ AE有效 , 则进入等待状

态 ;

else if (AF_ AE) begin

DACK 《 = 1;

DMA state 《 = #1 sDACKDelay;

RE 《 = 1; W E 《 = 1; DBOE 《 = 1;

end

else begin

DMA state 《 = #1 sDataXfer;

RE 《 = 1; WE 《 = 0; DBOE 《 = 0;

end

end

default:

DMA state 《 = #1 sIdle;

endcase

end

end

上面程序经 ISE软件仿真,仿真波形如图4所示。

3 结论

本文介绍了高速、大面阵CCD相机存储系统的DMA控制器设计。运用Verilog HDL语言对 FP2GA编程实现 DMA 控制器功能。文中给出了它的软件程序及仿真波形。仿真结果表明为利用 FPGA芯片能够代替专门的DMA控制器完成DMA 控制功能。FPGA的运用使设计更加灵活 ,传输性能更好及反应时间更快 ,而且减小了存储设备的体积。

-

存储系统的层次结构2021-07-29 0

-

高速硬盘存储设备的系统结构设计2011-06-02 0

-

FAS368M的信号及内部寄存器说明2011-06-02 0

-

DMA控制器介绍2015-11-04 0

-

怎么实现基于FAS466的CCD相机数字视频实时存储系统设计?2021-06-07 0

-

浅析DMA控制器与FSMC控制器2021-12-09 0

-

符合Ultra2的高性能SCSI处理器FAS4662009-04-30 391

-

一种以DMA控制器为基础的SoC系统设计2010-09-08 2309

-

高速图像存储系统中SDRAM控制器的实现2016-08-29 603

-

NetApp_FAS2600系列混合存储系统2016-12-29 797

-

NiosⅡ系统中DMA控制器的原理及应用2017-12-07 2069

-

基于FAS466的CCD相机数字视频实时存储系统设计2019-02-14 319

-

SCSI控制器进入复位状态时的注意事项2020-08-10 1271

-

基于SCSI协议控制器FAS466实现专用高速SAR数据存储设备的设计2020-11-12 2877

-

基于SCSI协议处理器FAS466实现图像数据存储系统的设计2021-03-16 2118

全部0条评论

快来发表一下你的评论吧 !