基于FPGA实现PCI-E接口和DMA控制器设计

控制/MCU

描述

随着网络的飞速发展,人们可获取的信息量日益增长,数据的处理及存储速率的要求也越来越高。万兆网(10Gb以太网)的普及,高速存储设备的应用(如DDR2,传输速率可达800M)对系统带宽带来极大的挑战。

伴随着FPGA技术的大规模的应用,越来越多的大型系统采用PCI Express总线连接FPGA处理板和PC以实现数据的交互。尽管很多FPGA公司推出了基于PCI Express协议相关的IP硬核,但是掌握这些硬核的使用需要对PCI Express 协议具有一定的了解,而且直接使用硬核,带宽很小,开发难度大,移植性差等缺点这些都是造成目前PCI Express接口设计的瓶颈。为了降低开发难度,提高带宽和移植性,许多现有的方案是在PCI Express硬核中加入高速DMA控制器单元,以此来达到设计需求。

文中介绍了一种基于高速的I/O串行互联技术,PCI-Express(简称PCIe),提出了在系统设计中基于FPGA的PCIe总线接口设计及应用于该总线的高速DMAEngine设计方案。

PCI Express总线简介

PCI Express总线技术是取代PCI的第三代I/O技术。PCIExpress总线是为计算机和通讯平台定义的一种高性能、通用I/O互联总线。至今已经发布了3个正式版本:PCI Express 1.0、PCIExpress 2.0、PCI Express 3.0。单向单通道带宽分别为:250MB/s, 500MB/s, 1GB/s。PCI Express体系结构的设计非常先进,采用了类似网络体系结构中OSI分层体系结构设计方案,如图2.1所示。按照协议规范,PCI Express总线的层次结构分为物理层(Physical Layer)、数据链路层(Data Link Layer)和事物层(Transaction Layer)体系结构。

在性能方面,相比PCI总线,PCI Express总线具有以下特点:

(1)在数据传输模式上,PCI Express 采用差分串行传输方式,一条PCI Express通道(称为PCI Express X1)由2对差分信号线来实现数据的发送和接收。

(2)PCI Express具有高速串行通信接口所特有的时钟恢复核心,将时钟融合到传输的数据中,这样既减去了时钟管脚,又能大大提高传输速度,突破了并行传输带宽的瓶颈。

(3)PCI Express是采用点到点的互连方法,每个设备都由独立的链路连接,独享带宽,大大提高传输效率。

(4)具有很好的灵活性,一个PCI Express物理连接可以根据实际需要配置成X1,X2,X4,X8,X16 及X32链路模式。因此传输的速度也就相应的成倍增长。

(5)PCI Express传输的数据以协议定义的数据包(packet)的形式进行传输,保障了数据传输的完整性和可靠性。

(6)PCI Express协议加入了数据重传机制,提高了数据传输的可靠性。

正是由于PCI Express的这些技术特点,使得其越来越广泛的应用在计算机系统架构及海量数据传输接口领域,特别是在加入了高速DMA控制器传输方式下,PCI Express带宽及传输效率大大提高,因此在高速系统领域具有广阔的前景。

FPGA系统设计方案

传统FPGA设计方案

传统FPGA并不具备LVDS信号驱动能力。一般以PEX8311桥接芯片实现PCIe物理层接口,再配合CPLD实现用户逻辑设计。PEX8311提供2个端口,一个为兼容PCIExpress1.0标准的PCIe接口,另一个为LocalBus总线接口,用于与CPLD相连。LocalBus总线工作于66MHz时钟,32-bit总线宽度,可以提供266MB/s带宽。同时,PEX8311还提供了2组DMA通道。使用PEX8311可以方便地从PCI平滑过渡到PCIe,从而降低开发成本,因此被广泛使用。

然而,PEX8311并不能有效发挥出PCIe高带宽优势,也缺乏可配置性和灵活性,难以提高系统整体性能。

基于PCIe硬核接口设计

Xilinx新推出Virtex-6系列的FPGA,集成了PCIeIP硬核模块。该模块兼容PCIExpress2.0标准分层协议(为物理层、数据链路层和事物层,又称传输层),提供了系统接口(SYS)、外部传输接口(PCIEXP)、配置接口(CFG)、事物接口(TRN)和物理链路接口(PL)。其Virtex-6GTX可配置高速串行传输器为PCIe信号可靠传输提供了保障。文中便是针对该硬核的事物层提出片上系统的PCIe设计方案。

PCI-Express接口及应用层设计

一个基本的高速数据采集系统,由微处理器(CPU)、FPGA和外部存储器等组成。CPU与FPGA通过PCIe总线进行数据传输,FPGA通过DMA方式对外部存储器进行数据读写操作。文中给出基于PCIex1传输方式的接口设计方案。

PCIe接口及事物层设计

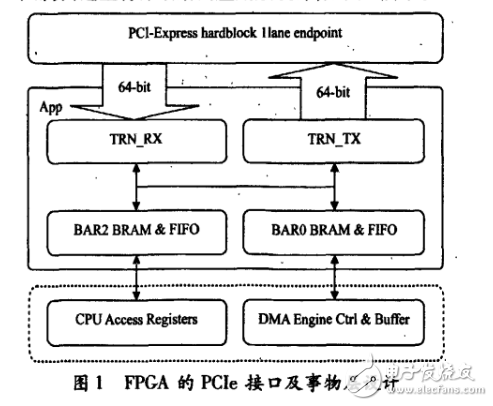

较之使用PEX8311桥接芯片的系统设计,采用基于Xilinx的IP核的设计方案,用户可以根据自己的需求灵活设计面向事物层接口电路,并方便加入特殊功能,如与内部总线连接、实现DMA传输等。该设计充分利用FPGA集成度高、可配置性强等特点来发挥PCIe接口性能。FPGA的PCIe接口设计包括XilinxPCIe端点硬核和面向事物层的应用逻辑设计2个部分,这里将详细给出应用层设计,如图1所示。

XilinxPCIe硬核支持64-bit数据通路,分别用于发送和接收数据。该硬核提供6个32-bit基地址寄存器BAR0~BAR5(BassAddressRegister,简称BAR),可以根据用户设计需求进行配置。在本设计中使用BAR0和BAR1组成一组64-bit地址空间,用于存储外部CPU访问FPGA内部寄存器地址。使用BAR2和BAR3组成另一组64-bit地址空间,用于存储DMAEngine控制器和缓存器地址。通过判断trn_rbar_hit_n[6:0]来区分BAR0和BAR2,其主要代码如下:

⋯ ⋯

‘TRN _RX_M EM _RD64_DW 1DW 2: begin

⋯ ⋯

req_bar0_o 《 = ~trn_rbar_hit_n_q [ 0 ] ; req_bar2_o 《 = ~trn_rbar_hit_n_q [ 2 ] ;

⋯ ⋯

end

以外部CPU读FPGA内部寄存器为例,FPGA将收到的PCIe总线上数据帧经由硬核的事物层,以64-bit带宽送出,应用层通过TRN_RX接收状态机来判断请求访问的地址空间,然后将请求数据缓写入一个双端口的req_fifo;用户逻辑通过读取req_fifo,将有效的寄存器数据写入另一个双端口data_fifo中,最后通过TRN_TX发送状态机发送给硬核事物层。

基于PCIe的DMAEngine设计

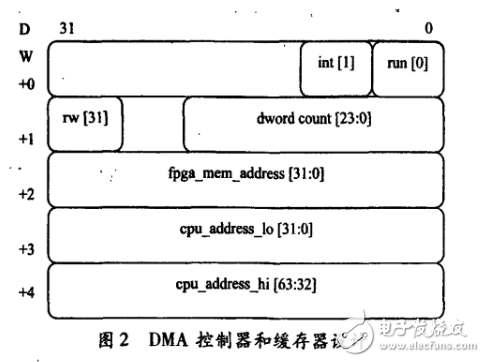

通过DMA访问外部存储器的最大优势在于CPU在配置完DMAEngine后可以继续其他指令操作,DMAEngine会通过请求PCIe总线中断的方式,来完成数据传输。本设计将PCIeBAR0地址空间存储DMAEngine控制和缓存器地址,其定义如图2所示。

DWORD0[0],run,写1开启DMA;

DWORD0[1],int,写1开启DMA中断方式;

DWORD1[31]rw,写1读fpga外部存储器;

DWORD1[23:0]dwordcount,DMA操作数据个数,以dword为单位;

DWORD2[31:0]fpga_mem_address,fpga外部存储器地址;

DWORD3[31:0]cpu_address_lo,cpu低32位地址;

DWORD4[31:0]cpu_address_h,icpu高32位地址。

修改PCIe数据帧类型(tlp_type《=trn_rd[62:56]),加入DMA数据帧,使其有别于对BAR的读写操作,部分代码如下:

`efineTRN_RX_DMA_TLP_TYPE 7.b10_01010;/*DMA

数据类型*/

d`efineTRN_RX_DMA_DATA1 10.b01_0000_0000;/*

DMA操作状态*/

,,

case(state)

R`ST:begin

,,

case(tlp_type)

,,

T`RN_RX_DMA_TLP_TYPE:begin

,,

state《=T`RN_RX_DMA_DATA1;

end

,,

T`RN_RX_DMA_DATA1:begin ,,

end,,

endcase

以同样的方式在TRN_TX状态机中加入DMA请求,其代码如下:

d`efineTRN_TX_DMA_REQ 10.b01_0000_0000;

,,

case(state)

R`ST:begin

if(dma_tlp_ready)begin/*DMAEngine准备好读操

作数据帧*/

state《=T`RN_TX_DMA_REQ;

dma_tlp_rd_en《=1.b1; /*DMA缓存读使能

*/

end

elseif(,,)

,,

end

,,

T`RN_TX_DMA_REQ:begin

,,

if(~tlp_dma_data_eof)/*

数据帧结束标志位*/

state《=T`RN_TX_DONE;

els

state《=T`RN_TX_DMA_REQ;

end

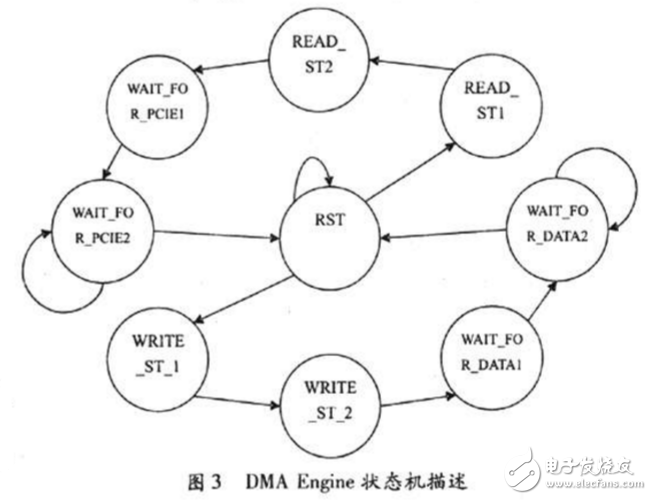

FPGA的DMAEngine状态转移图如图3所示,分DMA读操作和写操作2部分。DMAEngine处于RST状态时,通过读取DMA信息标识符来判断当前是否处于空闲状态,并从FPGA内部RAM中读取DMA控制信息(读或写),并进入相应状态READ_ST或WRITE_ST。以CPU写FPGA外部存储器为例,CPU通过PCIe总线写BAR0地址数据来配置并开启DMAEngine。FPGA将发出对CPU的DMA读请求,然后等待CPU发送DMA数据。此时DMAEngine处于WAIT_FOR_DATA状态,等待来自PCIe接口的DMA数据包。同样,CPU读FPGA外部存储器时,FPGA将发出对CPU的DMA写请求,并当DMA完成读操作后,等待PCIe接口发送DMA数据包,并由中断标志位判断是否开启PCIe中断。

仿真及测试结果

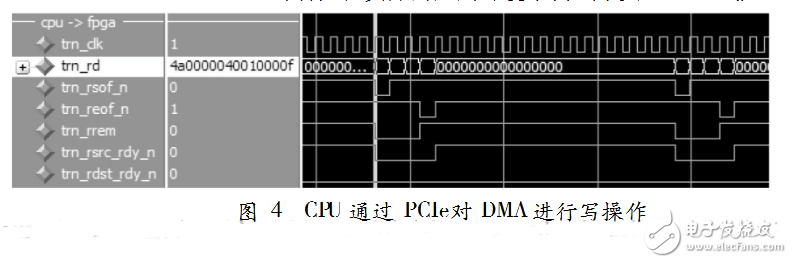

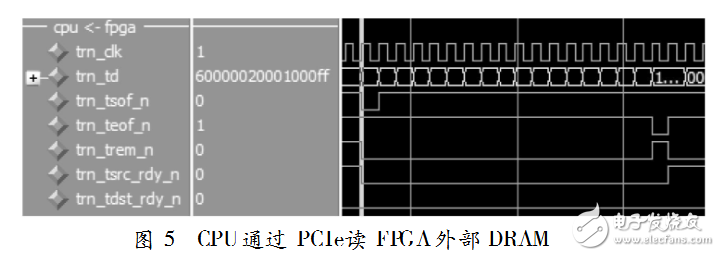

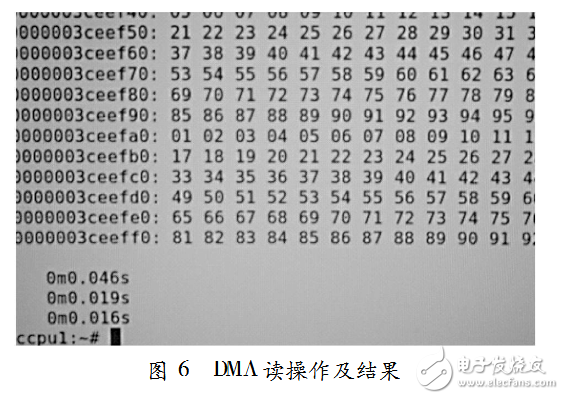

为了测试该DMAEngine设计,对FPGA外部64-bitDDR2DRAM进行32个dwords(128bytes)读与写操作,得到的仿真波形如图4和图5所示。图4是对DMA进行写操作的PCIe事物层接口波形。图5是对DMA进行读操作的PCIe事物层接口波形。该设计方案在questasmi6.3f下验证通过。可以估算出一次PCIex1写操作为1720Mb/s,读为1684Mb/s。同样,在实际的应用环境中测试本文DMAEngine设计,也获得比较好的结果。图6就是系统以本文DMA方式进行4096bytes读外部存储器的结果。

FPGA较ASIC的强大之处,在于灵活性和可配置性。文中凭借XilinxPCIe硬核,很好地实现了PCIex1总线接口,并在此基础上加入高速DMAEngine设计,可以有效地提高系统数据存储效率。

该设计方案通过简单修改也同样适用于32-bit带宽传输系统设计。

-

PCI-E 的PADS封转2011-03-30 0

-

PCI Express Endpoint Master DMA设计实现2015-06-21 0

-

在FPGA上设计PCI-e Gen2.0和PCI-e Gen3.0有什么不同2016-03-03 0

-

270-VC709E 增强版 基于FMC接口的Xilinx Vertex-7 FPGA V7 XC7VX690T PCIeX8 接口卡2016-03-11 0

-

pci-e布线规范2016-07-14 0

-

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡2017-10-19 0

-

RapidIO与PCI-E哪个更适合通信2019-01-29 0

-

Kintex®-7 PCI Express开发板需要什么样的PCI-e驱动器?2019-09-25 0

-

PCI PCI-X PCI-E介绍 精选资料分享2021-07-29 0

-

什么是PCI PCI-X PCI-E?2021-10-25 0

-

请问ickey的测试板卡中有哪一个带有mini pci-e接口?2023-11-01 0

-

PCI-E接口定义 引脚定义图 PCI-E针脚定义图2008-04-27 74581

-

基于FPGA的PCI接口控制器的设计与实现2009-12-14 1741

-

基于PCI Core的链式DMA控制器设计2017-12-06 2841

-

M.2和PCI-E接口固态硬盘的区别是什么2020-07-28 8286

全部0条评论

快来发表一下你的评论吧 !