三输出和双输出微型模块稳压器对基于FPGA的系统优化方案

FPGA/ASIC技术

描述

尽管 FPGA 的通用和可配置特性对系统设计师来说很有吸引力,但是影响这些器件内部运行方式及其外部接口协议的设计规则非常复杂,需要大量的培训、参考设计评估、设计仿真和验证。因此,FPGA 供应商提供详细的硬件和固件支持,以帮助系统设计师设法应对数字领域的新挑战。不过,模拟领域错综复杂,难以理解,尤其在用 DC/DC 稳压器为内核、I/O、存储器、时钟和其它轨供电和提供稳定电压这一块,需要新的解决方案。例如,今天的 FPGA 及支持组件需要多个电压轨。为了高效率和以最小的空间为每个轨供电,要求一个 DC/DC 稳压器电路平均含有 10 个组件 (电感器、MOSFET、电容器、DC/DC 稳压器等)。仅为一个 6 轨 FPGA 供电,也许就需要多达 60 个组件。除了用料单中列出用于 FPGA 供电的一长串组件以外,还有与组件插入、可靠性、PCB 复杂性以及更多因素有关的隐藏成本。现在,是 DC/DC 制造商提高产品性能标准的时候了。

管理多个电压轨

较旧的几代 FPGA 需要两或 3 个电源轨。现在,一些高端多核器件需要多达 7 个轨,既有 3.3V 传统电源轨,也有最近出现的从 2.8V 直到 1.0V 及更低电压的较低电压轨。此外,还为存储器、网络处理器、图形处理器、数模或模数转换器、以及运算放大器和 RF IC 等非 FPGA 器件提供了其它一些电压轨。

确保具有多个电压轨的系统“干净”地启动,而轨之间相互没有任何冲突,这是配备排序和跟踪功能的 DC/DC 稳压器的关键任务。简单地说,每个稳压器必须能够跟踪其它稳压器的输出电压。好消息是,从几年前开始,FPGA 就不需要对其多个轨进行任何排序了。不过,系统内跨不同部分的几个电压的顺序斜坡上升或斜坡下降仍然是需要的,以防止电压轨变化太快或太慢时可能发生的锁断。

过去,电源轨的跟踪和排序任务由单独的电源管理 IC 完成。今天,设计师要求排序和跟踪功能嵌入到稳压器中,尤其是当稳压器必须位于系统的不同角落时,更是这样。

降低电压纹波噪声和电容器要求

在非便携式应用中,随着对压降和电流要求的提高,在选择 DC/DC 稳压器时,散热和运行效率也变成了更加重要的因素。在便携式应用中,尽管每个轨的负载电流较低,但是在节省电池能量和简化便携式产品的热量管理方面,运行和备用效率仍然是重要因素。

无论是在便携式还是非便携式应用中,尤其是对于大功率需求来说,与线性稳压器相比,开关模式 DC/DC 稳压器可提供较高性能的解决方案。例如,一个开关稳压器从 3.3V 输入电源、以 90% 的效率提供 1.2V/5A,相比之下线性稳压器效率为 36%;此外,开关模式稳压器消耗 0.7W 功率,而线性稳压器消耗 10.5W。

另一方面,由于其固有的开关运行模式,开关模式稳压器引入开关噪声和更高的输出纹波噪声 (输出电压峰值至峰值纹波)。不幸的是,新型 FPGA 的较低电压轨和更快的 I/O 信号较精准的眼图对电源“噪声”的承受能力较低。为了减轻纹波噪声,可以给电路增加更多的输入和输出电容器,以降低峰值至峰值纹波电压。不过,降低开关噪声更具有挑战性。一种可能的方法是,让 DC/DC 稳压器的运行频率与一个外部时钟同步,该外部时钟迫使稳压器在一个设定的频率范围内运行,这些频率的选择原则是:对系统中其它噪声敏感器件的干扰最小。当几个开关模式稳压器都同步至一个对系统其余部分很安全的时钟频率时,这种方法尤其有效。

这些方法有助于设计较低噪声的开关模式负载点稳压器,不过,如果 DC/DC 稳压器是从零开始以合适的架构、功能和布局设计的,那么噪声问题可以极大地减轻。这样的稳压器最大限度地减轻了对电容器、滤波和 EMI (电磁干扰) 屏蔽的依赖。

降低高度以实现更好的空气流动

人们迫切需要缩小基于 FPGA 的系统的尺寸,同时要增加功能、存储器存储容量或计算功率,这促使设计师改进用来冷却组件的方法。一种简单的方法是,在组件上方提供高效率的空气流动。高的组件遮挡了 FPGA 或存储器 IC 等较纤巧封装上方的空气流动。在预制 DC/DC 负载点稳压器的情况下,遮挡非常严重,因为这些器件的高度达到了 FPGA 和其它 IC 高度的 6 至 10 倍。

在从封装顶部高效率散出内部产生的热量方面,FPGA 的纤巧 BGA 封装极其有用。当预制 DC/DC 稳压器等较高的器件阻碍空气流动并在其附近的组件上投下“阴影”时,这种好处就减小了。

少用 50% 的组件:三输出和双输出微型模块稳压器

一个新款和具有多个输出和输入的 DC/DC 微型模块 (uModule®) 稳压器系统级产品系列被设计为不仅可减少组件数量,而且可降低与组件插入 PCB 有关的成本、消除布局错误并提供一个已经做好的完整解决方案,从而减轻了任何数字系统设计师的工作负担。

就 FPGA 和基于 FPGA 的系统所使用的 DC/DC 稳压器电路而言,与分立式解决方案相比,除了材料成本降低 50%,所占用的 PCB 面积也减小了 10%,这个系列的多个输出 DC/DC 微型模块稳压器都有以下优势:

1. 电流模式架构可以非常精确地逐个脉冲提供输出负载电流

2. 对输出进行均流的功能提高了单个微型模块稳压器的输出功率

3. 微型模块至微型模块器件的输出均流功能进一步提高了输出功率

4. 分享输入功率:例如,双通道 8A LTM®4616 可以同时由 3.3V 和 5V 轨供电,以在如果一个输入电源无法提供充足的功率时,可同时分享两个单独输入电源的功率 (参见数据表以获得详细信息)

另外,这个系列的双通道和三输出 DC/DC 微型模块稳压器解决了之前提到的一些问题:

1. 管理多个 FPGA 或系统轨

这些 DC/DC 微型模块器件具有跟踪和/或排序功能,以正确启动具电源排序限制的系统或使其停机。

2. 降低电压纹波噪声和对电容器的要求

每个微型模块器件都含有内部输出和输入旁路电容器。此外,每个器件用非常低ESR的输出电容器都可以稳定,因此用户可以选择输出电容器的类型和值,以优化输出纹波 (有时称为“噪声”)。

3. 降低器件高度以使空气更好地流通

这个系列的双通道和三输出微型模块稳压器高度仅为 2.8mm,允许空气顺利流动,可以更好地去除稳压器及其附近组件的热量。这个系列的成员之一是 LTM4615,该器件是一个完整的三输出 DC/DC 微型模块稳压器系统,含有两个 4A 开关模式稳压器和一个 1.5A 的非常低压差 (VLDO) 稳压器,采用纤巧 15mm x 15mm x 2.8mm 表面贴装封装。两个开关稳压器中每一个的稳定输出电压都可在 0.8V 至 5V 的范围内调节,第三个输出可在 0.4V 至 2.6V 的范围内调节,这适合为新一代较低电压、多轨、尺寸非常小的数字 IC 供电。另一个产品是 LTM4619,该器件可用高达 26.5V 的输入电源工作。表 1 列出了这个双通道和三通道微型模块稳压器系列的所有成员。

图 1:三输出 LTM4615 是一个完整的封装系统,其两个 4A 和一个 1.5A 输出为稳压器的三个电压而优化,采用 5V 或 3.3V 输入轨

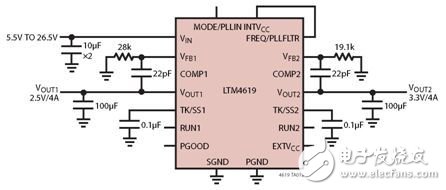

图 2:双输出 LTM4619 从高达 26.5V 的输入电源提供 4A 电流 (15mm x 15mm x 2.8mm LGA)

表 1:三通道和双通道 DC/DC 微型模块稳压器

结论

凌力尔特公司在 DC/DC 稳压器架构和封装领域的创新已经使得新一代负载点解决方案能够满足基于 FPGA 的系统提出的更严格的要求。这个微型模块 DC/DC 稳压器系列 (表 1) 由多输出产品组成,这些产品具有各种功率级和功能 (参见 )。这些器件的可靠性还为多芯片封装领域创立了新的标准,凌力尔特公司严格的合格性验证以及严格的测试保证了这些器件的可靠性。微型模块 DC/DC 解决方案正为新一代 FPGA 和基于 FPGA 的系统在较小的工艺尺寸上提升其性能铺平了道路。

-

凌力尔特推出双输出 18A 或单输出 36A DC/DC 微型模块降压型稳压器2013-09-18 1278

-

凌力尔特推出单输出 50A 或双输出 25A µModule 稳压器2016-03-01 956

-

µModule(微型模块)稳压器实现电源解决方案2017-09-19 495

-

Linear微型模块稳压器新增成员LTM46242018-09-27 0

-

DCDC微型模块稳压器LTM8025资料推荐2021-03-29 0

-

微型模块稳压器LTM8027相关资料分享2021-03-31 0

-

DCDC微型模块稳压器LTM4612相关资料下载2021-04-01 0

-

DCDC微型模块稳压电路LTM4628相关资料下载2021-04-14 0

-

凌力尔特推出4A系统级封装DC/DC微型模块稳压器2009-12-03 683

-

凌力尔特推出DC/DC微型模块(μModule)稳压器LTM2010-12-03 904

-

凌力尔特推出降压型微型模块稳压器LTM46132011-05-19 1361

-

凌力尔特推出降压型微型模块稳压器LTM46412012-10-18 1128

-

Linear新推微型模块稳压器LTM46442014-01-16 7185

-

6 输出 DC/DC 微型模块稳压器2021-03-19 473

-

单输出36A输出开关模式降压型DC/DC μModule®稳压器介绍2023-02-28 733

全部0条评论

快来发表一下你的评论吧 !