微波电路的微波性能影响的要素研究分析

RF/无线

描述

微波电路通常频率较高(1GHz以上),是微波集成电路器件通过微带传输线构成的一个平面电路、整个无论其图形如何复杂,均可简便地用厚、薄工艺制作在介质片上,将基片固定于作为接地板的金属基座(载体)上就构成一个完整的电路。这种电路的制作成本比同功能的波导和同轴电路便宜得多。这种电路由于消除了许多接头,同时带来了制作重复性好、性能优良、调整方便、体积小、重量轻、可靠性高等优点,得到了广泛地应用。

微波电路制作一般可分三个阶段。微波器件制作→基板微带线制作并组成功能块→与金属基座连接组成微波电路。微波电路由于作用频率高,其接地要求特别高、接地包括功能块基片接地与功能块与金属基座的接地连接。特别是后者,惯用螺钉连接,由于连接间的空隙,导致功能块间的串扰(一般≥0.5dB),插入损耗增加(一般≥1.4dB),同时也带来了附加电容与振荡。L波段以上电路已无法获得稳定的电路参数,可靠性低。目前国外已普遍使用钎接方法来实行“大面积钎接”。国内也开始摸索和使用。大面积钎接的主要难点在于金属与陶瓷材料的物理、化学性能差异太大,易造成陶瓷开裂、不良接头、变形等。芯片与微带线互连的长度、拱度,微带线制作的精度等同样是影响微波性能的要素。本文主要介绍笔者与同仁们在这方面的研究成果。

1 接地连接的分析和设计

微波电路的接地连接主要影响电路串扰和插入损耗。电路串扰主要是过长的连接线形成附加电感引起的。插入损耗主要由四分部组成:导体损耗、介质损耗、辐射损耗及制作工艺的损耗。

导体损耗指金属导带与接地金属面对传输信号

所造成的插入损耗。介质损耗指电磁场在金属导带和接地面中间的介质中传输,由填充介质引入的插入损耗。焊接缺陷(空洞、孔隙)及其它制作缺陷(介质板、导带¨)均会增加插入损耗[1]。接地连接的设计原则就是就近接地,大面积(全面积)接地。几种典型的接地方式是:

(1)接地金属化通孔:主要连接微带线与基板接地面。可通过孔金属化、空心铆钉、连接销钉的方法实现。如图1所示。

接地通孔设计

空心铆钉

连接销钉

图1 几种典型的接地方式

(a)薄膜接地孔—四周金属化

(b)厚膜接地孔—全孔金属化

(c)多层厚膜,大面积接地,

采用网状孔,孔金属化。

三种方法各有各的技术难点,特别是薄膜金属化孔,目前尚处研究阶段,一次成功率仅为90%。采用空心铆钉的方法最可靠,但空心铆钉的制作难度较大。

(2)接地包边:为了更大面积的与接地面连接,在条件允许的情况下,可采用直接用铜箔(厚0.10~0.20mm)连接面。如图2所示。

图2 包边接地示意图

包边接地比较可靠,但只有在孔径及边带尺寸大的地方进行,而焊接工作也往往只能靠人工进行,要求操作工人的熟练程度高。

(3)接地面与接地板的大面积焊接:用于替代螺钉连接的大面积焊接,是保证接地可靠的主要手段。

微波电路中的传输线(微带线)通常在坚固的介质基片(陶瓷、石英……)上用薄膜工艺(蒸发、溅射……)来制作。随着新技术的发展,微波电路微带线也有用厚膜、LTCC(低温共烧陶瓷)技术制作,近年来也出现非Al2O3的软基片复合材料作基片的,但在S波段以上,往往还无法替代陶瓷材料。

陶瓷材料与接地板金属的连接,即接地面与接地板的连接。惯用螺钉连接,除去装配和使用过程中容易造成陶瓷基片碎裂外,它已无法满足微波电路的电、热性能参数的要求,近年来已被软钎接技术所替代。

由于陶瓷与金属的化学、物理焊接性差异极大,特别热膨胀系数的差异,造成焊接及使用过程中瓷片开裂、电路失效。这些问题的研究,将在2、3节中叙述。

2 焊接性能研究

陶瓷基片与金属基座焊接时,考虑到陶瓷金属化(薄、厚膜工艺) 及MIC器件的特性,往往采用软钎接办法来实现。陶瓷基片接地面与载体必须具备优良的软钎接性能。

(1)基片接地面的金属化研究

微波电路基片金属化的主要途径是通过薄膜、厚膜和LCTT共烧来实现。

(a)薄膜制作

微波薄膜电路一般采用CrAu膜系统。Cr层作为过渡层以提高金属与陶瓷板的附着强度,Au作为主导层以满足微波电性能的要求。

采用Au基钎料可以实现CrAu膜与载体的焊接,但Au基钎料价格昂贵,并要在专门的气控炉中进行,工艺复杂,为此需研究适合普通Sn-Pb钎料的金属膜系。

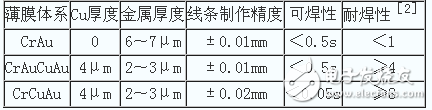

研究设计了CrAu、CrCuAu、CrAuCuAu三种膜系,并通过不同工艺手段制作出不同的膜厚。测试结果见表1。

表1 不同薄膜体系的工艺性能状况

考虑微波电路的综合要求(线厚、精度及焊接性等)选用 CrAuCuAu系统作为微波电路的导带及接地面金属化膜。

(b)厚膜制作

微波电路厚膜制作的关键是线条精度,接地面的金属层一般是Au基合金,其中以Au-Pt的耐焊性最好。Au-Pt的耐焊性大于10次,如烧结工艺掌握好的话可达70~80次。Au-Pt膜的可焊性相对来说差一些,但经过适当处理,也能获得较好的可焊性。

(c)LTCC共烧制作

各层之间的通孔、接地面均可用Au制作,整个基板的制作与厚膜制作相同,也以采用Au-Pt膜为主。

(2)载体可焊性镀层研究

根据产品不同的要求,需选用不同的载体材料,功率大、散热要求高的选AI、Cu;重量要求轻的选Al、Ti;与Al2O3陶瓷热膨胀系数相近的选可伐合金、42合金等。另外还有与GaAs热膨胀系数相近的Mo,新兴的复合材料AlSiC等,这些载体材料要通过表面处理才能与陶瓷基片焊接,得到优良的焊接接头。表面处理包括焊接性能良好的表面镀层和热膨胀系数分配合理的镀层体系。

本研究设计了不同的镀层系列。经环境试验及试样制作,最终选用的体系分别为:

Al——NiP-Cu-SnPb

Cu——Ag

Ti——Cu-SnPb

可伐——Ni-Au

42合金——Ni-Au

3 焊接工艺研究

焊接工艺研究主要包括三方面的内容:热膨胀系数相异造成的陶瓷开裂;焊接变形和钎透率(被钎接面积/需焊接面积)。

(1)陶瓷开裂问题

从结构分析、设计;钎料和缓冲层;钎接工艺等几个方面着手研究。

结构分析与设计—通过结构分析和计算,得出了最佳的结构因素。为计算简便起见,作如下假设:a)不考虑Y、Z方面的变化;b)温度范围设定为 20~200℃,仅考虑弹性变形;c)中心轴的长度保持不变如图3、图4、图5所示。

图3 试样示意图

图4 板厚比与po的关系

图5 界面应力分布

综合考虑,选择r≤1为佳。

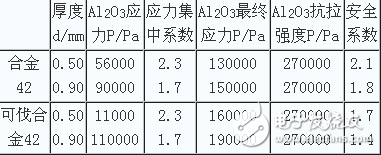

WilliamW在42合金和可伐合金上用Au-Ge焊料在400℃时焊接Al2O3,并对应力作了测定结果。见表2。

表2 应力测定结果

从表2中也可看出金属基座愈薄,对抗裂愈有利。

钎料和缓冲层—选择焊接温度低,塑性好的钎料及应力缓冲层是防止陶瓷开裂的一个重要手段。研究了多种钎料的可焊性,最终选定In-Sn、Sn-Pb二种钎料作为基本钎料。[4][6]缓冲层的结构也很多,材料选择主要是以Mo片、Ti片为主。

钎接工艺—钎接工艺主要根据陶瓷热性能来设计,选用缓慢加热、冷却过程如图6所示。值得提出的是这种工艺对基片与载体的焊接性能,特别是耐焊性提出了更高的要求。

图6 典型温度曲线(Sn-Pb钎料)

(2)焊接变形

焊接变形主要影响最终装配质量,变形大时,在最终装配时不会引起开裂。变形必须控制在一定的范围内。

控制变形的方法是载体材料、厚度的正确选择和焊接夹具的设计。

选用夹具,控制变形,将增加应力,不利于防裂,为此夹具的压力必须合适。压力是保证间隙、焊接质量和减少焊后变形的关键因素,要在整个加热过程中维护适当的压力,是夹具设计的原则。

通常设计要求为变形小于0.1mm/100mm,正确设计夹具及焊接工艺,研究的实测变形一般在0.03~0.05mm之间。

(3)钎透率

钎透率直接反映了接地效果,是整个技术的重要指标,要在100mm×100mm(研究目标)内达到高指标,是一个难题。在焊接预置、载体开槽及打孔、夹具空隙等方面作了研究,使钎接率达到85%以上(一般可达90%)如载体金属打工艺孔,可使钎接率从40%~50%上升到90%。开槽可控制被焊接的位置,在电性能上获得了良好的效果。目前正在研究网格载体与电性能的关系,如获得突破,则钎透率问题就将最终获得解决。

4 讨论与实例

Al2O3— Al产品的实例,其技术指标如下:

工作频率 1200~1400MHz

组件尺寸 40mm×90mm

钎透率 90.28%

焊后变形 ≤0.01mm

接触电阻 ≤0.02Ω

插入损耗 ≤0.06db

串 扰 ≤0.1db

热循环次数 ≥45次

微波电路组装技术的研究,是一个电、结构及工艺的综合性课题。目前这项研究工作已应用于实践,共制作组件2000余件,并获得明显的技术和经济效益。

-

影响微波电路性能的要素研究2019-06-21 0

-

微波电路及设计的基础知识2009-08-24 0

-

【下载】《微波固态电路设计》2018-01-24 0

-

单片微波集成电路设计分析介绍2019-07-04 0

-

基于LTCC多微波无源滤波器研究设计2019-07-08 0

-

基于波导带通滤波器的计算微波电路的并行算法分析2019-07-10 0

-

基于微波频率的Vivaldi天线研究2019-07-17 0

-

微波电路射频设计2011-04-11 3029

-

微波电路引论-射频与应用设计_朱建清译2012-03-05 992

-

两种新型微波管慢波结构的高频特性仿真研究2013-01-22 648

-

微波暗室性能的低频三维电磁分析2020-12-21 594

-

微波拉远系统问题分析及解决思路2021-06-08 505

-

微波射频电路杂波干扰问题技术分析及改进研究2022-12-19 994

-

《微波工程基础》:微波技术的基本理论和基本分析方法2023-01-09 495

-

微波网络如何使用S参数来分析电路2023-10-31 209

全部0条评论

快来发表一下你的评论吧 !